#### Universidade Estadual de Campinas Instituto de Computação

## Isaías Bittencourt Felzmann

Architectural Support for Approximate Computing

Suporte Arquitetural para Computação Aproximada

#### Isaías Bittencourt Felzmann

## Architectural Support for Approximate Computing

#### Suporte Arquitetural para Computação Aproximada

Tese apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Doutor em Ciência da Computação.

Thesis presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Doctor in Computer Science.

Supervisor/Orientador: Prof. Dr. Lucas Francisco Wanner

Este exemplar corresponde à versão final da Tese defendida por Isaías Bittencourt Felzmann e orientada pelo Prof. Dr. Lucas Francisco Wanner.

#### Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Felzmann, Isaías Bittencourt, 1992-

F349a

Architectural support for approximate computing / Isaías Bittencourt Felzmann. - Campinas, SP: [s.n.], 2023.

Orientador: Lucas Francisco Wanner.

Tese (doutorado) - Universidade Estadual de Campinas, Instituto de Computação.

1. Computação aproximada. 2. Computação consciente de energia. 3. Arquitetura de computador. I. Wanner, Lucas Francisco, 1981-. II. Universidade Estadual de Campinas. Instituto de Computação. III. Título.

#### Informações Complementares

**Título em outro idioma:** Suporte arquitetural para computação aproximada

Palavras-chave em inglês:

Approximate computing Energy-aware computing Computer architecture

Área de concentração: Ciência da Computação Titulação: Doutor em Ciência da Computação

Banca examinadora:

Lucas Francisco Wanner [Orientador]

Jorge Castro-Godínez

Alfredo Goldman Vel Lejbman Guido Costa Souza de Araújo

Sandro Rigo

Data de defesa: 04-08-2023

Programa de Pós-Graduação: Ciência da Computação

- Identificação e informações acadêmicas do(a) aluno(a)

ORCID do autor: https://orcid.org/0000-0003-3048-8310

Currículo Lattes do autor: https://lattes.cnpq.br/3499341475094394

#### Universidade Estadual de Campinas Instituto de Computação

#### Isaías Bittencourt Felzmann

# Architectural Support for Approximate Computing Suporte Arquitetural para Computação Aproximada

#### Banca Examinadora:

- Prof. Dr. Lucas Francisco Wanner IC/UNICAMP

- Prof. Dr. Jorge Castro-Godínez TEC/Costa Rica

- Prof. Dr. Alfredo Goldman vel Lejbman IME/USP

- Prof. Dr. Guido Costa Souza de Araújo IC/UNICAMP

- Prof. Dr. Sandro Rigo IC/UNICAMP

A ata da defesa, assinada pelos membros da Comissão Examinadora, consta no SIGA/Sistema de Fluxo de Dissertação/Tese e na Secretaria do Programa da Unidade.

$To\ Andressa.$

## Acknowledgements

This work was directly supported by the São Paulo Research Foundation (FAPESP) grant #2018/24177-0. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author and do not necessarily reflect the views of the Foundation. This work received additional support from the National Council for Scientific and Technological Development – Brazil (CNPq), under grants 404261/2016-7, 438445/2018-0, and 402467/2021-3, and the Coordination for the Improvement of Higher Education Personnel – Brazil (CAPES), Finance Code 001.

This text contains significant text excerpts extracted, with permission, from Isaías Felzmann, João Fabrício Filho, and Lucas Wanner, *Risk-5: Controlled approximations for RISC-V*, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, November 2020 [46]. ©2020 IEEE.

This text contains significant text excerpts extracted, with permission, from Isaías Felzmann, João Fabrício Filho, Juliane Regina de Oliveira, and Lucas Wanner, Special Session: How much quality is enough quality? A case for acceptability in approximate designs, IEEE 39th International Conference on Computer Design (ICCD), October 2021 [45]. © 2021 IEEE.

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of University of Campinas's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights\_link.html to learn how to obtain a License from RightsLink.

This text contains significant text excerpts extracted from Isaías Felzmann, João Fabrício Filho, Lucas Wanner, AxPIKE: Instruction-level Injection and Evaluation of Approximate Computing, Design, Automation & Test in Europe Conference & Exhibition, February 2021 [47]. ©2021 EDAA.

## Resumo

A Computação Aproximada é uma metodologia que proporciona ganhos em eficiência energética ao relaxar requisitos de qualidade em aplicações resilientes. Várias técnicas de hardware, desenvolvidas sem vínculo com uma aplicação, têm potencial de proporcionar grandes benefícios em cenários favoráveis, mas a integração delas em uma arquitetura de propósito geral traz novos desafios para seu controle, tais como determinar, em tempo de execução, que regiões de aplicação se beneficiam de aproximações, que tipos de aproximações são essas, e até que ponto elas são vantajosas.

Nesta tese, apresentamos extensões para a arquitetura RISC-V que implementam mecanismos de controle para coordenar múltiplas técnicas de aproximação coexistentes no mesmo sistema. Através dessas extensões, as habilidades de um hardware de aproximação são expostas ao software por meio de registradores para identificação, estruturas de dados e drivers que descrevem a natureza e parâmetros de configuração para cada elemento do sistema aproximado. Isso permite que a pilha de software controle o que e quanto é aproximado em uma aplicação. As aproximações podem ser dinamicamente configuradas e combinadas em tempo de execução, ampliando os horizontes de exploração.

Para expor ao software os mecanismos de controle, nós também construímos uma interface em nível de software supervisório contendo uma camada de abstração e permitindo a coexistência de diferentes configurações de aproximação dentre as aplicações que compartilham o processador. Os elementos necessários para esse nível de controle foram implementados em dois níveis: um simulador em software e um protótipo sintetizado para FPGA, que possibilitaram uma demonstração da funcionalidade do sistema e estimativas de custo energético.

Nos nossos resultados, selecionamos aproximações para avaliação tanto no simulador como no protótipo em FPGA. Esses resultados destacam a necessidade de integração em nível de arquitetura de aproximações em hardware para melhor avaliação de como aplicações se comportam quando expostas a aproximação. Nesse sentido, esta tese propõe uma nova ferramenta que preenche a lacuna entre o software e hardware de aproximação, permitindo que desenvolvedores avaliem os benefícios e custos de técnicas de aproximação em um ambiente controlado e configurável.

## Abstract

Approximate Computing offers enhanced energy efficiency by exploring quality relaxation on resilient applications. Application-agnostic hardware-level techniques can provide high benefits under certain scenarios, but their integration on a general-purpose architecture presents novel control challenges, such as determining, at runtime, what application regions benefit from approximation, which approximations are favorable, and by how much.

In this thesis, we present extensions to the RISC-V architecture that implement control mechanisms to orchestrate multiple coexisting approximation techniques within an architecture. Through these extensions, approximate hardware capabilities are exposed to software through identification registers, data structures, and drivers that describe the nature and configuration parameters for each approximate design. Approximations may be configured and combined at runtime, allowing for simplified design space exploration.

To allow high-level software to take control of the approximate state of the system, we also built a supervisor-level software interface that provides the hardware abstraction layer of the approximation and supports the coexistence of different levels of reliability within applications that share the processor. The underlying hardware needed to support the control of approximations was implemented in two levels, a software simulator and a prototype synthesized for FPGA, which allowed the functional demonstration of the system and energy estimation. In our experiments, we selected approximations for evaluation both in the simulator and in the FPGA prototype.

Our results highlight the need for architectural integration of hardware approximations in order to provide an accurate evaluation of how applications behave when subjected to approximations. To this end, this thesis proposes a novel hardware-software framework that bridges the gap between software and hardware approximations, allowing designers to easily evaluate energy-quality trade-offs of approximation techniques in a controlled and configurable environment.

# List of Figures

| 1.1 | The role and contributions of this thesis                                   | 17    |

|-----|-----------------------------------------------------------------------------|-------|

| 4.1 | Structure of the Approximation Description Table                            | 40    |

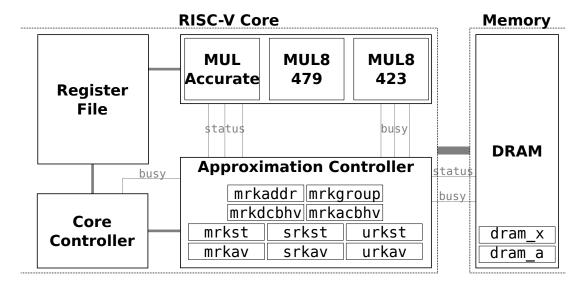

| 4.2 | Supporting hardware for the ISA extension                                   | 43    |

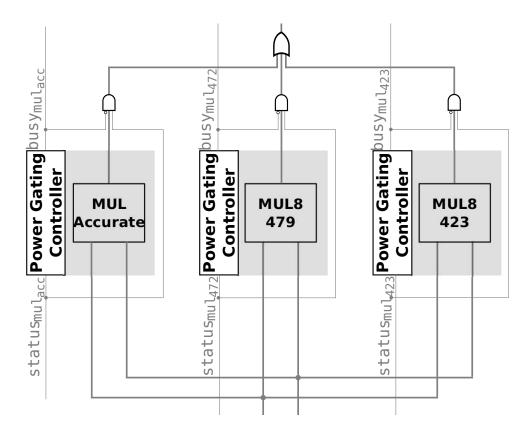

| 4.3 | Implementation of non-configurable multiplication hardware                  | 44    |

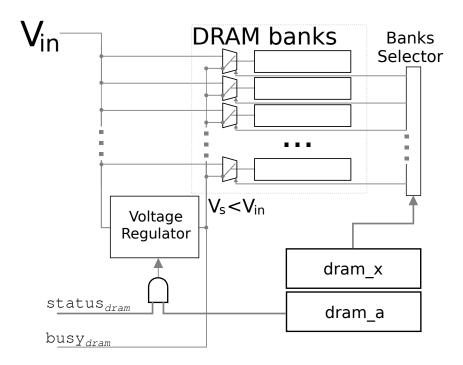

| 4.4 | Implementation of indirectly-configurable DRAM                              | 45    |

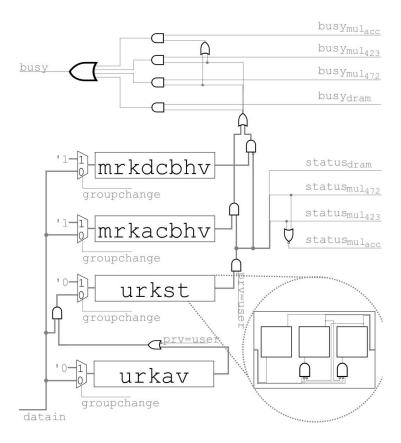

| 4.5 | Implementation of the approximation controller                              | 47    |

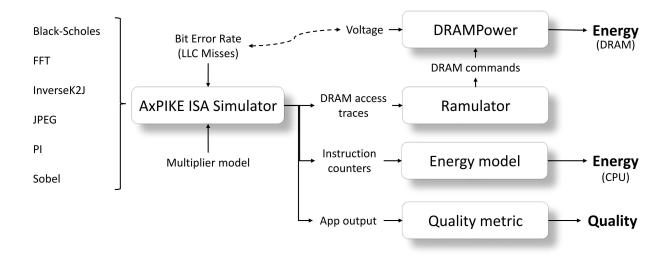

| 5.1 | Workflow of the simulation environment                                      | 54    |

| 5.2 | Sample approximation models                                                 | 55    |

| 5.3 | Sample approximation configuration                                          | 55    |

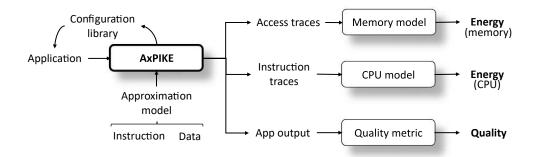

| 5.4 | AxPIKE control interface                                                    | 56    |

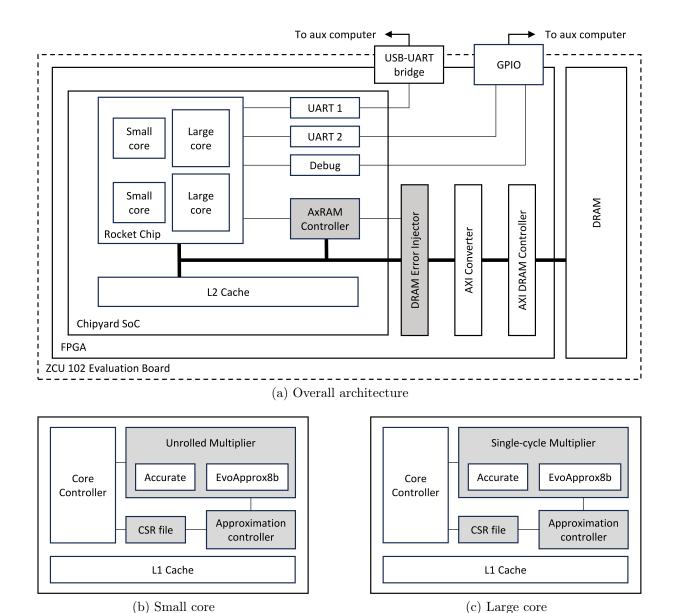

| 5.5 | Architecture of the hardware prototype                                      | 60    |

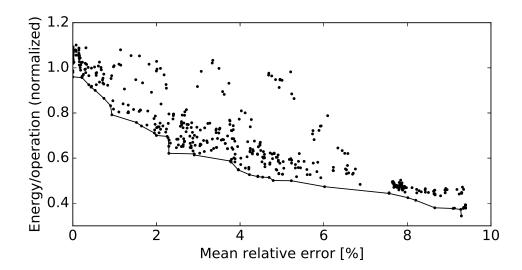

| 5.6 | Energy-quality trade-off individual EvoApprox8b multipliers                 | 63    |

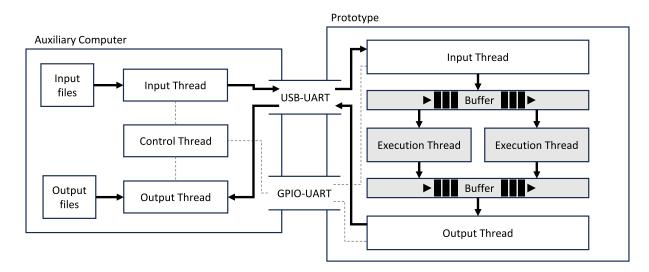

| 5.7 | Software to support the hardware prototype                                  | 67    |

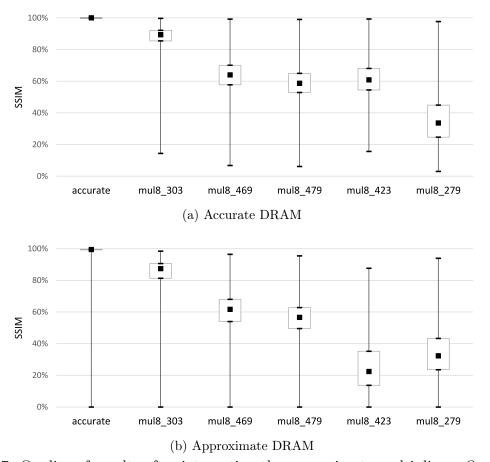

| 6.1 | Demonstration experiments in the simulation environment                     | 69    |

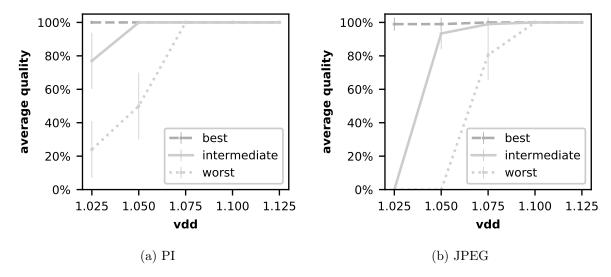

| 6.2 | Output quality of applications using the approximate DRAM                   | 70    |

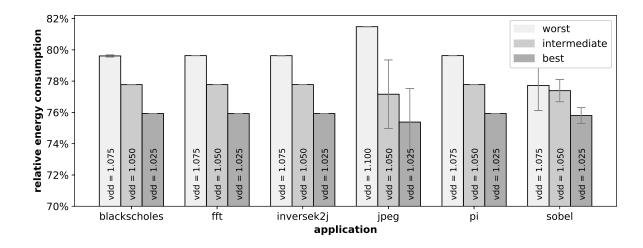

| 6.3 | Energy to achieve 90% quality on approximate DRAM                           | 71    |

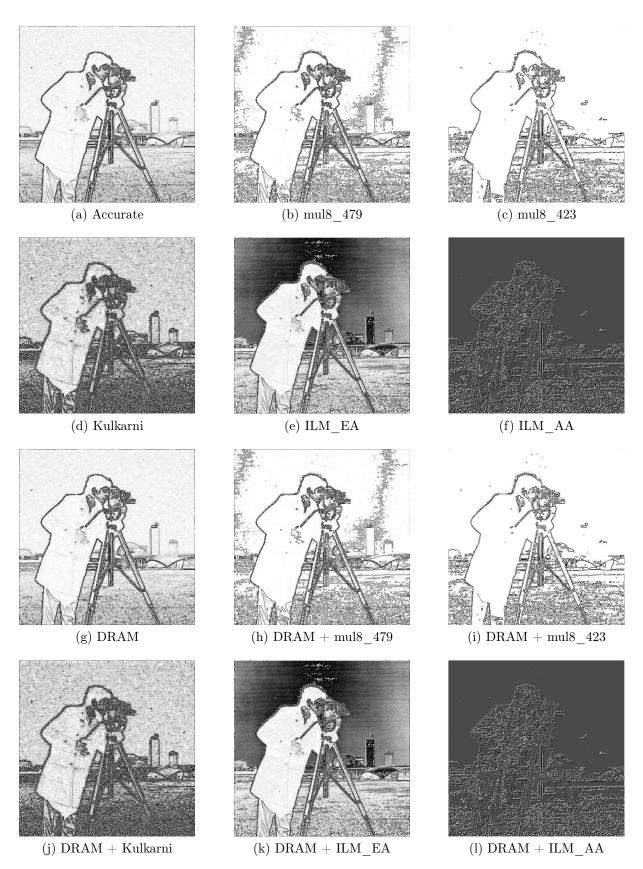

| 6.4 | Sobel execution using approximate DRAM and multipliers                      | 73    |

| 6.5 | Quality distribution on approximate DRAM                                    | 76    |

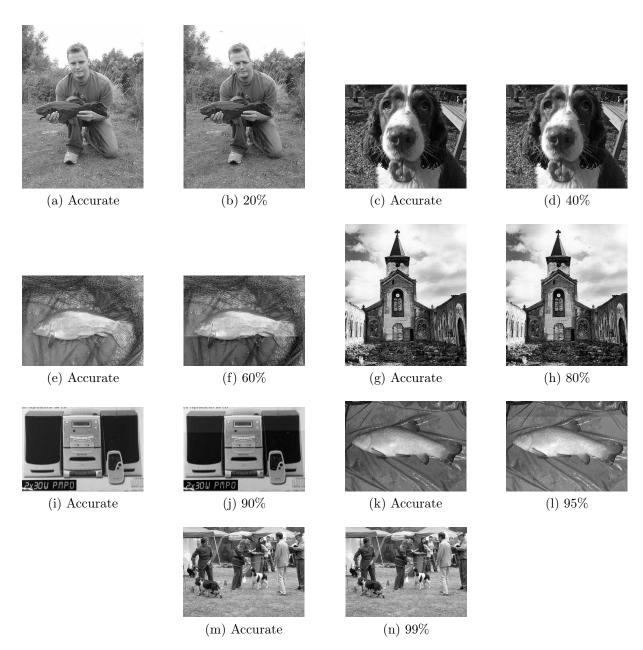

| 6.6 | Sample images at given quality thresholds                                   | 77    |

| 6.7 | Quality of results after integrating the approximate multipliers            | 78    |

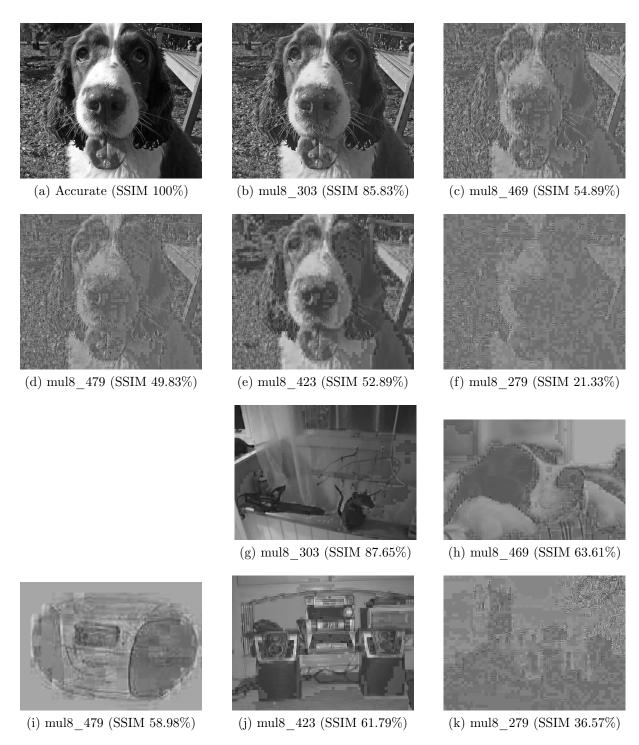

| 6.8 | Sample images illustrating outputs of approximate multiplication            | 80    |

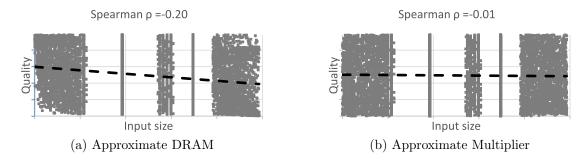

| 6.9 | Correlation test between input size and quality of results                  | 81    |

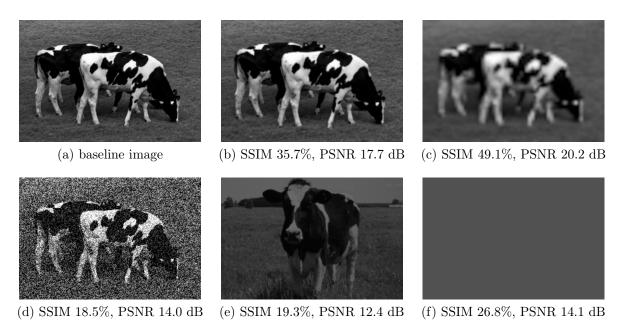

| 7.1 | Effect of morphological changes and noise injection in the quality metric . | 85    |

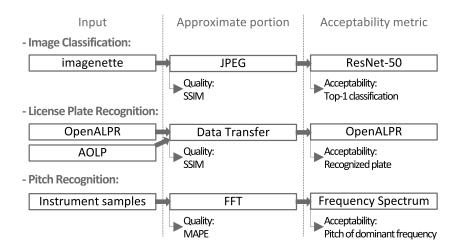

| 7.2 | Our proposed approach to evaluate the acceptability of results              | 86    |

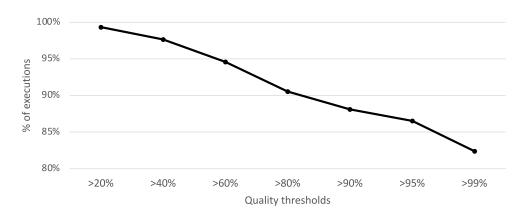

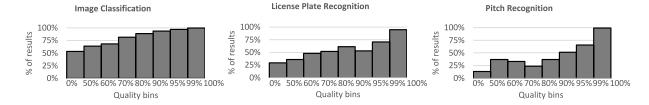

| 7.3 | Percentage of results that are acceptable within bins delimited by quality  | 00    |

| 1.5 | thresholds                                                                  | 87    |

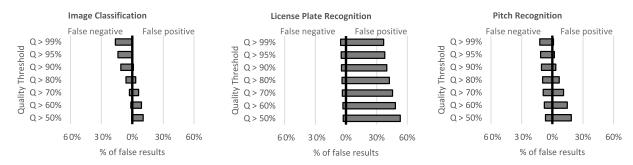

| 7.4 | False positives or negatives: percentage of unacceptable or acceptable re-  | 01    |

| 1.4 | sults that are wrongfully classified using quality thresholds only          | 87    |

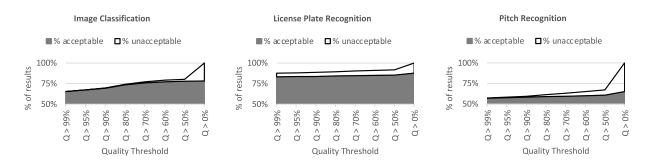

| 7.5 | Percentage of acceptable and unacceptable results with quality above pre-   | 01    |

| 7.5 | determined thresholds                                                       | 88    |

|     | determined intesholds                                                       | _ ^ ^ |

# List of Tables

| 1.1        | List of authored publications related to this thesis                         | 21 |

|------------|------------------------------------------------------------------------------|----|

| 3.1        | Qualitative classification of related work and comparison with this thesis . | 27 |

| 4.1        | CSRs defined in Risk-5                                                       | 38 |

| 5.1<br>5.2 | Statistics collected for Matrix Multiply                                     | 57 |

|            | proximation                                                                  | 58 |

| 5.3        | Comparison of simulation performance under different configurations          | 58 |

| 5.4        | Resource utilization of FPGA Baseline implementation                         | 61 |

| 5.5        | Selected EvoApprox8b multipliers                                             | 63 |

| 5.6        | Overhead introduced in the FPGA implementation                               | 65 |

| 5.7        | Software tools in the prototype framework                                    |    |

| 6.1        | Regression of error rates in the DRAM approximation scenario                 | 70 |

## Glossary

This is a non-exhaustive list of terms and acronyms used in this thesis. The provided definitions are not intended to be broad, but to reflect the meaning in the scope of this thesis, as a reference for the reader.

6T-SRAM 6T Static Random Access Memory. The typical SRAM cell made of 6

transistors.

ALU Arithmetic and Logic Unit. The part of the processor that computes

arithmetic and logic functions.

AMBA AXI4 Advanced Microcontroller Bus Architecture (AMBA) Advanced eXten-

sible Interface (AXI). The fourth generation of a royalty-free on-chip

communication bus protocol developed by ARM.

ARCS International Conference on Architecture of Computing Systems. An

international scientific event.

ARM Advanced RISC Machine. Both a family of ISAs and the company that

develops it.

Arty A7-100T A development board based on a Xilinx Artix-7 FPGA.

AXI See AMBA AXI4.

AxPIKE Our in-house functional simulator for Approximate Computing.

AxRAM Our in-house data access interface for approximate memories.

CPU Central Processing Unit. The main processor in a computing system.

CSR Control and Status Registers. The registers that control and store in-

formation about the CPU in a RISC-V architecture.

DATE Design, Automation and Test in Europe. An international scientific

event.

DDR4 Double Data Rate SDRAM. The fourth generation of the most common

class of DRAM.

DMA Direct Memory Access. A method that allows a peripheral device to

communicate data directly with the main memory.

DRAM Dynamic Random Access Memory. A type of random access memory

typically used as main memory.

DSP Digital Signal Processing (slice). An internal structure in an FPGA.

DVFS Dynamic Voltage-Frequency Scaling. A mainstream energy-saving tech-

nique that adjusts voltage and frequency on demand.

EDAA European Design and Automation Association. A scientific association.

ELF Executable and Linkable Format. A common standard for executable

files in Linux.

ERAD-SP Escola Regional de Alto Desempenho de São Paulo. A regional academic

event held in São Paulo.

EvoApprox8b A library of approximate integer multipliers and adders.

FFT Fast Fourier Transform. An algorithm that calculates the discrete form

of the Fourier Transform.

FGCS Future Generation Computer Systems. A scientific journal published by

Elsevier.

FPGA Field Programmable Gate Array. A hardware device designed to be

reconfigured after manufacturing, representing different logic circuits.

FPU Floating-Point Unit. The part of a processor that computes arithmetic

with real numbers (Floating-Point representation).

GPIO General-Purpose Input/Output. An I/O interface for general purposes.

I/O Input/Output. One of the main functions of a computer.

ICCD International Conference on Computer Design. An international scien-

tific event.

IEEE Institute of Electrical and Electronics Engineers. A professional associ-

ation.

Internet of Things. A network of small connected devices and sensors.

IP Intelectual Property. The proprietary designs by a given company.

ISA Instruction Set Architecture. The interface between hardware and soft-

ware implemented by a processor.

JEDEC Joint Electron Device Engineering Council. An independent standard-

ization body.

JPEG An algorithm for lossy image compression.

JTAG The industry standard interface for design verification.

L1, L2 Level 1/2 Cache. The first/second level of cache memory.

Linux A reference to a given Operating System based on the Linux kernel.

LLC Last Level of Cache. The last level of cache memory, from which misses

are then fetched from the main memory.

LUT Lookup Table. An internal structure in an FPGA.

MMIO Memory-mapped Input/Output. A technique that maps communication

with peripherals as memory-like accesses.

OS Operating System. A collection of software that manages computer

hardware resources and provides common services for other programs.

RAM Random Access Memory. A memory that can be accessed at any order.

RISC-V An open-standard ISA.

Risk-5 Our ISA extension to support approximation.

Rocket Chip A processor implementation based on the RISC-V architecture.

RTL Register-transfer level. A design abstraction that models digital circuits

in terms of the flow of data.

RV64g A subset of the RISC-V ISA.

SBAC-PAD International Symposium on Computer Architecture and High Perfor-

mance Computer. An international scientific event.

SBESC Brazilian Symposium on Computing Systems Engineering. A national

scientific event held in Brazil.

SDRAM Synchronous Dynamic Random Access Memory. See DRAM.

Sobel An algorithm to identify borders in an image.

SSIM Structural Similarity Index Metric. A metric that computes the simi-

larity between two images.

SUSCOM Sustainable Computing: Informatics and Systems. A scientific journal

published by Elsevier.

TCAD Transactions on Computer-Aided Design of Integrated Circuits and Cir-

cuits. A journal published by IEEE.

TLB Translation Lookaside Buffer. A part of the virtual memory translation

system that caches page table entries.

UART Universal Asynchronous Receiver/Transmitter. A protocol for asyn-

chronous serial communication.

USB Universal Serial Bus. An industry standard for serial communication.

WSCAD Simpósio em Sistemas Computacionais de Alto Desempenho. A na-

tional scientific event held in Brazil.

ZCU102 A development board based on a Xilinx FPGA.

## Contents

| 1 | Intr                         | roduction: An architecture for Approximate Computing             | 16                         |

|---|------------------------------|------------------------------------------------------------------|----------------------------|

| 2 | <b>Bac</b> 2.1               | Configurability of hardware-level approximations                 | 22<br>23<br>23<br>24<br>25 |

| 3 | Rel                          | ated work: Interfacing hardware approximations and software      | 26                         |

|   | 3.1                          | · · · · · · · · · · · · · · · · · · ·                            | 29                         |

|   | 3.2                          |                                                                  | 31                         |

|   | 3.3                          |                                                                  | 32                         |

|   | 3.4                          | The design choices that led to this thesis                       | 35                         |

| 4 | $\operatorname{Int}\epsilon$ | egrating Approximate Computing: Architecture-level specification | 37                         |

|   | 4.1                          |                                                                  | 37                         |

|   |                              | 11                                                               | 38                         |

|   |                              |                                                                  | 39                         |

|   |                              |                                                                  | 40                         |

|   |                              | 4.1.4 Approximation status and control                           | 41                         |

|   |                              | 4.1.5 Activation/Deactivation behavior                           | 41                         |

|   |                              |                                                                  | 42                         |

|   |                              | 4.1.7 Interaction in multicore architectures                     | 42                         |

|   | 4.2                          | Hardware support                                                 | 42                         |

|   |                              |                                                                  | 43                         |

|   |                              | 0 11                                                             | 45                         |

|   |                              | 1 1                                                              | 46                         |

|   | 4.3                          |                                                                  | 48                         |

|   |                              | 11                                                               | 48                         |

|   |                              | 4.3.2 Approximation coherence of shared resources                | 49                         |

| 5 | Imp                          | plementation: Simulated behavior and FPGA prototype              | 51                         |

|   | 5.1                          |                                                                  | 52                         |

|   |                              |                                                                  | 53                         |

|   |                              |                                                                  | 53                         |

|   |                              | 5.1.2.1 Approximation Modeling and Injection                     | 54                         |

|   |                              | 5.1.2.2 Software Control Interface                               | 56                         |

|   |                              | 5.1.2.3 Statistics generator                                     | 57                         |

|   |                              | 5.1.3 A sample usage case                                        | 58                         |

| 5.2.1 Hardware Workflow 5.2.1.1 Base ZCU102 Support 5.2.1.2 Approximation controller 5.2.1.3 Approximate Multipliers 5.2.1.4 DRAM Error Injector 5.2.1.5 Area overhead 5.2.2 Software Framework  6 Experimentation: Evaluating the Approximate Computing integ 6.1 Experiments on the simulation environment 6.1.1 Configurable approximate DRAM 6.1.2 Non-configurable approximate multipliers 6.2 Experiments on the hardware prototype 6.2.1 Evaluating the Approximate DRAM operating point 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size  7 A case for acceptability: Is quality enough? 7.1 Quality evaluation of Approximate Systems 7.2 Analyzing Acceptability of Application Output 7.3 Results: Quality vs Acceptability  8 Conclusions: Architectural support and future directions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59         |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

| 5.2.1.2 Approximation controller 5.2.1.3 Approximate Multipliers 5.2.1.4 DRAM Error Injector 5.2.1.5 Area overhead 5.2.2 Software Framework  6 Experimentation: Evaluating the Approximate Computing integendation of the simulation environment 6.1.1 Configurable approximate DRAM 6.1.2 Non-configurable approximate multipliers 6.2 Experiments on the hardware prototype 6.2.1 Evaluating the Approximate DRAM operating point 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size  7 A case for acceptability: Is quality enough? 7.1 Quality evaluation of Approximate Systems 7.2 Analyzing Acceptability of Application Output 7.3 Results: Quality vs Acceptability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60         |  |  |  |  |  |

| 5.2.1.2 Approximation controller 5.2.1.3 Approximate Multipliers 5.2.1.4 DRAM Error Injector 5.2.1.5 Area overhead 5.2.2 Software Framework  6 Experimentation: Evaluating the Approximate Computing integendation of the simulation environment 6.1.1 Configurable approximate DRAM 6.1.2 Non-configurable approximate multipliers 6.2 Experiments on the hardware prototype 6.2.1 Evaluating the Approximate DRAM operating point 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size  7 A case for acceptability: Is quality enough? 7.1 Quality evaluation of Approximate Systems 7.2 Analyzing Acceptability of Application Output 7.3 Results: Quality vs Acceptability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61         |  |  |  |  |  |

| 5.2.1.4 DRAM Error Injector 5.2.1.5 Area overhead 5.2.2 Software Framework  6 Experimentation: Evaluating the Approximate Computing integ 6.1 Experiments on the simulation environment 6.1.1 Configurable approximate DRAM 6.1.2 Non-configurable approximate multipliers 6.2 Experiments on the hardware prototype 6.2.1 Evaluating the Approximate DRAM operating point 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size  7 A case for acceptability: Is quality enough? 7.1 Quality evaluation of Approximate Systems 7.2 Analyzing Acceptability of Application Output 7.3 Results: Quality vs Acceptability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |

| 5.2.1.5 Area overhead 5.2.2 Software Framework  6 Experimentation: Evaluating the Approximate Computing integengence of the simulation environment 6.1.1 Configurable approximate DRAM 6.1.2 Non-configurable approximate multipliers 6.2 Experiments on the hardware prototype 6.2.1 Evaluating the Approximate DRAM operating point 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size  7 A case for acceptability: Is quality enough? 7.1 Quality evaluation of Approximate Systems 7.2 Analyzing Acceptability of Application Output 7.3 Results: Quality vs Acceptability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62         |  |  |  |  |  |

| 5.2.2 Software Framework  6 Experimentation: Evaluating the Approximate Computing integendant of the simulation environment and the simulation of the simulation environment and the simul | 64         |  |  |  |  |  |

| 6.1 Experiments on the simulation environment 6.1.1 Configurable approximate DRAM 6.1.2 Non-configurable approximate multipliers 6.2 Experiments on the hardware prototype 6.2.1 Evaluating the Approximate DRAM operating point 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size 7 A case for acceptability: Is quality enough? 7.1 Quality evaluation of Approximate Systems 7.2 Analyzing Acceptability of Application Output 7.3 Results: Quality vs Acceptability 7.4 Consequence of the Approximate Systems 7.5 Analyzing Acceptability of Application Output 7.6 Results: Quality vs Acceptability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |  |  |  |  |  |

| 6.1 Experiments on the simulation environment 6.1.1 Configurable approximate DRAM 6.1.2 Non-configurable approximate multipliers 6.2 Experiments on the hardware prototype 6.2.1 Evaluating the Approximate DRAM operating point 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size 7.1 Quality evaluation of Approximate Systems 7.2 Analyzing Acceptability of Application Output 7.3 Results: Quality vs Acceptability 7.4 Case for acceptability of Application Output 7.5 Results: Quality vs Acceptability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66         |  |  |  |  |  |

| 6.1.1 Configurable approximate DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | gration 68 |  |  |  |  |  |

| 6.1.2 Non-configurable approximate multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68         |  |  |  |  |  |

| 6.2 Experiments on the hardware prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69         |  |  |  |  |  |

| 6.2.1 Evaluating the Approximate DRAM operating point 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72         |  |  |  |  |  |

| 6.2.2 Integrating the Approximate Multipliers 6.2.3 The impact of scaling input size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75         |  |  |  |  |  |

| 6.2.3 The impact of scaling input size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76         |  |  |  |  |  |

| 7 A case for acceptability: Is quality enough? 7.1 Quality evaluation of Approximate Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78         |  |  |  |  |  |

| 7.1 Quality evaluation of Approximate Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81         |  |  |  |  |  |

| 7.1 Quality evaluation of Approximate Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83         |  |  |  |  |  |

| 7.2 Analyzing Acceptability of Application Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84         |  |  |  |  |  |

| 7.3 Results: Quality vs Acceptability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |

| 8 Conclusions: Architectural support and future directions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89         |  |  |  |  |  |

| Bibliography 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |  |  |  |  |  |

## Chapter 1

## Introduction

## An architecture for Approximate Computing

In modern computing systems, power dissipation and energy efficiency are important factors to take into consideration in the design process. It is not uncommon to find these limiting scalability, as performance requirements may not be sustainable in the long run [68,140]. Approximate Computing has emerged as a design methodology to answer the computing systems' ever-increasing need for energy efficiency. This methodology explores the exposition of intermediary processing steps to minor deviations that do not affect the final result in a significant way for many computing domains. When the applications are resilient to some accuracy degradation, allowing approximate results can potentially lead to significant energy savings. These led to multiple software- and hardware-level approximation techniques to explore this energy-quality trade-off [6, 83, 91].

These approximation techniques, by themselves, are just a different way to perform a given operation. They need to be applied in solving a computing problem, on a target scenario, to achieve their expected energy-quality trade-off. This requires that the approximations are integrated into an application. Since software-level approximations are designed to be part of an application, this integration is resolved at design time. Loop perforation [125], for example, modifies the implementation of loops to skip iterations to save computation time and energy and, therefore, is integrated within an application at design time. Hardware-level techniques, on the other hand, require an architectural interface to support the execution of a full application stack. An approximate arithmetic unit [96] would require a coexistent accurate counterpart to support the execution of non-resilient code segments, imposing overheads and adding control requirements. Existing hardware techniques, however, typically lack this level of architectural integration.

Approximation-hardware units are usually built as standalone units that introduce some level of imprecision at design time, or designed to offer some level of controllability, either directly or by adjusting some external parameter [6,91]. In this thesis, these are refered as nonconfigurable, directly-configurable, and indirectly-configurable approximation units, respectively. Any of the approaches cause overhead at the architecture level, such as the need for replicated units to support non-resilient application segments, additional hardware to provide controllability or error recovery, or circuitry to allow operating parameters to be adjusted and to coexist. Approximation-hardware designs are, however,

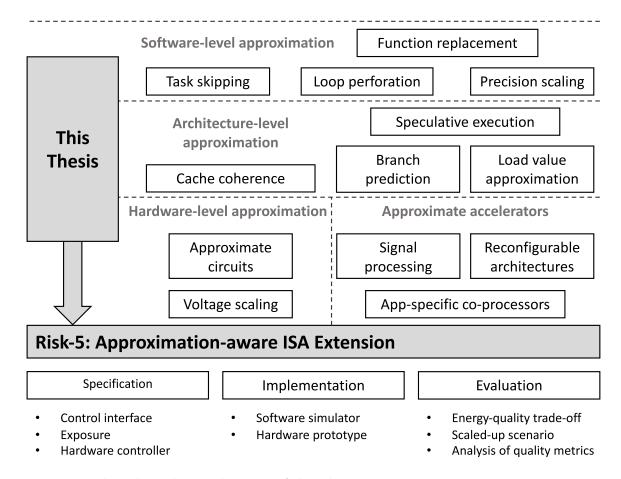

Figure 1.1: The role and contributions of this thesis. We propose an approximation-aware ISA extension to integrate approximate hardware in the general-purpose scenario.

usually demonstrated and evaluated in isolation, applied to specific application-level constructions, with limited or no discussion of the architecture-level integration with other hardware components in an actual processor.

Individual approximate multiplication units, for example, can report energy savings in the range of tens and up to 80%, in comparison to their accurate counterparts, with limited impact on expected error per operation [8,77,96]. These results, however, are oftentimes obtained in very limited scenarios based on mathematical modeling and software simulation of the multiplier alone, applied over synthetic workloads or case studies that profit from the multipliers at their best. Multipliers do not live alone in a general-purpose processor. They are just a part of the design, even if a significantly costly one [144]. Also, they may not be sized and optimized as demonstrated for their approximate designs and represent just a fraction of the instructions executed in a typical application. By taking these factors into consideration, we show that energy savings can be reduced to modest single-digit values at a significantly higher quality impact compared to other classes of approximation [46,49]. Thus, the lack of architecture-level considerations when analyzing and demonstrating approximation hardware results can potentially leave energy savings figures overestimated.

Figure 1.1 shows where this thesis is inserted in the Approximate Computing stack and summarizes its contributions. We study approximation techniques and approximate

architectures to answer whether and how approximation-hardware modules can be applied to general-purpose computing. The architecture-level integration is determinant in this scenario, and this requires an adequate hardware-software interface to recognize, expose, and control the approximation capabilities: recognize what kind of approximation is available and how to use it, expose it to the software application or supervisor so that they can evaluate whether they can profit from it, and control where and when the approximation should be employed as determined by the software.

Previous work has shown the potential of integrating approximations into architecture design [25–27,53,63,93,99] and proposed generic interfaces to control approximations and account for execution resilience [28, 31, 48, 49, 81, 114, 134]. These integration alternatives are, however, usually applied only to a limited number of specific approximation scenarios, and the generic control is mostly focused on the software controller, not reflecting a wide range of available approximation techniques. The differences in the behavior of applications when subjected to approximations [25, 44] require a control interface to be designed using a more approximation-centered approach, while still leaving enough links with the software for reliable execution. Existing integrated hardware-software alternative interfaces, however, are not focused on a general-purpose scenario, have limited compatibility with existing approximation techniques, underestimate control overhead, or are applied directly to the application, in a scenario not compliant with modern multiprocess and multi-application computing controlled by a supervisor system [6, 29]. Thus, how to orchestrate multiple coexisting hardware approximation techniques in a generalpurpose processor is a question that has not yet been fully answered [83]. Since different applications have different levels of compatibility with different approximations, managing coexisting techniques is essential to apply Approximate Computing into compatible applications in a general-purpose scenario.

This thesis advances into the ability to provide approximation control by proposing and demonstrating Risk-5 [46], an ISA extension that provides a hardware-software interface, based on RISC-V, to coordinate multiple hardware-level approximation techniques within an architecture. In Risk-5, each approximation technique is integrated within the processor as a dedicated controllable module that can be activated or deactivated at execution time as instructed by a set of standardized control registers. The main contributions of this thesis are:

- the architecture-level specification of the Risk-5 extension and interface, discussing how it manages and integrates approximation techniques,

- the definition of a hardware controller that allows applications and operating systems to manage different degrees of approximation,

- the definition of a software interface for the applications to communicate with the operating system and underlying hardware to recognize and configure the approximation capabilities of the system, and

- a scaled-up exploration and demonstration of approximation techniques and target applications, identifying computing scenarios that can benefit from hardware approximation and how they behave when scaled to larger requirements.

Furthermore, to demonstrate the capabilities of the proposed control interface and the applicability of hardware approximation in a general-purpose processor, this thesis incorporates two different levels of implementation as technical contributions. At the simulation level, we developed AxPIKE, an instruction-level simulator that introduces versatility in representing approximate systems allowing designers to quickly model and evaluate their approximation concepts. Based on the demonstration performed on AxPIKE, we show how our control interface can allow the reliable and energy-efficient execution of applications on a general-purpose system employing approximation in two architectural resources: the memory hierarchy [37, 38] and the multiplication operation [8, 77, 96].