#### Universidade Estadual de Campinas Instituto de Computação

#### Rafael Junio da Cruz

Rowhammer-based fault injection and its effects on aged memories

Ataques de injeção baseados em Rowhammer e seus efeitos em memórias envelhecidas

#### Rafael Junio da Cruz

## Rowhammer-based fault injection and its effects on aged memories

## Ataques de injeção baseados em Rowhammer e seus efeitos em memórias envelhecidas

Dissertação apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação.

Dissertation presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Master in Computer Science.

Supervisor/Orientador: Prof. Dr. Diego de Freitas Aranha Co-supervisor/Coorientador: Prof. Dr. Rodolfo Jardim de Azevedo

Este exemplar corresponde à versão final da Dissertação defendida por Rafael Junio da Cruz e orientada pelo Prof. Dr. Diego de Freitas Aranha.

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Cruz, Rafael Junio da, 1990-

C889r

Rowhammer-based fault injection and its effects on aged memories / Rafael Junio da Cruz. – Campinas, SP: [s.n.], 2023.

Orientador: Diego de Freitas Aranha. Coorientador: Rodolfo Jardim de Azevedo.

Dissertação (mestrado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Criptografia. 2. Criptografia de chaves públicas. 3. Curvas elípticas. 4. Bitcoin. I. Aranha, Diego de Freitas, 1982-. II. Azevedo, Rodolfo Jardim de, 1974-. III. Universidade Estadual de Campinas. Instituto de Computação. IV. Título.

#### Informações Complementares

**Título em outro idioma:** Ataques de injeção baseados em Rowhammer e seus efeitos em memórias envelhecidas

#### Palavras-chave em inglês:

Cryptography

Public key cryptography

Elliptic curves

Bitcoin

**Área de concentração:** Ciência da Computação **Titulação:** Mestre em Ciência da Computação

Banca examinadora:

Diego de Freitas Aranha [Orientador]

Bruno de Carvalho Albertini Julio César López Hernández **Data de defesa:** 16-10-2023

Programa de Pós-Graduação: Ciência da Computação

Identificação e informações acadêmicas do(a) aluno(a)

<sup>-</sup> ORCID do autor: https://orcid.org/0009-0002-8789-7174

<sup>-</sup> Currículo Lattes do autor: http://lattes.cnpq.br/6803837483695062

#### Universidade Estadual de Campinas Instituto de Computação

#### Rafael Junio da Cruz

## Rowhammer-based fault injection and its effects on aged memories

Ataques de injeção baseados em Rowhammer e seus efeitos em memórias envelhecidas

#### Banca Examinadora:

- Prof. Dr. Diego de Freitas Aranha (Supervisor) Institute of Computing of the University of Campinas

- Prof. Dr. Julio César López Hernández Institute of Computing of the University of Campinas

- Prof. Dr. Bruno de Carvalho Albertini Polytechnic School of the University of Sao Paulo

A ata da defesa, assinada pelos membros da Comissão Examinadora, consta no SIGA/Sistema de Fluxo de Dissertação/Tese e na Secretaria do Programa da Unidade.

Campinas, 16 de outubro de 2023

## Dedicatória

Dedico este trabalho a todas as pessoas que me ensinaram durante minha vida. Meu vô Valdecir que foi o pai que nunca tive, minha vó Maria que ensinou como ser bom, minha mãe Cidinha que ensinou resiliência. Professores que auxiliaram no meu crescimento intelectual durante toda minha vida acadêmica, como o Prof. Pedro Rezende que ensinou ser firme nas afirmações através de referências ou provas matemáticas, como Prof. Rodolfo Azevedo que ensinou a responder perguntas com outras perguntas e que a maioria das vezes a repostas a uma pergunta é depende, como Prof. Diego Aranha que foi meu grande mentor. Durante minha vida profissional com ensinamentos de gerentes como Nelson Uto que tornou um professional e um ser humano melhor.

## Acknowledgements

Thank you, Intel<sup>®</sup>, for financing and investing in almost everything of my master's research.

This study was financed in part by the *Coordenação de Aperfeiçoamento de Pessoal de Nível Superior* - Brasil (CAPES) - Finance Code 001.

Thank you, Dr. Lois Orosa, Prof. Dr. Lucas Wanner, and Prof. Dr. Newton Frateschi for supporting with knowledge in the DRAM aging research.

Thank you, Samsung Electronics®, for give me time to write this work.

### Resumo

Bitcoin é a criptomoeda mais famosa mundialmente devido ao seu alto valor especulativo e uso descentralizado, dispensando a existência de agentes centralizados como, por exemplo, instituições financeiras. O protocolo da Bitcoin adota a curva elíptica secp256k1, haja vista o seu alto desempenho. Entretanto, a curva secp256k1 é reconhecida como fraca por não conseguir prover computações simples, eficientes e seguras ao mesmo tempo, além de conter curvas irmãs, twists, consideradas inseguras, podendo tornar o protocolo suscetível a ataques de curva inválida. Apesar de difícil execução, ataques de injeção de falhas são muito poderosos pois, em sua maioria, podem explorar aspectos difíceis de serem controlados remotamente como, por exemplo, temperatura, voltagem e frequência. Dentre os ataques de injeção de falhas está o Rowhammer, um ataque via software que afeta diretamente a memória DRAM, invertendo bits devido a uma grande quantidade de leituras consecutivas. Neste trabalho, o Rowhammer foi utilizado para injetar falhas na implementação da curva adotada pela Bitcoin, visando a subversão do protocolo e a extração da chave privada. Além disso, observou-se que o ataque proposto é capaz de afetar outras curvas elípticas e demais protocolos que utilizam o Algoritmo de Assinatura Digital de Curvas Elípticas (ECDSA). Por fim, conjectura-se que a idade ou o tempo de uso possa induzir problemas em memórias DRAM que permitam ataques de Rowhammer. Nessa direção, iniciou-se um estudo de envelhecimento artificial de memórias DRAM através do aquecimento usando resistências e alterações de voltagem através da placamãe. As resistências possibilitaram experimentos com temperaturas acima de 200°C. Como resultado, percebeu-se a existência de uma faixa de operação segura para a memória DRAM. Falhas de leitura ou escrita puderam ser observadas a partir de uma determinada temperatura e voltagem. Além disso, encontrou-se um limiar máximo de temperatura e voltagem, a partir do qual a memória tornava-se inoperante.

### Abstract

Bitcoin is the most famous worldwide cryptocurrency due to its high speculative value and decentralized use, avoiding the need for centralized agents as financial institutions. The Bitcoin protocol adopts the secp256k1 elliptic curve because of its high performance. However, secp256k1 is known to be a weak curve due to not provide a simple, efficient and secure computing at same time, in addition to containing unsafe twists, making the protocol susceptible to invalid curve attacks. Despite their complex execution, fault-injection attacks are powerful as most exploit aspects hard of being controlled remotely, such as temperature, voltage, frequency, and others. Among these attacks, Rowhammer is a software attack that directly affects the DRAM memory by inverting bits via many subsequent reads. In this work, we used Rowhammer to inject flaws in the implementation of curve within Bitcoin, aiming to subvert the protocol and extract the private key. However, we observed that the proposed attack could also affect other curves and protocols that use the Elliptic Curve Digital Signature Algorithm (ECDSA). Finally, we conjecture that age or time of use may introduce vulnerabilities in DRAM memories that allow Rowhammer attacks. In this direction, we started exploring the artificial aging of DRAM memories by heating, using resistors, and regulating the voltage in the motherboard. The resistors allowed experiments with temperatures above 200°C. As a result, we obtained a secure operating threshold for DRAM memories. Thus, read or write failures were observed above a specific temperature and voltage. Moreover, we found a maximum threshold for temperature and voltage, above which the memory became inoperative.

## List of Figures

| 1.1 | Security pyramid model of fault injection                              | 18 |

|-----|------------------------------------------------------------------------|----|

| 2.1 | Symmetric system                                                       | 22 |

| 2.2 | Asymmetric system                                                      |    |

| 2.3 | Elliptic curves example                                                |    |

| 2.4 | Elliptic curve operations in $\mathbb{R}$                              |    |

| 2.5 | Elliptic curve operations in $\mathbb{F}_{43}$                         |    |

| 2.6 | Elliptic curves' composition of subgroups                              |    |

| 2.7 | NATO soldiers                                                          |    |

| 3.1 | Memory capacity growth through the years                               | 38 |

| 3.2 | Memory cells                                                           | 40 |

| 3.3 | Scaling of DRAM capacitors                                             | 41 |

| 3.4 | Memory subsystem                                                       | 41 |

| 3.5 | High level overview of a memory bank                                   | 43 |

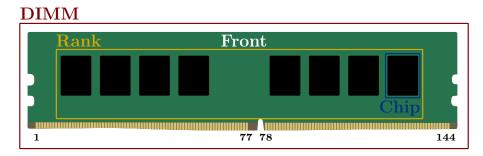

| 3.6 | Memory DIMM                                                            | 44 |

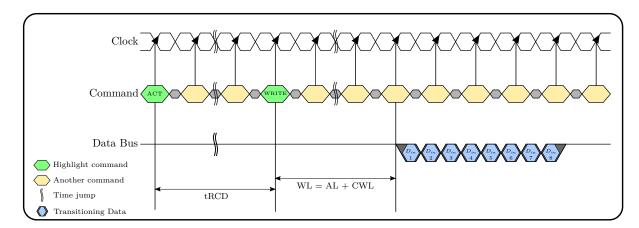

| 3.7 | Memory controller write and precharge commands                         | 48 |

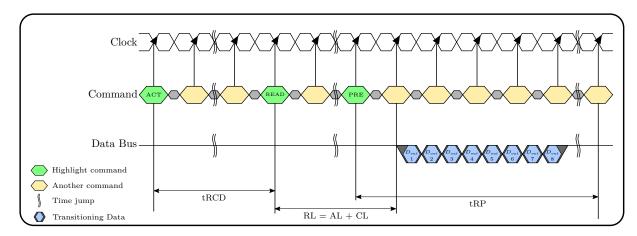

| 3.8 | Memory controller during a read command                                | 48 |

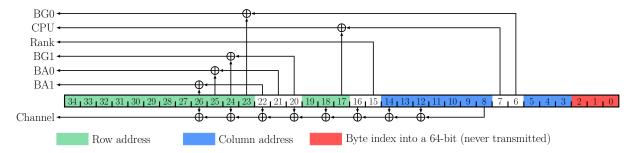

| 3.9 | Memory mapping from physical address to memory location                | 49 |

| 4.1 | Rowhammer types                                                        | 55 |

| 4.2 | Step-by-step Rowhammer attack                                          |    |

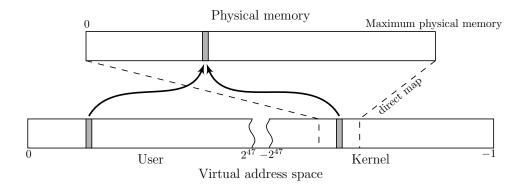

| 4.3 | Mapping physical memory using Prefetch Attack                          |    |

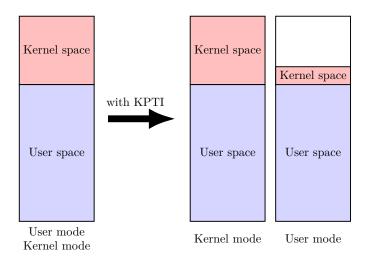

| 4.4 | Kernel Page-Table Isolation                                            | 58 |

| 4.5 | Page deduplication                                                     | 59 |

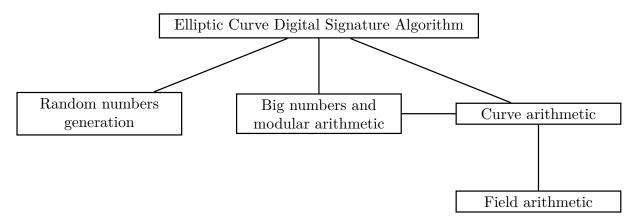

| 5.1 | ECDSA support modules                                                  | 64 |

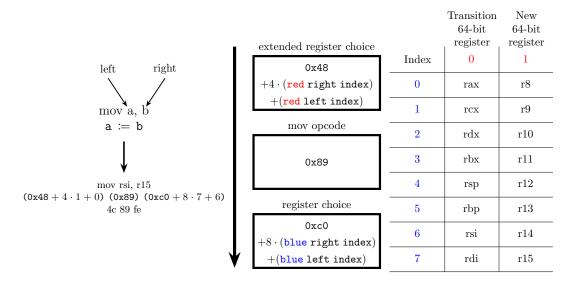

| 5.2 | x86-64 mov operation                                                   | 70 |

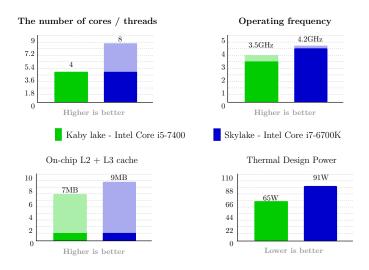

| 6.1 | Comparison between the Intel Kaby Lake i5-7400 and Skylake i7-6700k $$ | 74 |

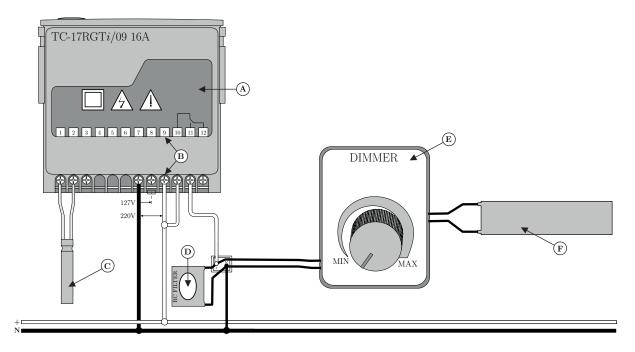

| 6.2 | DRAM aging setup                                                       | 76 |

| 6.3 | Thermostat diagram                                                     | 76 |

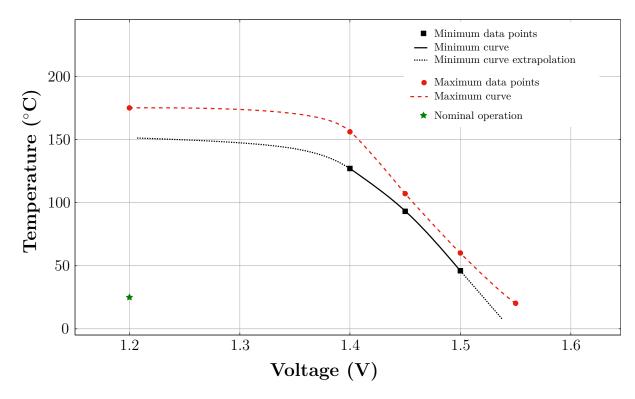

| 6.4 | DRAM operation: temperature and voltage relation                       | 78 |

## List of Tables

| 2.1 | Uniqueness of elements modulo 15                 | 32 |

|-----|--------------------------------------------------|----|

| 3.1 | Memory controller commands                       | 45 |

|     | secp256k1 twists                                 |    |

| 6.1 | Stable bits under different operating conditions | 73 |

## List of Listings

| 1 | Double-sided Rowhammer | 52 |

|---|------------------------|----|

| 2 | Single-sided Rowhammer | 54 |

| 3 | One-location Rowhammer | 54 |

## List of Algorithms

| 2.1 | ElGamal public and private key pair generation | 30 |

|-----|------------------------------------------------|----|

| 2.2 | ElGamal encryption algorithm                   | 30 |

| 2.3 | ElGamal decryption algorithm                   | 30 |

| 2.4 | RSA decryption using CRT                       | 36 |

| 5.1 | ECDSA key recovery attack                      | 69 |

| A.1 | ECDSA generation                               | 90 |

| A.2 | ECDSA verification                             | 91 |

## List of Examples and Theorems

| 2.1 | Example (Prime field $\mathbb{F}_{11}$ )                     | 24 |

|-----|--------------------------------------------------------------|----|

| 2.2 | Example (Extension field $\mathbb{F}_{41^4}$ )               | 24 |

| 2.1 | Theorem ([94, Theorem 2.19] Short Weierstrass Isomorphism)   | 28 |

| 2.3 | Example (Discrete logarithm group modulo 13)                 | 31 |

| 2.2 | Theorem ([94, Theorem 2.19] Chinese Remainder Theorem (CRT)) | 31 |

| 2.4 | Example (Uniqueness of all elements mod 15)                  | 32 |

| 2.5 | Example (NATO against Russia)                                | 32 |

| 3.1 | Example (Finding the physical address 0b000100001)           | 40 |

| 3.2 | Example (16GB DDR4 laptop)                                   | 44 |

## Contents

| 1 | Intr | oducti        |                                  | 17 |

|---|------|---------------|----------------------------------|----|

|   | 1.1  | Object        | tives                            | 18 |

|   | 1.2  | Contri        | ibutions                         | 19 |

|   | 1.3  | Organ         | ization                          | 19 |

| 2 | Pre  | limina        | ries                             | 21 |

|   | 2.1  | Basic         | Concepts of Cryptography         | 21 |

|   |      | 2.1.1         | Symmetric System                 |    |

|   |      | 2.1.2         | Asymmetric System                |    |

|   | 2.2  | Ellipti       | c-Curve Cryptography             |    |

|   |      | 2.2.1         | Fields                           |    |

|   |      | 2.2.2         | Elliptic Curves                  |    |

|   |      | 2.2.3         | Short Weierstrass                |    |

|   |      | 2.2.4         | Elliptic Curves for Cryptography |    |

|   |      | 2.2.5         | Discrete Logarithm Problem       |    |

|   |      | 2.2.6         | Chinese Remainder Theorem        |    |

|   | 2.3  | Side-cl       | hannel Attacks                   |    |

|   |      | 2.3.1         | Timing Attacks                   |    |

|   |      | 2.3.2         | Cache Attacks                    |    |

|   |      | 2.3.3         | Speculative Attacks              | 34 |

|   |      | 2.3.4         | Simple Power Analysis            |    |

|   |      | 2.3.5         | Differential Power Analysis      | 34 |

|   |      | 2.3.6         | Differential Fault Analysis      | 34 |

|   |      | 2.3.7         | Acoustic Cryptanalysis           |    |

|   |      | 2.3.8         | Remaining Data                   |    |

|   | 2.4  | Fault         | Injection Attacks                |    |

| 3 | DR   | AM M          | Iemory                           | 38 |

| J | 3.1  |               | M Architecture                   |    |

|   | 0.1  | 3.1.1         | DRAM Cells                       |    |

|   |      | 3.1.2         | DRAM Construction                |    |

|   |      | 3.1.3         | DRAM Subsystem                   |    |

|   | 3.2  |               | ry Controller                    |    |

|   | 0.2  | 3.2.1         | Memory Controller Commands       | 45 |

|   |      | 3.2.1 $3.2.2$ | Memory Timings Explained         | 47 |

|   |      | 3.2.3         | Address Mapping                  | 48 |

|   |      | 3.2.4         | The Error-Correcting Code Memory |    |

|   |      | 3.2.4         | The Target Row Refresh Solution  | 49 |

| 4       | Rov   | vhammer                                         | <b>50</b> |

|---------|-------|-------------------------------------------------|-----------|

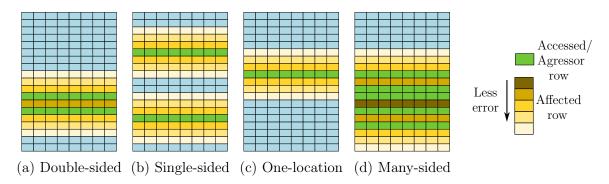

|         | 4.1   | Types of Rowhammer                              | 52        |

|         |       | 4.1.1 Double-sided Rowhammer                    | 52        |

|         |       | 4.1.2 Single-sided Rowhammer                    | 53        |

|         |       | 4.1.3 One-location Rowhammer                    | 53        |

|         |       | 4.1.4 Many-sided Rowhammer                      | 54        |

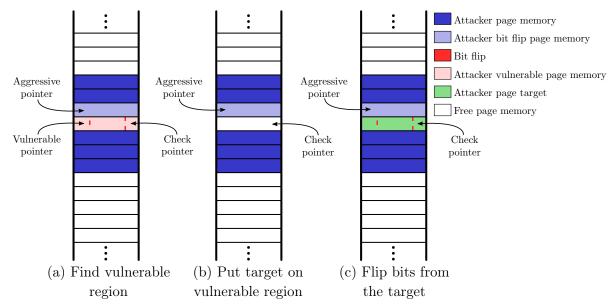

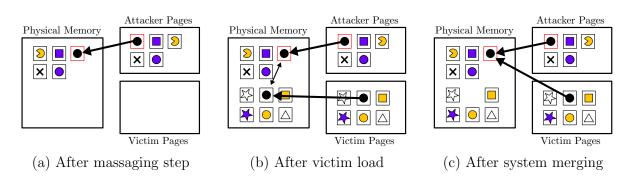

|         | 4.2   | Rowhammer Attack: Step-by-step                  | 55        |

|         |       | 4.2.1 Finding a Vulnerable Region               | 56        |

|         |       | 4.2.2 Putting a Target on the Vulnerable Region | 58        |

|         |       | 4.2.3 Flipping Bits From the Target             | 60        |

|         | 4.3   | Countermeasures                                 | 60        |

|         |       | 4.3.1 Software Countermeasures                  | 60        |

|         |       | 4.3.2 Hardware Countermeasures                  | 61        |

| 5       | ECI   | DSA, secp256k1, and Bitcoin                     | 63        |

|         | 5.1   | · · · · · · · · · · · · · · · · · · ·           | 64        |

|         |       | 5.1.1 Invalid Curve Attacks                     | 65        |

|         |       | 5.1.2 The Elliptic Curve secp256k1              | 65        |

|         | 5.2   | Bitcoin Core Wallet                             | 66        |

|         |       | 5.2.1 Countermeasures Against Fault Injections  | 66        |

|         |       | 5.2.2 A Fault Injection in secp256k1            | 68        |

|         |       | 5.2.3 A Fault Injection in ECDSA                | 70        |

| 6       | DR.   | AM Aging                                        | 72        |

|         | 6.1   | DRAM Aging Evaluation                           | 73        |

|         | 6.2   | Methodology Setup                               | 74        |

|         |       | 6.2.1 Experimental Setup                        | 74        |

|         |       | 6.2.2 Heating Setup                             | 75        |

|         | 6.3   | Preliminary Results                             | 77        |

| 7       | Con   | aclusions                                       | 79        |

| •       | 7.1   | Future Work                                     | 79        |

| Bi      | bliog | graphy                                          | 81        |

| ${f A}$ | ECI   | DSA Algorithms                                  | 90        |

| -       |       |                                                 | . 3       |

## Chapter 1

## Introduction

In cryptography, a side-channel attack is performed on a collection of information gathered during the execution of a cryptographic implementation. This information is obtained differently from a brute-force attack – that exhaust all possible inputs – or some inherent theoretical weakness of the algorithm, as in the case of the Data Encryption Standard (DES), which cryptanalysis reduces a 2<sup>56</sup>-bit brute-force attack to 2<sup>41</sup> [48]. Side-channel attacks can be performed on data obtained from running time, energy consumption, electromagnetic emanation, sound waves, and others. Paul Kocher was a pioneer in this field, showing how to perform side-channel attacks using the time channel on implementations of public-key cryptographic systems [58].

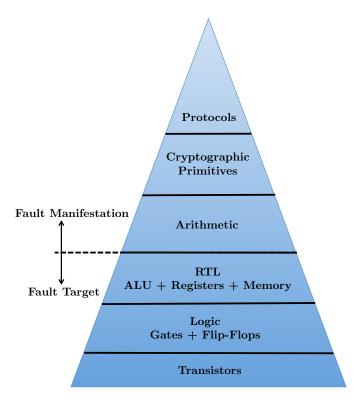

A class of side-channel attacks is Differential Fault Analysis (DFA). The principle is to induce failures during the execution of cryptographic implementations to partially or entirely reveal an internal state and then derive the cryptographic key or plaintext. DFA attacks are carried out by first injecting flaws in hardware structures, including main memory, CPU registers, logic and arithmetic units, transistors, among others. Then, the attacker observes the effect of the induced failure on higher layers, such as arithmetic, cryptographic primitives, and protocols. This process of injecting and observing is exemplified by The Fault Attack Jungle [92], which is given in Figure 1.1. This fault injection model is a pyramid, showing where faults are injected and where they manifest.

Faults can also occur in natural ways. For example, cosmic rays can induce bit flips in electronic equipment's [99]. In the 50s, anomalies were recorded by monitoring electronic equipment thanks to nuclear bomb tests [99]. In the 60s, minor flaws appeared in electronics sent into space by the space industry [99]. In the 70s, IBM started a study on how  $\alpha$  particles interfered in semiconductors [99]. These examples show that the electronics industry has been concerned with the accidental inversion of bits for over half a century. However, the injection of intentional failures depends on the level of control over the software or hardware by the malicious agent. Projects admit a fault tolerance probability rate, which is usually estimated for natural causes. In the case of purposeful failures, this probability can be as high as the failure injection power.

Figure 1.1: Security pyramid model of fault injection adapted from [92]. The base represents hardware at its lowest level, and the top represents software at its higher abstraction.

### 1.1 Objectives

The first step to being an excellent defender is to know how to perform an attack. During the process, the attacker needs to know how the system is defended, which may require much creativity. One way of attacking is to explore side channels, which allows observing design flaws and adding barriers to system protection. The study of fault-injection side-channel attacks is increasing in academy since the technologies using them are becoming accessible. For example, Karim M. et al. showed a low cost setup for Electromagnetic Fault-Injection (EMFI) attacks costing around \$200 [1].

Some software fault-injection attacks are well known, one of which uses excessive writing on SSDs to burn cells and perform a Denial-of-Service attack [31]. Another attack could be the distribution of malicious binaries that perform flawed computations, such as commercial cryptographic binaries modified by the National Security Agency (NSA) [5]. The most relevant software fault-injection attack for this work is *Rowhammer* [54]. The Rowhammer attack exploits the memory design, which contains several banks with a two-dimensional array made of rows and columns. The attack tries to focus on keeping a set of row readings in the same memory bank using a set of physical memory address. Given a consecutive series of readings ("hammering") in some memory rows, it ends up flipping bits in a predefined memory cell. The initial research of Rowhammer in Dynamic Random-Access Memory (DRAM) memories with potential for building attacks was published by Kim et al. in 2014 [54].

In late 2015, the Joint Electron Device Engineering Council (JEDEC) [47] standards

association proposed the LPDDR4 memory model that includes support for hardware that prevents the effect of Rowhammer without loss of performance and increase of power consumption. However, these measures are not enough to mitigate Rowhammer forever. Even with protections like Error-Correcting Code (ECC), Cojocar et al. showed in 2019 that Rowhammer can circumvent these countermeasures and affect this category of memories [19]. In 2020, two more attacks involving LPDDR4 models were conceived. One was used to read memories after some bit flips, also bypassing ECC protection [59]. The other can bypass the Target Row Refresh (TRR) protection, known as the ultimate defense against Rowhammer [29].

These new attacks guarantee long research on how to design new memory models and how to build countermeasures against Rowhammer in legacy memory systems. The attack can also be used on personal computers and Android smartphones to gain root privilege [89, 84]. From a cryptographic point of view, the attack has already been used to recover RSA private keys by injecting flaws and combining cache attacks [10]. It is important to remember that even if the hardware industry mitigates the attack at some point, several vulnerable memory chips – the problem arose on DDR3 memories and part of DDR4 – were sold and are still in use. In this context, this work aims to perform fault-injection attacks in a software implementation of the elliptic curve secp256k1 used by Bitcoin. Also, this work seeks to provide a brief study on how memory aging can lead to attacks similar to Rowhammer.

#### 1.2 Contributions

This work claims four contributions. First, we survey the DRAM memory operation, including its architecture with design and construction and the memory controller responsible for managing all operations over DRAM. Secondly, we survey the Rowhammer attack, detailing the attack types, how to execute an attack step-by-step, and some countermeasures. The third contribution focuses on fault injection in Bitcoin-core wallet using Rowhammer, in the Elliptic Curve Digital Signature Algorithm (ECDSA) protocol, and in the implementation of the elliptic curve secp256k1. Finally, the fourth contribution focuses on DRAM aging, seeking answers on whether a used memory may present failures similar to Rowhammer over time.

#### 1.3 Organization

This dissertation is organized as follows. Chapter 2 presents basic concepts of cryptography and elliptic curves, the Discrete Logarithm Problem, the Chinese Remainder Theorem, side-channel attacks, and fault injection. Then, Chapter 3 introduces the DRAM architecture, showing the cells' organization, construction details, and subsystem. It also presents a working memory controller, showing commands executed over the DRAM memory, memory timings used to control the memory, address mapping, Error-Correcting Code memory, and the Target Row Refresh solution.

Chapter 4 presents types of Rowhammer attacks, such as double-sided, single-sided,

one-location, and many-sided. This chapter continues addressing a step-by-step Rowhammer attack, showing how to find and put a target in a vulnerable region and flip a bit (or bits) from the target location. Lately, this chapter enumerates some software and hardware countermeasures. Chapter 5 approaches how to use Rowhammer to inject faults in the Bitcoin-core Wallet, the ECDSA protocol, and the curve secp256k1. Then, Chapter 6 addresses an initial study about DRAM aging and how it can lead to memories vulnerable to Rowhammer. Finally, Chapter 7 presents final remarks and directions for future works.

## Chapter 2

### **Preliminaries**

Cryptography is the practice and the study of techniques for secure communications in the presence of adversarial behavior [79]. These techniques aim to enforce the five pillars from Information Assurance [95]:

**Confidentiality:** a security measure that protects data against unauthorized access.

**Integrity:** a security measure that protects data against unauthorized modifications.

**Authenticity:** a security measure that provides confidence in data senders and validity of their message.

**Availability:** a security measure that ensures that data is retrieved or modified by authorized individuals.

**Non-repudiation:** a security measure that provides capability to determine if a particular action occurred such as creating information, sending a message, approving information, and receiving a message. In other words, perfect non-repudiation cannot argue falsely about the source or authenticity of data.

This chapter is organized as follows. Section 2.1 details basic concepts of cryptography, presenting symmetric and asymmetric cryptosystems. Then, Section 2.2 introduces Elliptic Curve Cryptography, including mathematical concepts, such as fields, elliptic curves and their operations, and elliptic curve for cryptography. Subsection 2.2.6 presents the Chinese Remainder Theorem (CRT), a fundamental theorem used to compose modular operations. Next, Section 2.3 details the categories of side-channel attacks: timing attack, cache attack, differential fault analysis, among others. Finally, Section 2.4 discusses fault-injection attacks.

### 2.1 Basic Concepts of Cryptography

The etymology of the word "cryptography" comes from "the art of writing secrets". A cryptographic system is defined by two bijective functions [68]: one for encryption of a

plaintext m into a ciphertext c, denoted  $E_e(m)$ , and another,  $D_d(c)$ , for decryption of a ciphertext c into a plaintext m. The encryption and decryption functions are parameterized by the keys e and d, respectively, each belonging to a finite set of keys  $\mathcal{K}$ . For every key  $e \in \mathcal{K}$ , there exists a key  $d \in \mathcal{K}$  such that  $D_d = E_e^{-1}$ ; that is,  $D_d(E_e(m)) = m$ .

A cryptographic system is weak if an attacker can systematically retrieve the plaintexts from the ciphertexts without knowledge of the keys (e, d) in a reasonable time [68]. How much is reasonable depends on the value of the information contained in the plaintext, that is, the attacker must not be able to easily enumerate all decryptions for each key  $d \in \mathcal{K}$  (brute force attack) or retrieve the plaintext by using some weakness in the algorithm (cryptoanalysis) or implementation (side-channel). In the worst case, the attacker must spend more resources, such as time, energy, and money, than the plaintext value. These definitions make it possible to classify cryptographic systems as symmetric or asymmetric.

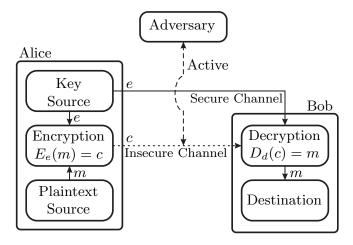

#### 2.1.1 Symmetric System

A symmetric system contains a key d for decryption and a key e for encryption, and each can be calculated from the other in polynomial time [68, Definition 1.24]. Most symmetric cryptosystems choose the encryption key to be identical to the decryption key [68]. A symmetric system is represented in Figure 2.1, in which two entities, Alice and Bob, want to establish a secure communication. The keys are generated and distributed over a secure channel inaccessible to the attacker. In Alice's entity, a plaintext m is obtained and given as input to the encryption function, thus generating a ciphertext c. Then, the ciphertext is delivered to Bob through an insecure channel, where the attacker can interact with their communication to confuse Alice and Bob. When the ciphertext arrives at Bob, it goes through decryption, and the plaintext m can be retrieved if there was no tempering.

Figure 2.1: Representation of a symmetric cryptosystem [68].

Based on the model presented above, a modern symmetric cipher uses layers of confusion (substitution), diffusion (permutation), and key addition, also known as Substitution-Permutation Networks (SPN) [39]. During decryption and encryption, there exists an internal state that goes through each of these layers for repeated rounds. A natural example of SPN is the Advanced Encryption Standard (AES) [25].

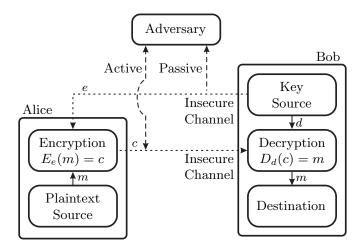

#### 2.1.2 Asymmetric System

An asymmetric system contains a public and a private key pair, so the private key cannot be derived from the public key in polynomial time [68, Definition 1.50]. Figure 2.2 represents an asymmetric system in which Alice is sending a ciphertext to Bob.

Figure 2.2: Representation of an asymmetric cryptosystem [68].

In this scenario, the attacker has access to two channels: one where he can actively interact with the insecure channel, and the other is passive, and he can observe without performing changes. Bob transmits his public key to Alice to encrypt the plaintext and send the ciphertext, which Bob then decrypts to obtain the plaintext.

### 2.2 Elliptic-Curve Cryptography

This section covers introductory concepts in elliptic-curve cryptography, such as the definition of fields, elliptic curves, equivalent curves, and isomorphisms, required for a greater understanding of the following chapters.

#### 2.2.1 Fields

The triple  $(\mathbb{K}, +, \star)$  represents a field  $\mathbb{K}$ , in which  $\mathbb{K}$  is an non-empty set, + is the addition in the field  $\mathbb{K}$ , and  $\star$  is the multiplication in  $\mathbb{K}$ . The binary operations of addition and multiplication in the field  $\mathbb{K}$  satisfy the following properties:

- Addition defined by the function  $+ : \mathbb{K} \times \mathbb{K} \to \mathbb{K}$ .

- 1. Commutative:  $\alpha + \beta = \beta + \alpha, \forall \alpha, \beta \in \mathbb{K}$ .

- 2. Associative:  $(\alpha + \beta) + \gamma = \alpha + (\beta + \gamma), \forall \alpha, \beta, \gamma \in \mathbb{K}$ .

- 3. Neutral element:  $\exists 0 \in \mathbb{K} \mid \alpha + 0 = \alpha, \forall \alpha \in \mathbb{K}$ .

- 4. Inverse:  $\exists -\alpha \in \mathbb{K} \mid \alpha + (-\alpha) = \mathbb{O}, \forall \alpha \in \mathbb{K}.$

- Multiplication defined by the function  $\star : \mathbb{K} \times \mathbb{K} \to \mathbb{K}$ .

- 1. Commutative:  $\alpha \star \beta = \beta \star \alpha, \forall \alpha, \beta \in \mathbb{K}$ .

- 2. Associative:  $(\alpha \star \beta) \star \gamma = \alpha \star (\beta \star \gamma), \forall \alpha, \beta, \gamma \in \mathbb{K}$ .

- 3. Distributive:  $\gamma \star (\alpha + \beta) = \alpha \star \gamma + \beta \star \gamma, \forall \alpha, \beta, \gamma \in \mathbb{K}$ .

- 4. Neutral element:  $\exists 1 \in \mathbb{K} \mid \alpha \star 1 = \alpha, \forall \alpha \in \mathbb{K}.$

- 5. Inverse element:  $\exists \alpha^{-1} \in \mathbb{K} \setminus \{0\} \mid \alpha \star \alpha^{-1} = 1, \forall \alpha \in \mathbb{K} \setminus \{0\}.$

In the field  $\mathbb{K}$ , subtraction is done by adding the inverse additive, and division is performed by multiplying by the multiplicative inverse. The sets of rational  $\mathbb{Q}$ , real  $\mathbb{R}$ , and complex numbers  $\mathbb{C}$  are examples of infinite fields.

The order of a field is the number of elements in  $\mathbb{K}$ . There exists a finite field  $\mathbb{F}$  of order q if and only if q is a prime power, that is,  $q = p^m$  for a prime number p called the characteristic of  $\mathbb{F}$ , and m a positive integer. If m = 1,  $\mathbb{F}$  is said to be a prime field; otherwise, it is an extension field.

**Example 2.1** (Prime field  $\mathbb{F}_{11}$ ). The elements of the prime field  $\mathbb{F}_{11}$  are  $\{0, 1, 2, \dots, 10\}$ . Examples of arithmetic operations in  $\mathbb{F}_{11}$  are as follows.

- i) Addition: 5 + 9 = 3, since  $14 \mod 11 = 3$ .

- ii) Subtraction: 6 9 = 8, since  $-3 \mod 11 = 8$ .

- iii) Multiplication:  $7 \star 3 = 10$ , since 21 mod 11 = 10.

- iv) Inversion:  $7^{-1} = 8$ , since  $7 \star 8 \mod 11 = 1$ .

Let p be a prime and  $m \geq 2$ .  $\mathbb{F}_p[x]$  denotes the set of all polynomials in the variable x with coefficients in  $\mathbb{F}_p$ . Let f(x) be an irreducible polynomial of degree m in  $\mathbb{F}_p[x]$ . A polynomial f(x) that cannot be factored as a product of polynomials in  $\mathbb{F}_p[x]$ , each of degree less than m, is said to be *irreducible*. The elements of  $\mathbb{F}_{p^m}$  are the polynomials in  $\mathbb{F}_p[x]$  of degree at most m-1:

$$\mathbb{F}_{p^m} = \{a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \ldots + a_2x^2 + a_1x + a_0 : a_i \in \mathbb{F}_p\}$$

The addition in a field is the usual addition of polynomials with coefficient arithmetic done in  $\mathbb{F}_p$ . In turn, the multiplication of field elements is performed modulo an irreducible polynomial f(x).

**Example 2.2** (Extension field  $\mathbb{F}_{41^4}$ ). Let p=41 and m=4. It is possible to use the irreducible polynomial  $f(x)=2x^4+15x^2+29x+21$  in  $\mathbb{F}_{41^4}$ . Examples of arithmetic operations in  $\mathbb{F}_{41^4}$  are as follows. Let  $a=32x^3+39x+5$  and  $b=15x^3+10x^2+21$ .

- i) Addition:  $a + b = 6x^3 + 10x^2 + 39x + 26$ .

- ii) Subtraction:  $a b = 17x^3 + 31x^2 + 39x + 25$ .

- iii) Multiplication:  $a \star b = 18x^3 + 6x^2 + 33x + 8$ .

- iv) Inversion:  $a^{-1} = 21x^3 + 14x^2 + 2x + 24$ .

The algebraic closure of a field  $\mathbb{K}$  is denoted  $\overline{\mathbb{K}}$ , such that  $\alpha \in \overline{\mathbb{K}}$  is root of a non-constant polynomial  $P(x) = \sum_{i=0}^{n} a_i x^i$ ,  $a_i \in \mathbb{K}$ , that is,  $P(\alpha) = \mathbb{O}$  [49]. For example, the algebraic closure of  $\mathbb{R}$  is the set of complex numbers  $\mathbb{C}$ . Also, every non-constant polynomial P(x) with coefficients in  $\mathbb{R}$  has roots in the set of complex numbers. For example, the polynomial  $P(x) = x^3 - x^2 + x - 1$  has one real root, which is 1, and two complex roots: i and -i. The algebraic closure of a field  $\mathbb{F}_{p^m}$  is the union of all fields of extensions  $\mathbb{F}_{p^m}$  for all  $m \geq 1$ .

#### 2.2.2 Elliptic Curves

An elliptic curve E over a field  $\mathbb{K}$ , denoted  $E(\mathbb{K})$ , can be defined by the Weierstrass equation [38, 9] as

$$E: a_0 y^2 + a_1 xy + a_3 y = x^3 + a_2 x^2 + a_4 x + a_6,$$

(2.1)

for all  $a_i \in \mathbb{K}$  and  $a_0 \neq 0$ . An elliptic curve requires the discriminant to be to ensure the non-existence of points  $P = (x_P, y_P) \in E(\mathbb{K})$  for which the curve has two or more distinct tangent lines. This requirement forms a rule used to perform point additions. The discriminant is obtained using the j-invariant equation [94, 23], which was studied as a parameterization of elliptic curves over complex numbers, denoted j(E) in the short Weierstrass (Equation 2.2) and Montgomery (Equation 2.3) equations. The j-invariant equation indicates if an elliptic curve equation can be transformed into another one in the algebraic closure  $\overline{\mathbb{K}}$ . In other words, the points satisfying the curve equations E and E' can be transformed into each other if j(E) = j(E'), showing that E is isomorphic to E' as described in Theorem 2.1. Moreover, elliptic curves with the same j-invariant are said to be a twist of each other.

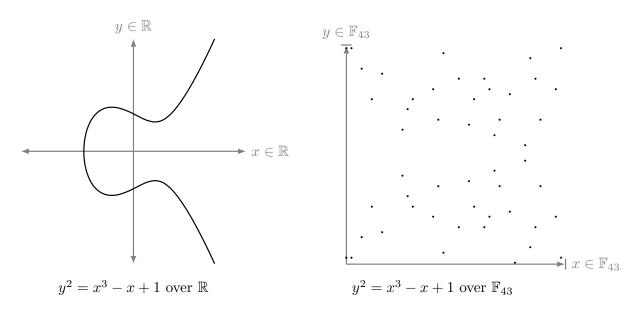

Figure 2.3 exemplifies the elliptic curve  $E: y^2 = x^3 - x + 1$  over the infinite field  $\mathbb{R}$  and the finite prime field  $\mathbb{F}_{43}$ .

Figure 2.3: Example of elliptic curves over  $\mathbb{R}$  and  $\mathbb{F}_{43}$ .

The Weierstrass equation, given in Equation 2.1, contains many simplifications, including the short Weierstrass and Montgomery curves equations, commonly used to represent elliptic curves defined over a finite prime field  $\mathbb{F}_p$ . The short Weierstrass equation has the form

$$E: y^{2} = x^{3} + ax + b$$

$$j(E) = 1728 \frac{4a^{3}}{\Delta} = 1728 \frac{4a^{3}}{4a^{3} + 27b^{2}}$$

$$4a^{3} + 27b^{2} \neq 0 \mod p,$$

$$(2.2)$$

whereas the Montgomery equation is given by form:

$$E: by^{2} = x^{3} + ax^{2} + x$$

$$j(E) = 256 \frac{(a^{2} - 3)^{3}}{\Delta} = 256 \frac{(a^{2} - 3)^{3}}{a^{2} - 4}$$

$$b(a^{2} - 4) \neq 0 \mod p.$$

(2.3)

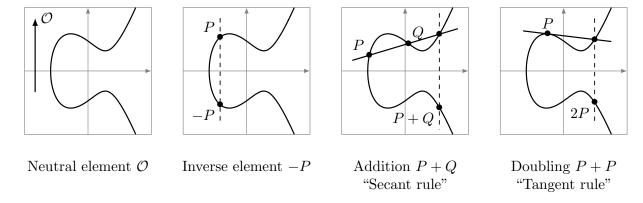

The addition of two points in  $E(\mathbb{K})$  is given by chord-and-tangent rules, for which the result is a third point in  $E(\mathbb{K})$ . The chord rule, also known as the secant rule, is used to add two distinct points P + Q. In contrast, the tangent rule is used to double a point P as P + P = 2P. Thus, elements of  $E(\mathbb{K})$  form an additive group endowed with chord-and-tangent rules for addition, having  $\mathcal{O}$  as the neutral element. Commonly, the neutral element is also represented as  $\infty$  and referred to as the point "at infinity". Additive operations and the representation of the neutral and inverse elements are illustrated in Figure 2.4 for the elliptic curve  $E(\mathbb{R})$ . Note that the secant-tangent rules can be used interchangeably to obtain n doublings of the point P, that is, for computing nP. For example, the calculation of 5P can be made up of two doublings using the tangent rule – one for getting 2P and the other for 4P – and a sum of points using the chord rule for obtaining 4P + P.

Figure 2.4: Operations performed in an elliptic curve E in its additive group over  $\mathbb{R}$ .

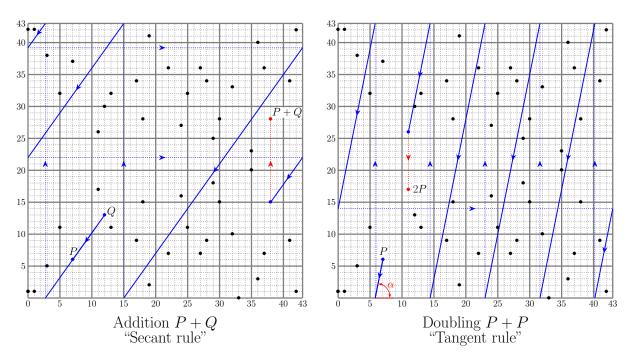

We can also perform addition operations in an elliptic curve over a finite field. For instance, Figure 2.5 represents the chord-and-tangent rules for the curve  $E: y^2 = x^3 - x + 1$  over  $\mathbb{F}_{43}$ . In the figure, consider that P = (7,6) and Q = (12,13). Thus, P + Q = (38,28) and 2P = (11,17). Also, the angular coefficient  $\alpha$  of the tangent line  $y = \alpha x + \beta$

is  $\alpha=(3x_R^2-1)2^{-1}y_R^{-1} \mod 43$  for  $R=(x_R,y_R)\in E(\mathbb{F}_{43})$ . Thus, from the angular coefficient equation, we obtain that  $\alpha=(3x_P^2-1)2^{-1}y_P^{-1}=(3\cdot 7^2-1)2^{-1}6^{-1}=5$  and, from the line equation, the first  $\beta$  is  $\beta=y_P-\alpha x_P=6-5\cdot 7=-29$ . Observe that  $\beta$  needs to be changed for the line being kept inside  $\mathbb{F}_{43}$ .

Figure 2.5: Representation of the addition and doubling operations for the elliptic curve  $E: y^2 = x^3 - x + 1$  in its additive group over the field  $\mathbb{F}_{43}$ .

The order of an elliptic curve E defined over a prime finite field  $\mathbb{F}_p$  is of the form  $\#E(\mathbb{F}_p) = h \cdot \ell$ , where  $\ell \in \mathbb{Z}$  is the largest prime number that divides  $\#E(\mathbb{F}_p)$  and  $h \in \mathbb{Z}$  is the cofactor. In particular, the curve  $E : y^2 = x^3 - x + 1$  over  $\mathbb{F}_{43}$ , depicted in Figure 2.3, has order  $52 = (2^4) \cdot 13$ , meaning that  $h = 2^4 = 4$  and  $\ell = 13$ .

#### 2.2.3 Short Weierstrass

This section introduces concepts of group law and isomorphism for elliptic curves, as required by Short Weierstrass curves that are elaborated in Chapter 5.

#### Group Law

A group law for the elliptic curve  $E(\mathbb{K}): y^2 = x^3 + ax + b$  with characteristic  $\mathbb{K} \neq \{2, 3\}$  contains the following properties [38, Section 3.1.2].

- i) Identity:  $P + \infty = \infty + P = P$  for all  $P \in E(\mathbb{K})$ .

- ii) Inverses: If  $P = (x, y) \in E(\mathbb{K})$ , then  $(x, y) + (x, -y) = \infty$ . The point (x, -y) is denoted by -P and is called the *additive inverse* of P. Note that -P is a point in  $E(\mathbb{K})$ . Also,  $-\infty = \infty$ .

iii) Point addition: Consider  $P=(x_1,y_1)\in E(\mathbb{K})$  and  $Q=(x_2,y_2)\in E(\mathbb{K})$  with  $P\neq \pm Q$ . Then, the addition  $P+Q=(x_3,y_3)$  is given by

$$x_3 = \left(\frac{y_2 - y_1}{x_2 - x_1}\right)^2 - x_1 - x_2$$

and  $y_3 = \left(\frac{y_2 - y_1}{x_2 - x_1}\right)(x_1 - x_3) - y_1$ .

iv) Point doubling: Consider  $P = (x_1, y_1) \in E(\mathbb{K})$  with  $P \neq -P$ . Then,  $2P = (x_3, y_3)$  is given by

$$x_3 = \left(\frac{3x_1^2 + a}{2y_1}\right)^2 - 2x_1$$

and  $y_3 = \left(\frac{3x_1^2 + a}{2y_1}\right)(x_1 - x_3) - y_1$ .

#### Isomorphisms

The isomorphism of two short Weierstrass elliptic curves is addressed by the Short Weierstrass Isomorphism, which is given in Theorem 2.1.

**Theorem 2.1** ([94, Theorem 2.19] Short Weierstrass Isomorphism). Let  $y_1^2 = x_1^3 + a_1x_1 + b_1$  and  $y_2^2 = x_2^3 + a_2x_2 + b_2$  be two elliptic curves with j-invariants  $j_1$  and  $j_2$ , respectively. If  $j_1 = j_2$ , then there exists  $0 \neq \mu \in \overline{\mathbb{K}}$  such that

$$a_2 = \mu^4 a_1$$

and  $b_2 = \mu^6 b_1$ .

Moreover, the transformation

$$x_2 = \mu^2 x_1, \qquad y_2 = \mu^3 y_1$$

takes one equation to the other.

*Proof.* First assume that  $a_1 \neq 0$ . Since this is equivalent to  $j_1 \neq 0$ , this imply also  $a_2 \neq 0$ . Choose  $\mu$  such that  $a_2 = \mu^4 a_1$ . Then

$$\frac{4a_2^3}{4a_2^3 + 27b_2^2} = \frac{4a_1^3}{4a_1^3 + 27b_1^2} = \frac{4\mu^{-12}a_2^3}{4\mu^{-12}a_2^3 + 27b_1^2} = \frac{4a_2^3}{4a_2^3 + 27\mu^{12}b_1^2}$$

which implies that

$$b_2^2 = (\mu^6 b_1^2)^2.$$

Therefore  $b^2 = \pm \mu^6 b_1$ . If  $b_2 = \mu^6 b_1$ , ended. If  $b_2 = -\mu^6 b_1$ , then change  $\mu$  to  $i\mu$  (where  $i^2 = -1$ ). This preserve the realation  $a_2 = \mu^4 a_1$  and also yields to  $b_2 = \mu^6 b_1$ .

If  $a_1 = 0$ , then  $a_2 = 0$ . Since  $4a_i^3 + 27b_i^2 \neq 0$ , we have  $b_1, b_2 \neq 0$ . Choose  $\mu$  such that  $b_2 = \mu^6 b_1$ .

### 2.2.4 Elliptic Curves for Cryptography

An additive group  $E(\mathbb{F}_p)$ , for p prime, can be composed with linear combinations of its subgroups. In particular, it is possible to compose  $E(\mathbb{F}_p)$  with the subgroups E[h] and  $E[\ell]$ , which order subgroups are h and  $\ell$ , respectively. When the integer h is composite,

the subgroup E[h] can be decomposed into the subgroups corresponding to the factors of h. A point G is said to be a generator of the subgroup E[x] if, for each point R in the subgroup x, there exists a scalar n such that  $R = n \cdot G$ .

For cryptography, the order  $h \cdot \ell$  of an elliptic curve is appropriate when  $\ell$  is a large prime number, and h is a small integer. Thus, this format of group order avoids a decomposition of  $E(\mathbb{F}_p)$  into much smaller subgroups [8]. Additionally, only one generator is used for the subgroup  $E[\ell]$ , avoiding confinement in subgroups. In other words, for a generator  $G \in E[\ell]$  with  $k \in \mathbb{Z}$ , we choose  $k \cdot G \in E[\ell]$  instead of a random generator  $G \in E(\mathbb{F}_p)$  that can lie in some subgroup in E[h].

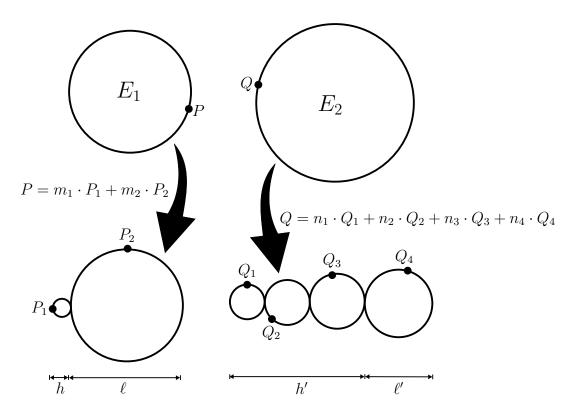

A curve  $E_1$  with order  $h \cdot \ell$  may contain an unsafe twist curve  $E_2$  with order  $h' \cdot \ell'$ , for which the subgroup E[h'] is composed of several small subgroups and  $h' \gg h$ . Thus, an invalid curve attack can be performed by computing a point  $Q \in E_2$  as if it was on  $E_1$  [8]. Figure 2.6 exemplifies a curve  $E_1$  with good properties for cryptography and an insecure twist  $E_2$  containing several smaller subgroups.

Figure 2.6: Two elliptic curves  $E_1$  and  $E_2$ , where one is a twist of the other. If  $\ell$  is a large prime, the curve  $E_1$  contains a good safety margin since h is a small integer. The curve  $E_2$  is considered unsafe because it contains a composite cofactor h', allowing the subgroup E[h'] to be factored into several smaller subgroups. Both curves contain illustrations of how a point behaves in  $E(\mathbb{F}_p)$  and in its subgroups.

Compared to RSA<sup>1</sup> [78], asymmetric cryptosystems based on elliptic curves excel in two aspects. The first is performance, as curve implementations are more compact and efficient [38]. The second aspect is the key size to achieve a certain security level. When considering the bit security provided by a symmetric system using a 256-bit AES key [25],

<sup>&</sup>lt;sup>1</sup>RSA, an asymmetric cryptographic system based on integer factorization.

RSA requires a 15360-bit key, whereas a curve-based cryptosystem needs only a 512-bit [6].

For illustration, the ElGamal cryptographic system using elliptic curves is presented in Algorithm 2.1, Algorithm 2.2, and Algorithm 2.3, which describe the tasks of key generation, encryption, and decryption, respectively.

During encryption, the function CHANGE\_TO\_POINT takes as input a plaintext m, given as a sequence of bytes, and encodes it into a point M=(x,y). In the Elliptic Curve Cryptosystems [56, section 3], Koblitz describes some methods to encode plaintext messages as elliptic curve points. One of the methods is usually described as Koblitz's method and assumes that we are working over a prime field  $\mathbb{F}_p$  and that plaintext is represented as a non-negative integer m less than  $\frac{p}{1000} - 1$ . To encode, let x coordinates be  $x = 1000m, 1000m + 1, \cdots, 1000m + 999$  until find one where it is possible to compute the corresponding y-coordinate. Generally speaking, if the Koblitz method does not lead to a valid point on the curve, an alternative approach is to adopt a more complex encoding mechanism [28].

At the decryption's end, the inverse function Change\_To\_Message maps a point M back into a byte array m. In the above example, if M = (x, y) and  $x = 1000m, 1000m + 1, \dots, 1000m + 999$ , then Change\_To\_Message decoding is achieved by deleting the last 3 digits of the x-coordinate of an elliptic curve point.

#### Algorithm 2.1 Public and private key pair generation for ElGamal

**Require:** Prime p, curve E, generator point G, and order n

**Ensure:** Point S as the public key and scalar d as the private key

1:

$$d \stackrel{\$}{\leftarrow} \mathbb{Z}_n^*$$

$\triangleright$  Choose a random number in  $\mathbb{Z}_n^* = \{a \mid \gcd(a,n) = 1\}$

2:  $S \leftarrow d \cdot G$

#### **Algorithm 2.2** Encryption of a plaintext m using elliptic curves in ElGamal

**Require:** Prime p, curve E, generator point G, order n, public key S, and plaintext m **Ensure:** Ciphertext  $(C_1, C_2)$

```

1: M \leftarrow \text{CHANGE\_TO\_POINT}(m) \triangleright Transform the message m into a point (x, y)

```

2:

$$k \stackrel{\$}{\leftarrow} \mathbb{Z}_n^*$$

$\triangleright$  Choose a random number in  $\mathbb{Z}_n^* = \{a \mid \gcd(a, n) = 1\}$

3:  $C_1 = k \cdot G$

$4: C_2 = M + k \cdot S$

#### **Algorithm 2.3** Decryption of a ciphertext c using elliptic curves in ElGamal

**Require:** Prime p, curve E, order n, private key d, and ciphertext  $(C_1, C_2)$

Ensure: Plaintext m

1:

$$X \leftarrow d \cdot C_1$$

$\Rightarrow d \cdot C_1 = d \cdot k \cdot G = k \cdot S$

$2: M \leftarrow C_2 - X$

3:  $m \leftarrow \text{CHANGE\_TO\_MESSAGE}(M) \triangleright \text{Transform the point } (x, y) \text{ into the message } m$

#### 2.2.5 Discrete Logarithm Problem

The logarithm  $\log_b a$  is a number k such that  $b^k = a$ . In mathematics, a group is a set equipped with an operation that associates any two elements with a third element belonging to the same group. A discrete logarithm is a group G, where  $\log_b a$  is an integer k such that  $b^k = a$ . For finite cyclic groups, it follows that  $\log_b a = k$  is  $b^k \equiv a \mod m$ .

**Example 2.3** (Discrete logarithm group modulo 13). Next, we enumerate every integer number b in the group G that has solution for  $\log_b 5$  in the cyclic group  $G = \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12\}$ , the set of integers modulo 13. By definition,  $b^k = 5 \mod 13$  with  $b, k \in G$ . Thus, the solutions are:

```

• b = 2, k = 9: 2^9 \equiv 5 \mod 13

```

•

$$b = 5, k = \{1, 5, 9\}$$

:  $5^1 \equiv 5^5 \equiv 5^9 \equiv 5 \mod 13$

•

$$b = 6, k = 9$$

:  $6^9 \equiv 5 \mod 13$

•

$$b = 7, k = 3$$

:  $7^3 \equiv 5 \mod 13$

•

$$b = 8, k = \{3, 7, 11\}$$

:  $8^3 \equiv 8^7 \equiv 8^{11} \equiv 5 \mod 13$

•

$$b = 11, k = 3$$

:  $11^3 \equiv 5 \mod 13$

Similar to integer factorization, the complexity of solving an instance of the Discrete Logarithm Problem increases according to the size of the numbers. In 1993, Menezes et al. showed how to convert Elliptic Curve Discrete Logarithm Problem (ECDLP) into the Discrete Logarithm Problem over a finite field [67]. This made it possible to finding the private key of an elliptic curve system instantiated with supersingular curves.

#### 2.2.6 Chinese Remainder Theorem

Invalid curve attacks occurs when an attacker forces the victim to compute a common secret point  $d \cdot G'$  using a point  $G' \in E'[\ell']$  outside of the original defined curve E subverting the computation of  $d \cdot G$  to  $d \cdot G'$ . Where G is the generator of  $E[\ell]$ , G' is the generator of  $E'[\ell']$  with  $\ell \gg \ell'$ , and d is the private key. Because of that, an attacker can solve the Discrete Logarithm Problem over  $\ell'$  and partially recover d. As a result, instead of obtaining  $d \mod \ell$ , the attacker will have  $d \mod \ell'$ . Then, using some computations in other subgroups, the result is combined using the Chinese Remainder Theorem (CRT):

**Theorem 2.2** ([94, Theorem 2.19] Chinese Remainder Theorem (CRT)). If the integers  $n_1, n_2, \ldots, n_k$  are pairwise relatively prime, that is,  $gcd(n_i, n_j) = 1$  for  $i \neq j$ , then the system of simultaneous congruences

$$x \equiv a_1 \bmod n_1$$

$$x \equiv a_2 \bmod n_2$$

$$\vdots$$

$$x \equiv a_k \bmod n_k$$

has an unique solution modulo  $n = n_1 n_2 \cdots n_k$  [68, Definition 2.120]. By Gauss's algorithm [68, Definition 2.121] the solution x to the simultaneous congruences in the Chinese Remainder Theorem may be computed as  $x = \sum_{i=1}^k a_i N_i M_i \mod n$ , where  $N_i = n/n_i$  and  $M_i \equiv N_i^{-1} \mod n_i$ .

The CRT can be used to recover an elliptic curve point from subgroups, as shown in Figure 2.6. The potential of CRT is illustrated in Example 2.4 and Example 2.5. Example 2.4 shows the uniqueness of group elements when represented in its subgroups. Also, Example 2.5 illustrates how the theorem can be used with large numbers.

**Example 2.4** (Uniqueness of all elements mod 15). Table 2.1 enumerates all numbers from 0 to 14, showing that each number is unique when written modulo 3 and modulo 5. For example,  $11 \equiv 1 \mod 5$  and  $11 \equiv 2 \mod 3$ .

Table 2.1: Uniqueness of elements mod 15. Rows and columns show elements modulo 3 and 5, respectively.

| mod5<br>mod3 | 0  | 1  | 2  | 3  | 4  |

|--------------|----|----|----|----|----|

| 0            | 0  | 6  | 12 | 3  | 9  |

| 1            | 10 | 1  | 7  | 13 | 4  |

| 2            | 5  | 11 | 2  | 8  | 14 |

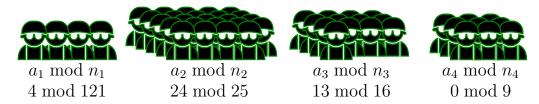

**Example 2.5** (NATO against Russia). A North Atlantic Treaty Organization (NATO) captain is responsible for counting the number of soldiers about to invade Russian territory. When he arrived in front of the squad of soldiers, they were organized in groups of  $n_1 = 11 \times 11$ . One of the groups contained only four soldiers. The captain wanted to know the exact number of soldiers, and he knew the approximate number was 200,000. So, he asked the soldiers to reorganize themselves into groups of  $n_2 = 5 \times 5$ ,  $n_3 = 4 \times 4$ , and  $n_4 = 3 \times 3$ . In all configurations, there was an incomplete group, as depicted in Figure 2.7. Particularly, for the  $5 \times 5$  and  $4 \times 4$  compositions, the number of remaining soldiers in the incomplete group was 24 and 13, respectively.

Figure 2.7: Columns and columns of soldiers organized in groups of  $11 \times 11 = 121$ ,  $5 \times 5 = 25$ ,  $4 \times 4 = 16$ , and  $3 \times 3 = 9$ .

Thus, the exact number of soldiers sent for the mission was obtained via CRT. First, consider that  $n = n_1 n_2 n_3 n_4 = 121 \cdot 25 \cdot 16 \cdot 9 = 435{,}600$ . Then, the computation proceeds

as follows.

$$\begin{split} N_1 &= n/n_1 = n_2 n_3 n_4 = 25 \cdot 16 \cdot 9 = 3{,}600 \\ N_2 &= n/n_2 = n_1 n_3 n_4 = 121 \cdot 16 \cdot 9 = 17{,}424 \\ N_3 &= n/n_3 = n_1 n_2 n_4 = 121 \cdot 25 \cdot 9 = 27{,}225 \\ N_4 &= n/n_4 = n_1 n_2 n_3 = 121 \cdot 25 \cdot 16 = 48{,}400 \\ M_1 &\equiv N_1^{-1} \mod n_1 \equiv 3{,}600^{-1} \mod 121 \equiv 91^{-1} \mod 121 \equiv 4 \mod 121 \\ M_2 &\equiv N_2^{-1} \mod n_2 \equiv 17{,}424^{-1} \mod 25 \equiv 24^{-1} \mod 25 \equiv 24 \mod 25 \\ M_3 &\equiv N_3^{-1} \mod n_3 \equiv 27{,}225^{-1} \mod 16 \equiv 9^{-1} \mod 16 \equiv 9 \mod 16 \\ M_4 &\equiv N_4^{-1} \mod n_4 \equiv 48{,}400^{-1} \mod 9 \equiv 7^{-1} \mod 9 \equiv 4 \mod 9 \end{split}$$

Finally, the exact number of soldiers is the combination of the partial results

$$x = (a_1N_1M_1 + a_2N_2M_2 + a_3N_3M_3 + a_4N_4M_4) \mod n$$

$$= (4 \cdot 3,600 \cdot 4 + 24 \cdot 17,424 \cdot 24 + 13 \cdot 27,225 \cdot 9 + 0 \cdot 48,400 \cdot 4) \mod 435,600$$

$$= 221,149 \mod 435,600,$$

which is  $x = 221,149$ .

#### 2.3 Side-channel Attacks

From time to time, an ingenious side-channel attack emerges. Examples are acoustic cryptanalysis that gained strength in 2014 [32], and speculative attacks such as Meltdown [64] and Spectre [57] in 2018. The following are the most popular categories of side-channel attacks, demonstrating the importance of concerning side-channel attacks when building a cryptographic model and carefully implementing it.

#### 2.3.1 Timing Attacks

Timing attacks (TA) rely only on the algorithm execution time. This type of attack was introduced by Paul Kocher, who demonstrated its use on asymmetric cryptographic algorithms for recovering the private key [58]. Another classic timing attack relies on an authentication forge attack over HMACs<sup>2</sup>, in which the attacker uses variances on the HMAC verification time to build a forged HMAC [61]. A countermeasure against timing attacks is the isochronous implementation of primitives that handle sensitive information.

#### 2.3.2 Cache Attacks

Cache attacks (CA) are based on the ability to monitor the accesses to the victim's cache by sharing part of the same physical memory addresses. For example, both the victim and attacker can share the same library. Cache attacks can be considered a subcategory of

<sup>&</sup>lt;sup>2</sup>HMAC, the acronym for Hash Message Authentication Code.

timing attacks, as they require comparing time measurements. An example is the attack FLUSH + RELOAD [97], which managed to retrieve an RSA key of 1024 bits by watching accesses to the cache of a GnuPG implementation<sup>3</sup>.

#### 2.3.3 Speculative Attacks

Speculative Attacks (SA) are based on the ability to monitor the speculative execution of the processor. Speculative attacks can be considered a subcategory of cache attacks, as they require comparing time measurements in the cache memory. Examples are Meltdown [64] and Spectre [57]. In particular, Meltdown breaks the mechanism that keeps applications from accessing the system's arbitrary memory (a.k.a, the kernel memory). In turn, Spectre tricks other applications into accessing arbitrary locations in their memory, allowing secret information to be leaked.

#### 2.3.4 Simple Power Analysis

Simple Power Analysis (SPA) is a type of side-channel attack based on the observation of electromagnetic emanations that allows the reconstruction of related information. A classic example of a SPA attack was performed by Van Eck [90], which recovered what was being played on a monitor about 1 km away through the leakage of electromagnetic waves. This category of attacks is old, prior to the 80s, and contains examples of how spy agencies use it to retrieve information. In the case of the United States, the project dedicated to observing these leaks is known as TEMPEST [42] and is implemented by the National Security Agency (NSA).

#### 2.3.5 Differential Power Analysis

Side-channel attacks using Differential Power Analysis (DPA) interconnect data dependencies by capturing electromagnetic emanations. In other words, several power measurements of the same stretch can make a difference and help infer some private data. An example of a DPA attack is the work of Nascimento et al., which used 1,000 measures to recover about 80% of a 256-bit key of an elliptic curve [60].

#### 2.3.6 Differential Fault Analysis

Differential Fault Analysis (DFA) is a side-channel attack that introduces faults during computation. In the work of Tunstall et al. [88], for example, a 128-bit key was retrieved from AES by injecting faults through the clock.

### 2.3.7 Acoustic Cryptanalysis

Attacks based on Acoustic Cryptanalysis (AC) use the sound produced during computation. An example was given in 2014 by Genkin et al. when a 4096-bit RSA key was fully recovered through the sound emitted by the processor [32].

<sup>3</sup>https://www.gnupg.org/.

#### 2.3.8 Remaining Data

Side-channel attacks can be performed based on retrieving sensitive data remaining in memory after being supposedly deleted. The work of Halderman et al. showed how to obtain the decryption key from an encrypted hard drive by freezing the memory in liquid nitrogen [37], characterizing a cold boot attack. Cold boot attacks can retrieve cryptographic keys in memory even when the computer screen is locked.

### 2.4 Fault Injection Attacks

The fault injection model works with four aspects [92]:

- 1. **Granularity:** how many bits are affected by the failure.

- 2. **Modification:** given a fixed bit, set as either zero or one, a modification can invert its value or make it random.

- 3. **Control:** guarantees location and when the failure will occur. The control can be precise, vague, or none.

- 4. **Duration or failure effect:** describes whether the failure is transient, permanent, or destructive.

A system can be attacked or analyzed in a non-invasive or invasive way. The classification is defined according to the operations performed on the chip. The best non-invasive techniques consist of reducing the supply voltage [4], changing the temperature [41], increasing supply voltages in small spikes [51, 82], and inducing fault-injection by clock [3]. On the other hand, the invasive technique can be considered an optical exposure [85, 91, 24]. For that, the attack requires uncapping the chip, causing permanent damage.

The Chinese Remainder Theorem (Subsection 2.2.6) is employed in implementations to accelerate computational calculations with large numbers. In the 90s, researchers began to worry about generating intentional failures [14, 13]. The RSA was the first cryptographic algorithm to suffer a fault-injection attack. In the implementation in question [14], RSA used the CRT for working with the primes that lead to the module  $n = p \cdot q$  so that the decryption would follow the procedure described in Algorithm 2.4.

#### Algorithm 2.4 RSA decryption using CRT

**Pre-computed:**  $p_{inv} \leftarrow p^{-1} \mod q$ ,  $n = p \cdot q$ .

**Require:** Primes p and q, ciphertext c, and a private key given by the pairs  $d_p = e^{-1} \mod (p-1)$  and  $d_q = e^{-1} \mod (q-1)$ , where e is the public key.

Ensure: Plaintext m.

```

1: procedure RSA_CRT(p, q, c, d_p, d_q)

2: m_p \leftarrow c^{d_p} \mod p

3: m_q \leftarrow c^{d_q} \mod q

```

4:  $m \leftarrow (((m_q - m_p) \cdot p_{inv}) \mod q) \cdot p + m_p \mod n$

5: return m

6: end procedure

The attack [14] used the following procedures:

- Insert ciphertext c and collect plaintext m.

- Insert ciphertext c, inject any failure into  $m_p$  or  $m_q$ , and collect the plaintext  $\widehat{m}$ .

- Compute the greatest common divisor of  $(m-\widehat{m})$  and n to factor the RSA modulus, since  $(m-\widehat{m})$  contains a common factor with n.

Without loss of generality, suppose that the fault was injected in  $m_q$ . Thus,

$$m - \widehat{m} = ((((m_q - m_p) \cdot p_{inv}) \bmod q) \cdot p + m_p)$$

$$- ((((\widehat{m_q} - m_p) \cdot p_{inv}) \bmod q) \cdot p + m_p) \bmod n$$

$$= (m_q - \widehat{m_q}) \cdot p_{inv} \cdot p \bmod n$$

Therefore,  $gcd(m - \widehat{m}, n) = p$ .

In 2000, three fault injection attacks were proposed on elliptic curves in the work of Biehl et al. [12]:

- 1. Some implementations do not check if a certain point is on the desired curve. Thus, the attacker can use a point on another curve (a twist curve) and perform an invalid curve attack.

- 2. The second attack uses the fact that the implementation checks for an invalid point. The attacker injects faults during this verification to corrupt and therefore bypass it. After successfully bypassing the check, the attacker performs the first attack.

- 3. Finally, the last attack uses fault injection during point duplication and performs a differential analysis through these faults. This attack works similarly to the attack employed in the RSA + CRT described in Algorithm 2.4.

Higher-order attacks require capturing more data from side channels to retrieve the desired secret information. Suppose an attack on a given algorithm that needs to obtain or change x operations to be successful (i.e. first-order attack). Another attack that needs to obtain or change about  $n \cdot x$  operations in the same algorithm by, for example,

inserting redundancy into the algorithm is called an attack of order n. Compared to their first proposal, the second attack of Biehl et al. [12] is an example of a second-order attack, since it needs to inject faults in the check phase and provide an invalid point.

Countermeasures against fault injections are always challenging, as preventing an attacker from trying to mount an attack is impossible. However, the attack can be made more demanding to succeed. A typical barrier against fault injection attacks is hiding sensitive hardware information as much as possible. These barriers can be built by encrypting the main memory and employing purposeful noises to make it difficult to read the bus. Moreover, one can enhance the metal layers to be a passive shield, add filters or security sensors such as power, time, light, and temperature, and wire the meshes to act as an active shield [66].

Computational barriers via software are also possible by performing several operations that lead to the same point and comparing the results. Alternatively, the inverse operation can be used to check if the result has not been changed, and both software countermeasures can be used concurrently. Nevertheless, second and higher-order attacks are still highly probable to succeed [12].

# Chapter 3

# DRAM Memory

Dynamic Random-Access Memory (DRAM) is the main memory in most computational systems. DRAMs are composed of memory cells, each having a capacitor responsible for holding a bit of information. Due to the capacitor's nature, the DRAM uses a process called refresh that updates memory cells frequently to preserve their charge and recover the stored logical bit.

In the computer system's, the main memory is critical to maintain its performance growth and technology scaling benefits. Lim et al. [63] showed that the number of processor cores in a computer doubles every two years, whereas the amount of DRAM memory doubles every three years. Thus, the memory capacity per core is affected by around 30% every two years, and even worse regarding memory bandwidth since the number of pins in a physical memory is limited and can not grow indefinitely. Figure 3.1, extracted from the work of Lim et al. [63], shows a projection for the growth in the number of processor cores and memory capacity over the past years.

Figure 3.1: On average, the memory capacity per processor core is supposed to decrease 30% every two years [63].

A system's main memory must scale in size, technology, efficiency, cost, and algorithms

management to preserve performance even with its capacity growing slower than the number of processor cores. For this to be successful, many challenges need to be addressed since memory technology needs to handle multi-core accesses, data-intensive applications, and different technologies like GPUs<sup>1</sup>, mobile, among others.

This chapter is organized as follows. Section 3.1 shows details about the DRAM architecture, including DRAM cell information, construction materials, and subsystem. Section 3.2 presents how the memory controller accesses DRAM information, detailing the required commands, the timings needed to execute each command, and the address mapping to distribute DRAM accesses.

## 3.1 DRAM Architecture

The following sections present the DRAM construction and architecture, showing its complexity in material selection, internal arrangement, and subsystem structure. For instance, each subsystem of the DRAM construction increments a specific size in its final configuration. Finally, an overview of the DRAM is presented to show its function and how large it can be.

## 3.1.1 DRAM Cells

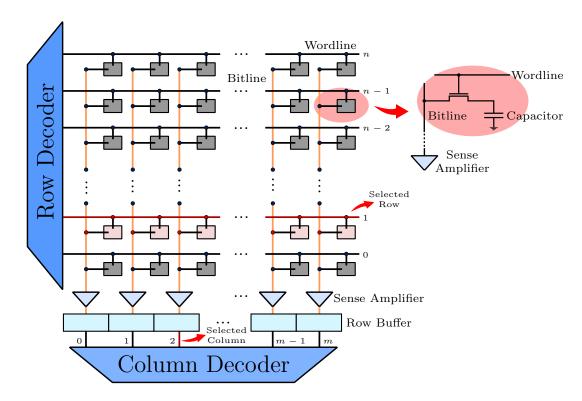

DRAM memories can be seen as a two-dimensional array of cells, each cell composed of a transistor and a capacitor, known as DRAM array [47]. Part of a physical address contains the row and column number in the DRAM array. The DRAM array is composed of DRAM rows; otherwise, it is known as a DRAM page.

The Row Decoder selects the DRAM page in the DRAM array by activating a specific wordline. The Sense Amplifier amplify the signal through bitlines and copies the result of the cells selected by the wordline to the Row Buffer. Then, the row's content is entirely moved to the Row Buffer. This process is said to leave that row open. Any read or write in some column is processed over the Column Decoder directly affecting the Row Buffer. The row is closed – that is, the data kept by the Row Buffer is returned to the original row – only by command [47]. This entire process is illustrated in Figure 3.2.

<sup>&</sup>lt;sup>1</sup>GPU, the acronym for Graphics Processing Unit.

Figure 3.2: Memory arrays with an expansion of the memory cells in red.

Example 3.1 presents a decoder from a physical address. For better understanding, combine Figure 3.2 and Example 3.1.

**Example 3.1** (Finding the physical address 0b000100001). Consider a DRAM array with five columns and four rows bits addresses respectively, in which the address 0bCCCCCRRRR represents the column 0bCCCCC and the row 0bRRRR. Then, the address 0b000100001 needs to activate the wordline 1 (0b0001), bring the entire row to the Row Buffer, and then select column 2 (0b00010).

## 3.1.2 DRAM Construction

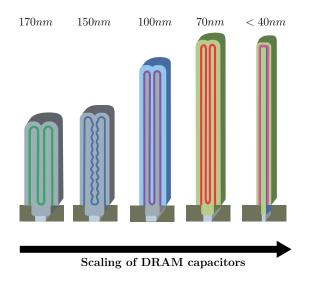

According to the International Technology Roadmap for Semiconductors (ITRS) [44], the scaling of the DRAM technology is ending since hardware projects will not be able to scale below a certain length in nanometers. The most used material for building a capacitor in DRAMs has a minimum distance between 5 and 7 nanometers of manufacturing concerning proper capacitance. If the capacitor has a higher capacitance, the data in memory does not need to be refreshed frequently because a more elevated capacitance implies the possibility of recovering the logic value of the capacitor, which is zero or one, even with a charge loss. On the other hand, a distance below 5 nanometers requires new materials for manufacturing the capacitor.

Recall that the capacitor is only a part of the memory cell, as shown in Figure 3.2. The entire DRAM cell can reach up to 28 nanometers using TiN (Titanium and Nitrogen), the currently most used material for building capacitors. In 2009, the ITRS [44] considered adopting other materials for 20 nanometers. From 2019 to 2024 the DRAM memories will be made it in 20 nanometers [45, Section 8.2]. Kim et al [52] claimed that will

be really challenging for further scaling toward 10 nanometers and DRAM may end at approximately 15 nanometer technology due to the capacitor constraints. The Figure 3.3 shows the evolution of the DRAM capacitors scaling.

Figure 3.3: Scaling of DRAM capacitors over the years [53].

The time to access a transistor and capacitor based memory should be large enough to allow low leakage and high retention. However, creating a reliable sense amplifier is challenging since cell storage tends to reduce over time.

## 3.1.3 DRAM Subsystem

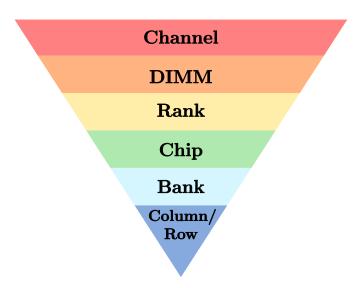

The DRAM subsystem is depicted in Figure 3.4, showing from its outer (channel) to the inner (column and row) composition. This section focuses on the DRAM Double Data Rate 4 (DDR4) standard [47], presenting each layer in a DRAM subsystem.

Figure 3.4: Memory subsystem organization from multiple modules to cells.

#### Column and Row

The DRAM row, or DRAM page, has a maximum of 18 physical pins for access. The maximum number of rows is  $2^{18} = 256$ K. Nowadays, the common number of rows is 32,768 or 32K – giving an 8GB memory. For reading and writing, a DRAM page is moved to the Row Buffer. Internally, the rows are split into small groups known as subarrays [55] to facilitate accesses on different rows of the bank. Therefore, each sub-array contains its Row Buffer that can then be copied to a global Row Buffer.

A DRAM column can be accessed from the Row Buffer and have a maximum of 10 physical pins for access. The maximum number of columns is  $2^{10} = 1$ K. Nowadays, a common number of columns is 1024 or 1K, and each column usually has 8 bits. With this information, it is possible to observe that a natural size for the Row Buffer is 8,192 bits or 8Kb.

#### Banks

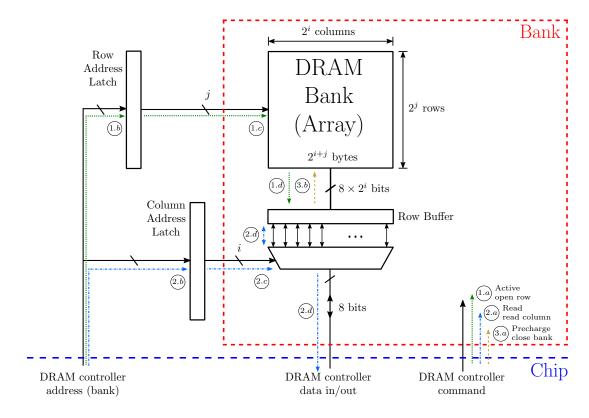

A DRAM bank is a series of bi-dimensional arrays of cells in the form of rows and columns. Additionally, the bank has a Row Decoder, a Column Decoder, and a Row Buffer, as illustrated in Figure 3.5. Usually, the bank has an 8-bit input and output. Considering the values mentioned previously, the bank is composed of a three-dimensional matrix of bits, having 8 bits in depth, 1K addresses through the columns, and 32K addresses in the rows.

## The Chip

A DRAM chip consists of multiple banks. The chip is composed of four bank groups, and each group has four banks. Resulting in 16 banks in a chip. The chip has a narrow interface providing from 4 bits to 16 bits per reading – the most common number is 8 bits.

Figure 3.5: A high-level overview of a DRAM chip consisting of multiple banks sharing addresses, data, and command buses. Memory bank – array, row address, column address and sense amplifiers.

#### The Rank

The DRAM rank comprises multiple chips operating together by a single interface. All chips composing a rank are controlled concurrently by sharing the address and command buses, but each is provided with different data information. The rank has three physical pins to be selected, so the maximum number of ranks is eight. A typical number of chips in a rank is eight, and each chip in this configuration provides 8 bits, resulting in 64-bit wide data. Recall that a bank's standard number for the Row Buffer is 8Kb. However, as a rank opens a row in a bank on each chip, it is possible to consider a larger Row Buffer of  $8 \times 8Kb = 8KB$ , or 8,192 bytes.

## The Dual Inline Memory Module

The Dual Inline Memory Module (DIMM), also called a module, consists of one or more ranks. The terminology dual inline came from the front and back pins of the module. In DDR4's case, there are 144 pins in the front and 144 pins in the back, apart from the Error Correction Code (ECC). A DIMM composed of ranks with 8 chips and providing 8 bits per chip has the advantage of high capacity and flexibility for the memory controller since it does not need to deal with individual chips. However, it has at least one disadvantage, which is the granularity, because the access cannot retrieve less than the interface width [69]. Figure 3.6 shows the chip and rank location in a DRAM module, allowing the visualization of the memory structure from the chip to the DIMM.

Figure 3.6: DDR4's DIMM without Error-Correcting Code (ECC). The figure shows the front of the modulo and half of the pins.

## The Channel

The DRAM channel has one or more DIMMs. Each channel needs a different memory controller from the CPU [69]. The typical number of DIMMs per channel is two. This information can be retrieved from the processor and motherboard.

**Example 3.2** (16GB DDR4 laptop). Consider a laptop with one channel and two DDR4 slots, each having two DIMMs of 8GB. Each DIMM has 2 ranks having 8 chips. Note that each rank has 4GB (8GB/2) and each chip has 512MB (4GB/8). Thus, the computation of the number of banks, columns, and rows of the 8GB DIMM proceeds as follows.

- Banks: Each chip has 4 bank groups and 4 banks per bank group, leading to 16 banks in total. A physical address selecting the bank group  $X \in \{1, 2, 3, 4\}$  and the bank  $Y \in \{1, 2, 3, 4\}$  from the group X will select the same bank on all eight chips. Then, the number of banks in the DIMM can have two possible values: 16 banks, from a physical address perspective, or  $2 \times 16 \times 8 = 256$  banks, considering all the chips in the two ranks. Thus, taking the physical address perspective, each bank has 32MB (512MB/16).

- Columns: The higher the number of columns, the greater the Row Buffer will be (Figure 3.5) and potentially larger the consecutive addresses that can be accessed. With 32MB remaining for each bank, it is possible to maximize the number of columns to 2<sup>10</sup> or, equivalently, 10 bits in the physical address. Thus, each column will have 1,024 bytes.

- Rows: The bus data needs to provide 64-bit wide data, assuming eight chips and each chip giving 8 bits. The entire bank has  $8 \times \#rows \times \#columns$  bits =  $32\text{MB} = 8 \times 32 \times 1,024 \times 1,024$  bits. Since the number of columns is 1,024 and each column provides 8 bits, the above computation ends up resulting in  $32 \times 1,024 = 32,768 = 2^{15}$  rows, which represents 15 bits in the physical address.

# 3.2 Memory Controller

The memory controller is complex, comprehending more than fifty time constraints for its proper functioning [47, 62]. Examples of constraints are Read to Read Delay (tRTR),

Read to Write Delay (tRTW), and Refresh Period (tREF). Beyond the constraints, the memory controller needs a minimum of bank conflicts, a good rank selection, and knowing the open rows and refresh rate to avoid loss of information and save energy. Moreover, the controller still needs to maintain quality of service [62, 55].

Although having a high-level view of the system's memory, the memory controller needs to control some commands to prevent leaks to maintain reliability and security. DRAM and memory controllers, as known today, are unlikely to satisfy all requirements of capacity, bandwidth, and, especially, reliability and security [54]. Thus, rethinking the main memory system is necessary to fix DRAM issues and enable emerging technologies while satisfying all requirements.

## 3.2.1 Memory Controller Commands

Table 3.1 presents each memory controller command:

$\overline{\mathrm{BG}_{1-0}}$  $A_{12}$  $A_{10}$  $\mathbf{A}_{11}$ Command Abbreviation  $\overline{\mathrm{CS}}$  $\overline{\text{ACT}}$  $\mathbf{A}_{13}$  $\mathbf{A}_{9-0}$  $\mathbf{A}_{17}$  $BA_{1-0}$  $\overline{CAS}$  $\overline{\mathrm{WE}}$ Deselect DES Η Active ACT L Bank  $\mathbf{L}$ Row Address (Row Opening) No Operation NOP L V Η V V V V ZQ Calibration ZQCL/ZQCS  $_{\rm L}$ V Η V Η Η L V V V Long V RD/RDA Burst Column Auto-Η V Н L Н V Read RDS4/RDAS4 Bank Chor Precharge Address RDS8/RDAS8 WR/WRA Burst Column Auto-Write WRS4/WRAS4 Bank Η V Η L Chop Precharge Address WRS8/WRAS8 Reserved for RFU V Н RFU L RFU L Η Future Use Precharge Η PREA L V Η V  $\mathbf{L}$ Η L V V V V All Banks Single Bank V PRE  $\mathbf{L}$ Bank Η V  $\mathbf{L}$ Η  $_{\rm L}$ V V  $_{\rm L}$ V Precharge V V Refresh REF  $_{\rm L}$ Η V  $\mathbf{L}$ L Η V V V V Mode Register MRS Н L Opcode Register Opcode Set

Table 3.1: DDR4 commands summarized [47].