#### Universidade Estadual de Campinas Instituto de Computação

#### Casio Pacheco Krebs

Integração e análise de desempenho de arquiteturas RISC-V paralelas

#### Casio Pacheco Krebs

## Integração e análise de desempenho de arquiteturas RISC-V paralelas

Dissertação apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação.

Orientador: Prof. Dr. Lucas Francisco Wanner Coorientador: Prof. Dr. Guido Costa Souza de Araújo

Este exemplar corresponde à versão final da Dissertação defendida por Casio Pacheco Krebs e orientada pelo Prof. Dr. Lucas Francisco Wanner.

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Krebs, Casio Pacheco, 1997-

K871i

Integração e análise de desempenho de arquiteturas RISC-V paralelas / Casio Pacheco Krebs. – Campinas, SP : [s.n.], 2023.

Orientador: Lucas Francisco Wanner.

Coorientador: Guido Costa Souza de Araújo.

Dissertação (mestrado) – Universidade Estadual de Campinas, Instituto de Computação.

- 1. Arquitetura de computador. 2. Processamento paralelo (Computadores).

- 3. Computação de alto desempenho. I. Wanner, Lucas Francisco, 1981-. II. Araújo, Guido Costa Souza de, 1962-. III. Universidade Estadual de Campinas. Instituto de Computação. IV. Título.

#### Informações Complementares

Título em outro idioma: Integration and performance analysis of parallel RISC-V

architectures

#### Palavras-chave em inglês:

Computer architecture

Parallel processing (Electronic computers)

High performance computing

**Área de concentração:** Ciência da Computação **Titulação:** Mestre em Ciência da Computação

Banca examinadora: Lucas Francisco Wanner Rodolfo Jardim de Azevedo

Mateus Beck Rutzig

Data de defesa: 03-04-2023

Programa de Pós-Graduação: Ciência da Computação

Identificação e informações acadêmicas do(a) aluno(a)

- ORCID do autor: https://orcid.org/0000-0003-1719-8546

- Currículo Lattes do autor: https://lattes.cnpq.br/4374078124009506

#### Universidade Estadual de Campinas Instituto de Computação

#### Casio Pacheco Krebs

## Integração e análise de desempenho de arquiteturas RISC-V paralelas

#### Banca Examinadora:

- Prof. Dr. Lucas Francisco Wanner Universidade Estadual de Campinas

- Prof. Dr. Rodolfo Jardim de Azevedo Universidade Estadual de Campinas

- Prof. Dr. Mateus Beck Rutzig Universidade Federal de Santa Maria

A ata da defesa, assinada pelos membros da Comissão Examinadora, consta no SIGA/Sistema de Fluxo de Dissertação/Tese e na Secretaria do Programa da Unidade.

Campinas, 03 de abril de 2023

### Resumo

O uso de arquiteturas vetoriais e matriciais tem o potencial de aceleração proporcional à quantidade de unidades de processamento primitiva e permitem reduzir a sobrecarga na cache de instruções. Neste cenário, acelerar rotinas de multiplicação e acumulação (MAC) sobre estruturas regulares, por meio do processamento paralelo de dados em estruturas de hardware dedicadas, tornou-se um objetivo desejado, tanto pela indústria, quanto pelo ambiente acadêmico. No entanto, a ativação dessas estruturas não são triviais, necessitando de intervenções por parte do programador no código base da aplicação, caso contrário, o código não estará atingindo o máximo de eficiência promovido pelo sistema. Neste trabalho, são investigados o coprocessador vetorial Hwacha e o acelerador matricial Gemmini, concomitantemente com o processador RISC-V superescalar BOOM. A fim de eliminar a dependência de intervenções no código base e do conhecimento das rotinas de ativação, a ferramenta de reescrita de código automática SMR foi estendida, a partir do desenvolvimento de novas bibliotecas, que resumem as rotinas de preparação e movimentação de dados, combinados com as instruções de ativação do Hwacha e do Gemmini, nos padrões de execução GEMV e GEMM. Com o uso da ferramenta SMR acordado com a plataforma Verilator, foi criado um ecossistema de simulação, onde o desempenho separado do Hwacha e do Gemmini foram analisados, e na sequência, comparados com o processador RISC-V BOOM, a partir de sete aplicações do conjunto de Álgebra Linear do benchmark Polybench. Com esse ecossistema de simulação, acreditamos disponibilizar uma ferramenta capaz de ativar essas estruturas de aceleração sem a necessidade de intervenções no código base da aplicação.

### Abstract

The use of vector and matrix architectures has the potential for acceleration proportional to the number of primitive processing units and allows reducing the overhead in the instruction cache. In this scenario, accelerating multiplication and accumulation (MAC) routines on regular structures, through parallel processing of data in dedicated hardware structures, has become a desired objective, both by industry and by the academic environment. However, the activation of these structures is not trivial, requiring interventions by the programmer in the base code of the application, otherwise the code will not be reaching the maximum efficiency promoted by the system. In this work, the Hwacha vector coprocessor and the Gemmini matrix accelerator are investigated, concomitantly with the BOOM superscalar RISC-V processor. In order to eliminate the dependency on interventions in the base code and knowledge of activation routines, the SMR automatic code rewriting tool was extended, starting with the development of new libraries, which summarize the preparation and data movement routines, combined with the Hwacha and Gemmini activation instructions in the GEMV and GEMM runtime patterns. With the use of the SMR tool agreed with the Verilator platform, a simulation ecosystem was created, where the separate performance of the Hwacha and the Gemmini were analyzed, and then compared with the RISC-V BOOM processor, from seven applications of the Linear Algebra set of the Polybench benchmark. With this simulation ecosystem, we believe we can provide a tool capable of activating these acceleration structures without the need for interventions in the application's base code.

## Lista de Figuras

| 2.1 2.2    | Código de multiplicação Matriz-Matriz                                                                                                                                                               | 15<br>16                        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 2.3<br>2.4 | Código de convolução 2D                                                                                                                                                                             | <ul><li>19</li><li>20</li></ul> |

| 3.1        | Formatos básicos de instrução RISC-V. Fonte [Waterman and Asanovic, 2019]                                                                                                                           | 23                              |

| 3.2        | Esquema do <i>pipeline</i> do processador Berkeley Out-of-Order Machine (BOOM) [Celio et al., 2021]                                                                                                 | 24                              |

| 3.3        | Exemplo de instruções antes e após a etapa de renomeação de registradores, para corrigir dependência de dados dos tipos $WAR$ e $WAW$                                                               | 26                              |

| 3.4<br>3.5 | Diagrama do Reorder Buffer de dois bancos                                                                                                                                                           | 27                              |

| 26         | face RoCC                                                                                                                                                                                           | 28<br>28                        |

| 3.6<br>3.7 | Visão geral do coprocessador Vetorial Hwacha                                                                                                                                                        | 30                              |

| 3.8        | Formatos das instruções da thread de trabalho [Lee et al., 2015]                                                                                                                                    | 32                              |

| 3.9        | Código de multiplicação entre vetores mapeados para o coprocessador Hwacha                                                                                                                          | 33                              |

| 3.10       | Visão geral do Acelerador Gemmini                                                                                                                                                                   | 34                              |

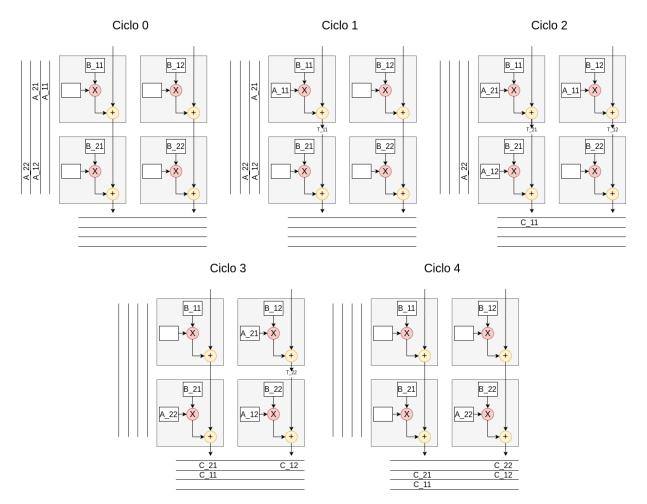

| 3.11       | Visão geral do SA e unidades MACs do Acelerador Gemmini Diagrama de execução de uma multiplicação de matrizes 2x2 (A × B = C), utilizando o fluxo estacionário de peso (WS), onde T_xx representa o | 35                              |

| 3.13       | resultado parcial transmitido                                                                                                                                                                       | 36                              |

| 3.14       | resultado parcial acumulado                                                                                                                                                                         | 37<br>39                        |

| 5.1<br>5.2 | Visão geral da estrutura de um código PAT                                                                                                                                                           | 47<br>47                        |

| 5.3        | Diagrama de execução de multiplicação Matriz-Matriz paralelizada pelo                                                                                                                               | 4.0                             |

| 5.4        | coprocessador vetorial Hwacha. Orientação Row-major                                                                                                                                                 | 49                              |

| 0.4        | processador vetorial Hwacha. Orientação Row-major                                                                                                                                                   | 50                              |

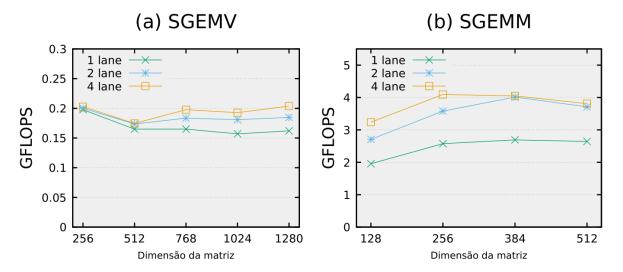

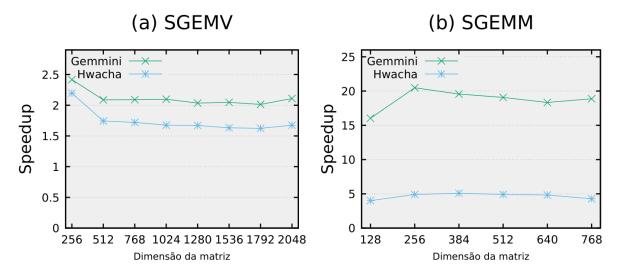

| 6.1<br>6.2 | Kernel para execução de operação GEMV. Linguagem Fortran Número de milhões de instruções de ponto flutuante por segundo executadas pelo Hwacha nas aplicações SGEMV e SGEMM, variando a quantidade  | 54                              |

|            | de Pistas Vetoriais                                                                                                                                                                                 | 56                              |

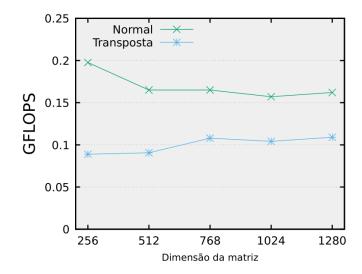

| 6.3 | Número de milhões de instruções de ponto flutuante por segundo na apli- |    |

|-----|-------------------------------------------------------------------------|----|

|     | cação SGEMV, utilizando orientação normal e transposta da matriz de     |    |

|     | entrada                                                                 | 57 |

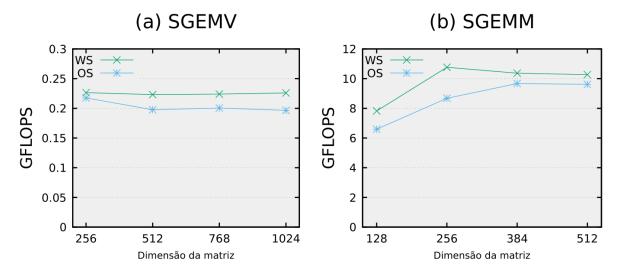

| 6.4 | Número de milhões de instruções de ponto flutuante por segundo executa- |    |

|     | das pelo Gemmini nas aplicações SGEMV e SGEMM, variando o fluxo de      |    |

|     | dados                                                                   | 58 |

| 6.5 | Desempenho da execução dos kernel SGEMM e SGEMV, quando executa-        |    |

|     | das pelo Hwacha e Gemmini, em comparação a execução pelo núcleo         | 59 |

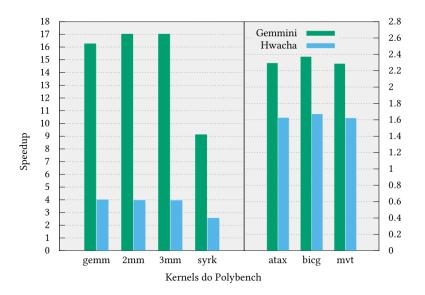

| 6.6 | Desempenho dos kernels do Polybench, quando executadas pelo Hwacha e    |    |

|     | Gemmini, em comparação a execução pelo núcleo                           | 59 |

|     |                                                                         |    |

## Sumário

| 1 | Intr                            | odução                                                                                                                                                               | 11                         |  |  |  |  |  |  |  |  |  |  |  |

|---|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 2 | Ref<br>2.1<br>2.2<br>2.3<br>2.4 | Multiplicação Matriz-Matriz  Multiplicação Matriz-Vetor  BLAS  Convolução  2.4.1 Aplicação em algoritmos  2.4.2 Conversão para chamadas blas  Aceleração em hardware | 16<br>17<br>18<br>18<br>20 |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Inte                            | Integração entre Processador e Aceleradores na Framework Chipyard 2                                                                                                  |                            |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1                             | RISC-V                                                                                                                                                               | 22                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2                             | Processador Berkeley Out-of-Order Machine (BOOM)                                                                                                                     | 23                         |  |  |  |  |  |  |  |  |  |  |  |

|   |                                 | 3.2.1 Predição de desvio                                                                                                                                             | 24                         |  |  |  |  |  |  |  |  |  |  |  |

|   |                                 | 3.2.2 Dependência de dados                                                                                                                                           |                            |  |  |  |  |  |  |  |  |  |  |  |

|   |                                 | 3.2.3 Escalonamento dinâmico de instruções                                                                                                                           |                            |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.3                             | Rocket Custom Coprocessor Interface (RoCC)                                                                                                                           | 27                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.4                             | Coprocessador Hwacha                                                                                                                                                 | 29                         |  |  |  |  |  |  |  |  |  |  |  |

|   |                                 | 3.4.1 Fluxo de dados                                                                                                                                                 |                            |  |  |  |  |  |  |  |  |  |  |  |

|   | 0.5                             | 3.4.2 Conjunto de instruções                                                                                                                                         |                            |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.5                             | Acelerador Gemmini                                                                                                                                                   |                            |  |  |  |  |  |  |  |  |  |  |  |

|   |                                 | 3.5.1 Array sistólico                                                                                                                                                |                            |  |  |  |  |  |  |  |  |  |  |  |

|   |                                 | 5.5.2 Sistema de controle                                                                                                                                            | 36                         |  |  |  |  |  |  |  |  |  |  |  |

| 4 | Tra                             | balhos relacionados                                                                                                                                                  | 41                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.1                             | Arquiteturas vetoriais                                                                                                                                               | 41                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.2                             | Arquiteturas sistólicas                                                                                                                                              |                            |  |  |  |  |  |  |  |  |  |  |  |

|   |                                 | 4.2.1 Projetos acadêmicos                                                                                                                                            |                            |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.3                             | Síntese dos Trabalhos Relacionados                                                                                                                                   | 44                         |  |  |  |  |  |  |  |  |  |  |  |

| 5 | Inte                            | egração no fluxo SMR                                                                                                                                                 | 46                         |  |  |  |  |  |  |  |  |  |  |  |

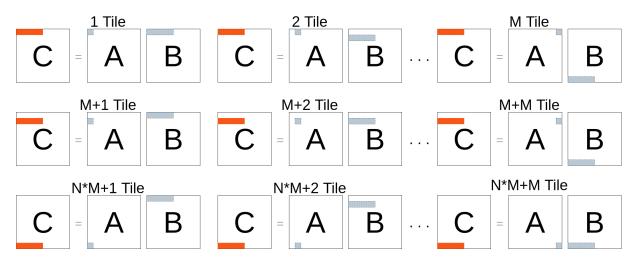

|   | 5.1                             | Matching and Rewriting (SMR)                                                                                                                                         | 46                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.2                             | Integração do Hwacha no SMR                                                                                                                                          | 48                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.3                             | Integração do Gemmini no SMR                                                                                                                                         | 50                         |  |  |  |  |  |  |  |  |  |  |  |

| 6 | Evo                             | olução e Avaliação das arquiteturas                                                                                                                                  | 52                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.1                             | Definição e configuração da plataforma de avaliação                                                                                                                  | 52                         |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.2                             | Aplicações                                                                                                                                                           | 53                         |  |  |  |  |  |  |  |  |  |  |  |

| 7 | Con | siderações Finais          |  |  |  |   |  |   |  |   |  |  |   |   |  | 62 |

|---|-----|----------------------------|--|--|--|---|--|---|--|---|--|--|---|---|--|----|

|   | 6.6 | Limitações Experimentais . |  |  |  | • |  | • |  | • |  |  | • | • |  | 60 |

|   | 6.5 | OpenBLAS                   |  |  |  |   |  |   |  |   |  |  |   |   |  | 58 |

|   | 6.4 | Avaliação Gemmini          |  |  |  |   |  |   |  |   |  |  |   |   |  | 57 |

|   | 6.3 | Avaliação Hwacha           |  |  |  |   |  |   |  |   |  |  |   |   |  | 55 |

|   |     |                            |  |  |  |   |  |   |  |   |  |  |   |   |  |    |

## Capítulo 1

## Introdução

Operações de multiplicação e acumulação (MAC) envolvendo estruturas regulares, como matrizes e vetores, compõem uma das mais fundamentais rotinas existentes em problemas computacionais. Aplicações envolvendo aprendizado de máquina, como redes neurais e redes convolucionais, podem ter operações com matrizes, comprometendo cerca de 70% do total de ciclos de computação durante a etapa de treinamento [Qin et al., 2020].

Como resultado da crescente demanda por essas rotinas, despertou um grande interesse em desenvolver bibliotecas [Oliphant, 2006; Xianyi and Kroeker, 2020] e algoritmos [Strassen et al., 1969; Coppersmith and Winograd, 1987; Williams, 2012, 2014] que buscam acelerar operações de multiplicação de Matriz-Matriz e Matriz-Vetor, também denominado de GEMM e GEMV, respectivamente. No entanto, por serem soluções baseadas em software, tendem a serem limitadas pelo núcleo, que precisa cumprir uma demanda de área e energia.

Historicamente, a melhoria da capacidade de processamento foi motivada principalmente pela Lei de Moore [Schaller, 1997] e pela escala de Dennard [Dennard et al., 1974]. Contudo, Dennard [Dennard et al., 2007] e outros pesquisadores já identificaram que os circuitos com transistores atingiram um ponto de fabricação crítico, onde o aumento exponencial da corrente de fuga impede o seguimento da escala original, gerando um aumento na densidade de potência e no custo energético total do *chip*. Nesse cenário, um alvo de pesquisa para continuar aumentando o desempenho, é o desenvolvimento de arquiteturas que buscam atender a um propósito específico da aplicação.

Uma prática comum dos projetistas é utilizar essas arquiteturas dedicadas como aceleradores dentro do *chip*, operando em conjunto com o processador de propósito geral, visando melhorar o desempenho final do *chip*, acelerando as rotinas extremamente intensivas em computação, e consequentemente, liberando o processador para continuar realizando computação útil. A implementação em hardware dessas rotinas, também permite avanços na eficiência energética dos projetos. Devido, não só pela simplificação das estruturas de controle e computação, mas também pela possibilidade de paralelização na etapa de processamento dos dados.

As aplicações que se baseiam em processamento de operações GEMM e GEMV, são alvo de otimizações por diversos projetos de aceleradores [Lee et al., 2015; Chen et al., 2016; Jouppi et al., 2017; Moss et al., 2018; Nvidia, 2017, 2018, 2020; Genc et al., 2021]. As arquiteturas desses aceleradores são baseadas no modelo de processamento Single Ins-

truction, Multiple Data (SIMD), onde a unidade de processamento primitiva é replicada, mas conectada a uma mesma unidade de controle, permitindo assim, que os aceleradores executem a mesma instrução sobre diferentes dados de forma simultânea.

Nesse intuito, apesar de terem o mesmo objeto, diversas topologias de aceleradores foram desenvolvidas, onde destacam-se as arquiteturas vetoriais [Lee et al., 2015; Lomont, 2011; Intel, 2022] e as sistólicas [Chen et al., 2016; Qin et al., 2020; Liu et al., 2020; Genc et al., 2021]. No entanto, a integração entre o *software* e o *hardware* é uma tarefa complexa no desenvolvimento dessas arquiteturas dedicadas.

Com um conjunto de instruções (ISA) que estende as instruções nativas do processador, é necessário por parte do programador, conhecimento prévio das funcionalidades do sistema para realizar adaptação do código base da aplicação para à sua ativação. Dessa forma, o desenvolvimento de bibliotecas de alto nível para facilitar seu uso, faz-se recomendado, uma vez que diferentes projetos podem estar presente em um mesmo SoC, e quando não acionadas, uma fração do hardware é subutilizada.

Nesse cenário, esta proposta buscou implementar e avaliar o coprocessador vetorial Hwacha [Lee et al., 2015] e o acelerador de processamento matricial Gemmini [Genc et al., 2021], visando disponibilizar diretrizes para os seus desenvolvimentos. Uma vantagem desses projetos, é a sua integração a framework de descrição de *hardware* Chipyard [Amid et al., 2020], que fornece ferramentas para implementar e avaliar componentes SoC (em português, sistema-em-um-chip). Por ter a natureza de código aberto, apresenta suporte a uma ampla variedade de processadores, incluindo o processador RISC-V superescalar BOOM [Zhao et al., 2020].

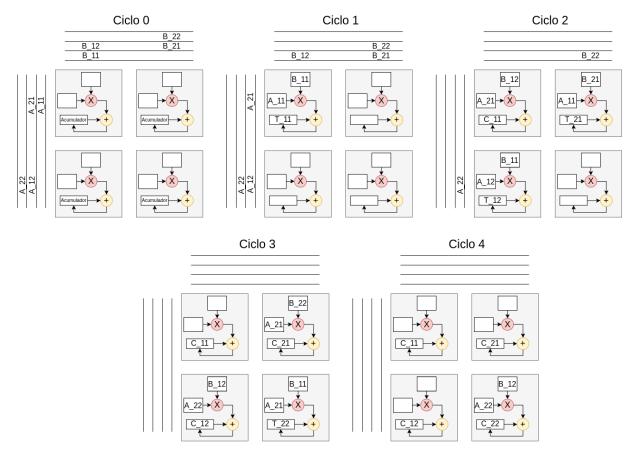

Visando oferecer suporte de alto nível, a interface de programação das arquiteturas, foi estendido no fluxo de compilação do Source Matching and Rewriting (SMR) [Espindola et al., 2023], uma ferramenta que realiza a correspondência e reescrita de código. Para esse fim, foi desenvolvido bibliotecas otimizadas que realizam as rotinas dessas arquiteturas, permitindo que o Hwacha e o Gemmini possam ser utilizados sem a necessidade de conhecimento do compilador, das funções de ativação, e principalmente, sem precisar modificar o código base da aplicação. Por fim, o desempenho das bibliotecas desenvolvidas foi comparado com a solução em software OpenBLAS [Xianyi and Kroeker, 2020], sendo executada no processador superescalar BOOM.

Sumarizando, este trabalho apresenta como principais contribuições:

- Preparação de um ambiente experimental para integração do acelerador Gemmini e do coprocessador Hwacha com um processador RISC-V superescalar, via interface RoCC (Rocket Custom Coprocessor Interface).

- Desenvolvimento de bibliotecas para integração e abstração das arquiteturas paralelas em aplicações de GEMV e GEMM.

- Integração das bibliotecas no fluxo do SMR, uma ferramenta para reescrita automática de código.

- Análise comparativa de desempenho entre o processador superescalar BOOM e arquiteturas vetoriais e matriciais.

Este texto está organizado conforme segue: o Capítulo 2, apresenta operações clássicas de multiplicação envolvendo vetores e matrizes, assim como aplicações com uso intensivo dessas operações; o Capítulo 3, apresenta os detalhes das arquiteturas dos componentes utilizados no estudo, como as arquiteturas de processamento paralelo e o processador de propósito geral; o Capítulo 4, apresenta trabalhos que englobam o contexto de aceleração por arquiteturas de processamento paralelo dedicada; no Capítulo 5, é apresentado o fluxo de processamento do SMR, combinado com a biblioteca de ativação das arquiteturas em seu fluxo; os resultados são explorados no Capítulo 6 e, a conclusão, é apresentada no Capítulo 7.

## Capítulo 2

### Referencial Teórico

#### 2.1 Multiplicação Matriz-Matriz

Descrito pela primeira vez pelo matemático James Joseph Sylvester, em 1812, e divulgado em 1858, pelo matemático Arthur Cayley [Cayley, 1858], o termo matriz é utilizado para representar uma estrutura de dados dispostas em linhas e colunas. Comumente, os dados de uma matriz são representados entre colchetes, como mostrado abaixo:

$$\begin{bmatrix} C_{0,0} & C_{0,1} & \dots & C_{0,N-1} \\ C_{1,0} & C_{1,1} & \dots & C_{1,N-1} \\ \vdots & \vdots & \ddots & \vdots \\ C_{M-1,0} & C_{M-1,1} & \dots & C_{M-1,N-1} \end{bmatrix} =$$

$$\begin{bmatrix} A_{0,0} & A_{0,1} & \dots & A_{0,K-1} \\ A_{1,0} & A_{1,1} & \dots & A_{1,K-1} \\ \vdots & \vdots & \ddots & \vdots \\ A_{M-1,0} & A_{M-1,1} & \dots & A_{M-1,K-1} \end{bmatrix} \cdot \begin{bmatrix} B_{0,0} & B_{0,1} & \dots & B_{0N-1} \\ B_{1,0} & B_{1,1} & \dots & B_{1N-1} \\ \vdots & \vdots & \ddots & \vdots \\ B_{K-1,0} & B_{K-1,1} & \dots & B_{K-1,N-1} \end{bmatrix}$$

A multiplicação entre duas matrizes é definida se, e somente se, o número de colunas da matriz **A** for igual ao número de linhas da matriz da **B**. Dessa forma, dada uma matriz **A** do tipo [MxK], onde M é o número de colunas e K o número de linhas, e uma matriz **B** do tipo [KxN], o produto da matriz **A** pela matriz **B** é a matriz **C** do tipo [MxN], onde o elemento (**i**,**j**) da matriz resultante é calculado pelo somatório dos produtos obtidos pela multiplicação dos elementos da linha **i**, da matriz **A**, pelos elementos da coluna **j**, da matriz **B**, como mostrado pela equação 2.1.

$$C_{i,j} = A_{i,0}B_{0,j} + A_{i,1}B_{0,j} + \dots + A_{i,K-1}B_{K-1,j} = \sum_{l=0}^{k-1} A_{i,l}B_{l,j}$$

(2.1)

Uma abordagem ingênua, para implementar a multiplicação entre matrizes, consiste em manter dois loops aninhados, a fim de acessar cada posição da matriz resultante, e um loop interno para se movimentar pela linha **i**, da matriz **A** e pela coluna **j**, da matriz **B**, realizando a multiplicação entre os elementos e a acumulação na posição de destino.

Essa implementação ingênua apresenta complexidade cúbica  $(\mathcal{O}(n^3))$ , e pode ser vista na Figura 2.1.

Figura 2.1: Código de multiplicação Matriz-Matriz

A generalização desse tipo de multiplicação recebe o termo GEMM (abreviação do ingles General Matrix Multiplication), e ocorre quando são adicionadas duas etapas de multiplicação por escalares. A primeira multiplica o resultado do produto da matriz A com a matriz B, com uma variável alpha, e a segunda, multiplica o valor previamente armazenado na matriz C com uma variável beta, com função de um acumulador. Apesar das multiplicações extras, a operação de GEMM apresenta complexidade cúbica. A função geral por ser vista na equação 2.2.

$$C := alpha * op(A) * op(B) + beta * C$$

(2.2)

Onde  $op(\mathbf{A})$  e  $op(\mathbf{B})$  representam as orientações de como as matrizes devem ser acessadas na multiplicação, isto é, sua orientação normal ou transposta. Desse modo, a operação pode ser executada de quatro formas, que podem ser vistas abaixo:

$$C = alpha * A * B + beta * C \tag{2.3}$$

$$C = alpha * A^t * B + beta * C (2.4)$$

$$C = alpha * A * B^t + beta * C (2.5)$$

$$C = alpha * A^t * B^t + beta * C (2.6)$$

Algumas termologias são empregadas para identificar o tipo das variáveis utilizadas nas operações, para isso, é adicionado uma letra no início da operação. Os termos empregados podem ser visualizados abaixo:

- S: número real de precisão simples;

- D: número real de precisão dupla;

- C: número complexo de precisão simples;

- Z: número complexo de precisão dupla.

#### 2.2 Multiplicação Matriz-Vetor

A partir da definição apresentada na seção anterior, um caso específico ocorre quando uma das matrizes apresenta apenas uma coluna, onde essa matriz recebe o nome de vetor. A multiplicação entre uma matriz do tipo [MxN] e um vetor de dimensão N, acarreta criação de um novo vetor de dimensão M, como mostrado abaixo:

$$\begin{bmatrix} y_0 \\ y_1 \\ y_2 \\ \vdots \\ y_{M-1} \end{bmatrix} = \begin{bmatrix} A_{0,0} & A_{0,1} & A_{0,2} & \dots & A_{0,N-1} \\ A_{1,0} & A_{1,1} & A_{1,2} & \dots & A_{1,N-1} \\ A_{2,0} & A_{2,1} & A_{2,2} & \dots & A_{2,N-1} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ A_{M-1,0} & A_{M-1,1} & A_{M-1,2} & \dots & A_{M-1,N-1} \end{bmatrix} \cdot \begin{bmatrix} x_0 \\ x_1 \\ x_2 \\ \vdots \\ x_{N-1} \end{bmatrix}$$

O produto Matriz-Vetor é definido se, e somente se, o número de colunas da matriz  $\bf A$  é igual ao número de linhas do vetor  $\bf x$ . Analogamente à multiplicação entre matrizes, o produto entre uma matriz e um vetor é calculado a partir do somatório dos produtos obtidos pela multiplicação dos elementos da linha  $\bf i$ , pelo elemento  $\bf i$  do vetor, conforme mostrado pela equação 2.7.

$$y_i = \sum_{j=0}^{N} A_{i,j} x_j (2.7)$$

Nesse caso, a abordagem ingênua consiste em implementar um loop que percorre as posições do vetor resultante, e um loop interno para se movimentar pela linha  $\mathbf{i}$ , da matriz  $\mathbf{A}$  e pelas posições do vetor  $\mathbf{x}$ , onde o resultado de cada multiplicação é acumulada na posição  $\mathbf{i}$ , no vetor de destino  $\mathbf{y}$ . Essa implementação ingênua pode ser vista na Figura 2.2.

```

for (int i = 0; i < M; i++){

y[i] = 0;

for (int j = 0; j < N; j++)

y[i] += A[i][j] * x[j];

}</pre>

```

Figura 2.2: Código de multiplicação Matriz-Vetor

A generalização desse tipo de multiplicação recebe o termo GEMV (abreviação do inglês *General Matrix-Vector Multiply*), e de forma análoga à operação GEMM, ocorre quando são adicionadas às etapas de multiplicação por *alpha* e *beta*. A função geral pode ser vista na equação 2.8.

$$y = alpha * op(A) * x + beta * y$$

(2.8)

#### 2.3 BLAS

As abordagens descritas anteriomente realizam a leitura sequencial dos elementos, em seguida multiplicam e, por fim, acumulam o resultado no endereço de destino até completarem todos os produtos parciais. Em arquiteturas que apresentam hierarquia de memória, com vários níveis de cache e memória DRAM desacoplada, as estratégias podem apresentar perda de desempenho à medida que as matrizes envolvidas cresçam o suficiente ao ponto de não poderem ser completamente alocadas na cache, uma vez que os níveis superiores apresentam uma maior latência de acesso. Dessa forma, para multiplicação com matrizes muito grandes, o desempenho fica limitado pela largura de banda da memória DRAM.

Visando disponibilizar abordagens mais eficientes para tais operações, bibliotecas como Basic Linear Algebra Subprograms (BLAS) [Lawson et al., 1979], e suas derivações como o GOTOBLAS2 [Center, 2020], o OpenBLAS [Xianyi and Kroeker, 2020] e o NVBLAS [NVI-DIA, 2022] foram desenvolvidas. Essas bibliotecas fornecem uma interface de programação, onde são disponibilizadas rotinas comuns de Algebra Linear, para realizar operações com vetores e matrizes. As bibliotecas visam aumentar a taxa de reutilização dos dados existentes na cache, otimizando assim os acessos à memória.

A implementação em baixo nível dessas bibliotecas, busca abstrair as rotinas em subrotinas menores, permitindo assim que os desenvolvedores se concentrem em otimizar um problema específico, visando atingir o algoritmo ótimo. Mas também, muitas bibliotecas buscaram otimizar as rotinas utilizando recursos de uma arquitetura específica, como por exemplo, ativando registradores vetoriais e programando os dados para aproveitarem instruções vetoriais, dessa forma, várias bibliotecas baseadas na interface BLAS são desenvolvidas com o foco em otimizar um conjunto de arquiteturas específicas.

Apesar do suporte restrito, a padronização das chamadas das funções permite que os usuários desenvolvam programas indiferentes à biblioteca BLAS que está sendo consumida, dessa forma, a etapa de migração para uma nova arquitetura necessita apenas da troca da biblioteca e não da modificação do código base.

A interface de programação fornecida pelas bibliotecas derivadas do BLAS, tem suas rotinas divididas em três conjuntos, denominados níveis, representando o grau de complexidades dos algoritmos. O nível 1, define o conjunto de funções de álgebra linear referentes à operações vetoriais que normalmente levam tempo linear  $(\mathcal{O}(n))$ , como, por exemplo, produtos escalares e adição vetorial, de formato:  $\mathbf{y} = \alpha \mathbf{x} + \mathbf{y}$ . O principal benefício apresentado pelas bibliotecas atuais, nesse nível, se deve à ativação das instruções de processamento vetorial.

As funções de nível 2 são destinadas às operações de Matriz-Vetor, onde se encontra a operação de GEMV, e de forma geral, apresentam tempo quadrático ( $\mathcal{O}(n^2)$ ). A implementação das rotinas desse nível podem ser apresentadas em termos de funções de nível 1. As funções de nível 3, são operações como o produto Matriz-Matriz, onde se encontra a operação de GEMM, e normalmente apresentam tempo cúbico ( $\mathcal{O}(n^3)$ ). Tais funções também podem ser implementadas a partir de chamadas das rotinas dos níveis inferiores.

Essas bibliotecas buscam acelerar a multiplicação de matrizes otimizando os acessos na cache, para isso, os dados das matrizes são divididos em blocos que possam ser alocados

nos diferentes níveis de cache, permitindo assim, que os blocos sejam processados com alta taxa de acerto das caches devido o reaproveitamento de dados. Por exemplo, uma multiplicação envolvendo matrizes de [1024x1024] pode ser dividida em uma sequência de multiplicações de matrizes de [64x64]. As operações de nível 2 também podem ser subdivididas, caso a matriz envolvida seja grande o suficiente.

#### 2.4 Convolução

Dentro do campo da matemática, o termo convolução é designado para representar a operação entre duas funções reais que produzem uma terceira função. Formalmente, convolução dentre uma função  $\mathbf{f} \colon \mathbb{R} \to \mathbb{R}$  e uma função  $\mathbf{g} \colon \mathbb{R} \to \mathbb{R}$ , resulta em uma função simbolizada por  $(\mathbf{f} * \mathbf{g})$ , denominado de mapa de recursos. No campo discreto, a convolução é caracterizada pela soma dos produtos parciais resultantes entre a superposição das duas funções após uma ser refletida em torno do eixo y e deslocada, conforme mostrado pela equação 2.9.

$$(f * g)[i] = \sum_{l=-\infty}^{\infty} f[l]g[i-l]$$

$$(2.9)$$

A equação 2.9 engloba operações com funções unidimensionais, nesse caso, a operação também pode ser chamada de convolução 1D. Caso as funções envolvidas se estendam ao longo de um campo bidimensional, a operação é denominada de convolução 2D. A equação 2.10 mostra a convolução bidimensional considerando uma matriz **A** de dimensão [MxN] e uma matriz **G**, de dimensão [RxP].

$$(A*G)[i,j] = \sum_{k=0}^{R-1} \sum_{l=0}^{P-1} A_{i-k,j-l} G_{k,l}$$

(2.10)

O algorítimo ingênuo para a execução de uma convolução 2D, consiste na implementação de quatro loops, dois loops aninhados para percorrer as posições na matriz  $\mathbf{A}$ , seguido por dois loops aninhados para percorrer as posições na matriz  $\mathbf{G}$ , realizando o processo de multiplicação dos dados sobrepostos e acumulações na posição de destino. Dessa forma, a aplicação ingênua da convolução 2D se torna uma operação muito cara computacionalmente, apresentando complexidade de  $\mathcal{O}(RxP)$  para cada posição da matriz  $\mathbf{A}$ . Essa implementação pode ser vista na Figura 2.3.

#### 2.4.1 Aplicação em algoritmos

No campo da Inteligência Artificial e de Aprendizado de Máquina, a Convolução 2D tem um papel fundamental na implementação dos algoritmos de processamento de imagens e, também, nos de inferência de Rede Neural Convolucional (CNN) [O'Shea and Nash, 2015], para fins de classificação e reconhecimento de padrões e objetos em imagens digitais.

Figura 2.3: Código de convolução 2D

Aplicações de processamento de imagens como o filtro de Sobel [Kanopoulos et al., 1988] e semelhantes, para detecção de borda, algoritmos de Realce como filtros passa-baixa e passa-alta, e também algoritmos de rotação, reflexão ou dimensionamento em imagens, denominadas de transformações afins, são implementadas a partir de uma pequena matriz carregada com o respectivo peso do filtro, denominada de máscara ou kernel.

Por exemplo, para a realização da detecção de borda a partir do filtro de Sobel, são aplicadas duas matrizes de kernel, uma para detecção de borda na vertical  $(G_x)$  e a outra para a horizontal  $(G_y)$ . O filtro usa kernels [3×3] que são convoluídos com a imagem original. Esses kernels podem ser visualizados abaixo:

$$G_x = \begin{bmatrix} -1 & 0 & +1 \\ -2 & 0 & +2 \\ -1 & 0 & +1 \end{bmatrix} \qquad G_y = \begin{bmatrix} +1 & +2 & +1 \\ 0 & 0 & 0 \\ -1 & -2 & -1 \end{bmatrix}$$

Para realizar o processamento, as duas matrizes de kernels são propagadas pela imagem, também representada por uma matriz, onde cada posição representa o valor do pixel. Os dados sobrepostos são convoluidos e o resultado das duas convoluções são ponderados, a fim de gerar o novo pixel da imagem final, que é classificado como parte de uma borda ou não. Dessa forma, para cada pixel são realizados dois procedimentos de convolução 2D.

CNN compõem um subconjunto da área de Aprendizado de Máquina, que atualmente está recebendo bastante destaque. Tradicionalmente, os algoritmos de CNN são compostos por três camadas: uma camada convolucional, uma camada de *pool* e uma camada totalmente conectada (FC).

A camada convolucional é o bloco de construção central de uma CNN, o qual é o responsável pelo maior volume computacional em uma CNN. Nessa camada é aplicado o kernel que representam o padrão do objeto desejável, movendo-se pelos pixels da imagem, verificando se o padrão está presente. Uma CNN pode ter várias camadas convolucionais, cada uma destinada a detectar os diferentes padrões da imagem de entrada. A saída final após todas as interações é conhecida como mapa de recursos. Por fim, a imagem é convertida em valores numéricos, o que permite que na camada FC, seja interpretada e extraído todos os padrões identificados na imagem.

#### 2.4.2 Conversão para chamadas blas

A convolução 2D pode ser reduzida para operações de multiplicação entre matrizes, dessa forma, os programadores podem otimizar os códigos a partir do uso de bibliotecas equivalentes ao BLAS. A ideia principal é transformar a imagem de entrada em uma representação baseada em "Coluna" de tal forma que as chamadas do GEMM para o produto escalar possam ser usadas para encontrar a saída final de convolução.

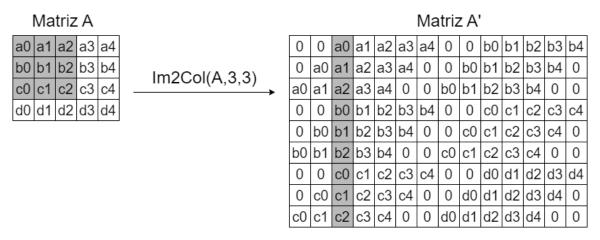

O algorítimo apresentado por Kumar Chellapilla, em 2006, denominado de im2col [Chellapilla et al., 2006], introduziu a ideia de expandir todas as janelas possíveis na memória e, em seguida, realizar o produto escalar como uma multiplicação de matrizes. Para esse fim, é identificada a quantidade de dados na matriz de kernel, que representa a altura da nova matriz de entrada, enquanto, a largura da nova matriz é igual ao número de vezes que o kernel de convolução desliza sobre a imagem de entrada. Os blocos de dados são tirados primeiro de cima para baixo e depois da esquerda para a direita da matriz.

Figura 2.4: Representação da matriz de entrada antes e após o procedimento de *im2col*, com kernel de dimensão [3x3]

Na Figura 2.4, é demonstrado o procedimento de im2col, com kernel de dimensão [3x3]. Após o procedimento, os pesos das matrizes de kernels são diretamente transformados em linhas. Por exemplo, para kernel de tamanho [3x3], dará uma nova matriz  $\mathbf{G}$  de tamanho [1x9], onde 3 x 3 = 9. Dessa forma, a nova matriz de entrada e o novo kernel podem ser processados diretamente com uma operação de GEMM.

Para convolução com apenas um kernel, o procedimento resultará em um vetor com dimensão equivalente ao número de vezes que o kernel de convolução desliza, sendo então convertido para as posições finais, com um procedimento análogo, denominado de *col2im*. As técnicas de *im2col* e *col2im* não melhoram a complexidade da convolução, mas melhora o desempenho em tempo real, pois permitem o uso de chamadas GEMM, às custas de mais uso de memória.

#### 2.5 Aceleração em hardware

As arquiteturas vetoriais e matriciais têm sido bastante difundidas pela sua capacidade de explorar o paralelismo na execução de aplicações MAC. Como apresentado na seção 2.4, a implementação de uma convolução 2D é muito cara computacionalmente, podendo atingir complexidade quadrática. Trabalhos como o Decaf [Donahue et al., 2014] mostram que as operações de convolução em uma CNN ocupam mais de 90% do tempo de execução, dessa forma, é um dos principais alvos para a aceleração de hardware.

As instruções para ativação dessas arquiteturas têm um potencial de aceleração proporcional a quantidades de unidades de processamento primitiva, além disso, permite reduzir a carga na cache de instruções e a pressão do pipeline, por reduzir a quantidade de instruções que precisam ser carregadas, decodificadas e emitidas.

O trabalho apresentado por Hasan Genc [Genc et al., 2021], mostra que quando a carga computacional é transferida para o acelerador, o núcleo presente no projeto tem menor impacto na computação da aplicação, permitindo assim, reduzir a área do projeto a partir da redução da complexidade do núcleo, mas preservando o desempenho da aplicação.

O mesmo trabalho apresenta uma arquitetura matricial de um array sistólico de 16x16 unidades de processamento (o conceito e funcionamento de um array sistólico será explorado na seção 3.5.1) acelerando CNNs. Quando aplicado na rede neural ResNet50, a arquitetura proposta atingiu um speedup de 189 vezes e quando aplicado na rede AlexNet, o speedup apresentado foi de 216 vezes, valores atingidos, acelerando apenas as operações de GEMM.

Apesar de permitir ganho de desempenho, o uso de estruturas para processamento paralelo apresentam desvantagens quando comparado com a execução tradicional [Cebrian et al., 2020]. Com o aumento da quantidade de unidades de processamento, aplicações originalmente limitadas pela ULA podem se tornar limitantes pela memória, uma vez que o paralelismo aumenta a pressão sobre o cache de dados e ao barramento de memória, pois exigem mais largura de banda para manter os PEs carregados.

## Capítulo 3

## Integração entre Processador e Aceleradores na Framework Chipyard

O ecossistema Chipyard é uma framework para descrição de hardware, de código aberto, que permite projetar, avaliar e por fim, implementar componentes SoC (em português, sistema-em-um-chip), baseados no conjunto de instruções (em inglês *Instruction set Architecture* (ISA)) RISC-V [Amid et al., 2020]. Desenvolvido pelo grupo Berkeley Architecture Research (BAR) da Universidade da Califórnia (UCB) a partir do projeto *Rocket Chip Gererator* [Asanović et al., 2016], é escrito na linguagem de descrição de hardware *Chisel*, uma extensão da linguagem de programação Scala, que fornece primitivas para descrever geradores de circuitos complexos e parametrizáveis, utilizados para sintetizar códigos Verilog.

O Chipyard oferece suporte aos geradores do processador superescalar BOOM [Zhao et al., 2020], do coprocessador Hwacha [Lee et al., 2015] e do acelerador Gemmini [Genc et al., 2021], que serão utilizados neste trabalho, além de estruturas periféricas, como interconexões e cache. Esses aceleradores são linkados com o núcleo BOOM a partir da interface de conexão RoCC, integrada ao ecossistema Chipyard.

#### 3.1 RISC-V

RISC-V é um conjunto de instruções (ISA) projetado para atender arquiteturas RISC (Computador de conjunto de instruções reduzidas, em português). Inicialmente, desenvolvido pelo grupo Berkeley Architecture Research [Waterman and Asanovic, 2019], foi planejado para ser utilizado como ferramenta de ensino, mas devido seu caráter aberto, chamou a atenção tanto da indústria quanto rede acadêmica, possibilitando o projeto de novas arquiteturas sem a necessidade de pagamento de royalties, permitindo a criação de diversos projetos [Conti et al., 2017; Flamand et al., 2018; Zhang et al., 2018; Pullini et al., 2019; Mashimo et al., 2019]. Atualmente é administrado pela RISC-V International, responsável por gerenciar a documentação de distribuição e definir alterações na ISA.

A base para o conjunto de instruções RISC-V é composto por quatro formatos de instruções, nominados de R-type, I-type, S-type e B-type, e duas variações com operador imediato, nominadas de U-type e J-type, que podem ser vistos na Figura 3.1. Esses forma-

| 31 30 25            | 24 $21$ $20$ | 19  | 15 14 12 | 2 11 8 7            | 6        | 0        |

|---------------------|--------------|-----|----------|---------------------|----------|----------|

| funct7              | rs2          | rs1 | funct3   | $\operatorname{rd}$ | opcod    | e R-type |

|                     |              |     |          |                     |          | _        |

| imm[1]              | 1:0]         | rs1 | funct3   | $_{ m rd}$          | opcod    | e I-type |

|                     |              |     |          |                     |          | _        |

| imm[11:5]           | rs2          | rs1 | funct3   | imm[4:0]            | opcod    | e S-type |

|                     |              |     |          |                     |          | _        |

| imm[12] $imm[10:5]$ | rs2          | rs1 | funct3   | imm[4:1] imm[1:     | 1] opcod | e B-type |

|                     |              | '   |          |                     |          | _        |

|                     | imm[31:12]   |     |          | $_{ m rd}$          | opcod    | e U-type |

|                     |              |     |          |                     | •        | _        |

| [imm[20]] $imm[10]$ | 0:1] imm[11] | imn | n[19:12] | $_{ m rd}$          | opcod    | e J-type |

Figura 3.1: Formatos básicos de instrução RISC-V. Fonte [Waterman and Asanovic, 2019]

tos foram definidos de forma que tanto os campos de registradores de origem (rs1 e rs2) quanto para o destino (rd) sejam mantidos na mesma posição para todos os formatos, a fim de simplificar o hardware de decodificação. Pela mesma forma, os imediatos foram colocados em direção aos bits mais significativos.

O RISC-V ISA apresenta duas variantes primárias referentes ao comprimento do espaço de endereçamento, representado pela letra "I", onde RV32I e RV64I representa o endereçamento de 32-bits ou 64-bits, respectivamente. Comumente o termo XLEN é utilizado para indicar o comprimento dos bits.

O formato rígido das instruções permitem que a ISA seja estendida com instruções específicas, a fim de reduzir o consumo de energia, tamanho do código ou o uso de memória [Waterman and Asanovic, 2019]. Algumas das extensões suportadas mais comuns podem ser vistas abaixo:

- M: Extensão padrão para multiplicação e divisão de inteiros;

- A: Extensão padrão para instruções atômicas;

- F: Extensão padrão para ponto flutuante de precisão simples;

- D: Extensão padrão para ponto flutuante de precisão dupla;

- C: Extensão padrão para instruções compactadas;

Por convenção, a letra "G"é utilizada para simplificar a combinação das extensões "IMAFD", dessa forma o termo RV64G, representa uma arquitetura de 64-bits com suporte as 4 extensões simultâneas.

## 3.2 Processador Berkeley Out-of-Order Machine (BOOM)

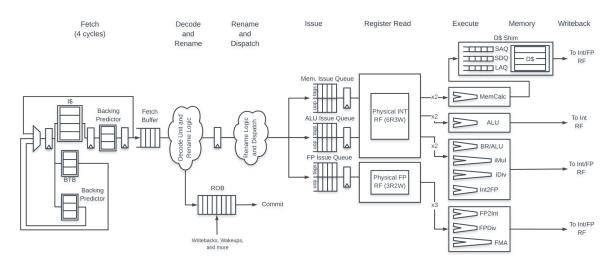

A plataforma Berkeley Out-of-Order Machine (BOOM) oferece um gerador de processador com execução fora de ordem [Zhao et al., 2020]. Atualmente em sua terceira versão, o núcleo BOOM conta com um estágio de previsão de desvio condicional, escalonamento

dinâmico de instruções, suporte a instruções RoCC e opera sobre o conjunto de instruções RV64GC. O projeto conta com uma execução dividida em 10 etapas, no entanto, algumas etapas são executados de forma paralela, resultando em um *pipeline* de 7 estágios de execuções e a etapa de *Commit* executada de forma assíncrona, que pode ser visto na Figura 3.2.

Na etapa de desenvolvimento, o gerador permite que sejam feitas mudanças em seus parâmetros estruturais, podendo modificar o tamanho da cache L1, número de registradores físicos e os estágios de *Fetch* e de *Decode* também podem ser configurados, modificando a quantidade de instruções lidas a partir da cache de instruções, e a quantidade de instruções decodificadas em um único ciclo, a fim de aumentar a quantidade de recursos do hardware utilizados.

Nos estágios de *Decode/Rename*, *Rename/Dispatch* e *Issue*, ocorre a execução do algoritmo de escalonamento dinâmico. Uma técnica baseada em *hardware* que realiza o despacho das instruções à medida que se tornam disponíveis os recursos para sua execução como, por exemplo, os dados de entrada, saída e unidades de execução. A fim de permitir que instruções que não tenham dependências de dados possam ser executadas paralelamente, garantindo assim, a consistência no resultado da execução do programa e apresentando ganho de desempenho.

Figura 3.2: Esquema do *pipeline* do processador Berkeley Out-of-Order Machine (BOOM) [Celio et al., 2021]

#### 3.2.1 Predição de desvio

A etapa de predição de desvio é implementada no estágio de Fetch, utilizando dois níveis de predição de desvio. O primeiro, denominado de preditor de próxima linha, chamado de NLP (do inglês Next-Line Predictor), opera com base em um Buffer de destino de ramificação (do inglês Branch Target Buffer (BTB)), onde é armazenado a decisão padrão com base no endereço nas instruções de desvios já analisadas, sendo que o objetivo desse nível de preditor é de manter um circuito de baixa complexidade que apresenta alta precisão para execução de laços de repetições.

Para execuções com desvios condicionados mais complexos, o BOOM utiliza um segundo preditor que supervisiona as decisões mantidas pelo BTB. Denominado de Preditor de Apoio (do inglês, *Backing Predictor* (BPD)), o modelo do preditor instanciado é definido pelo projetista, que pode escolher entre 5 preditores, como, por exemplo, o Gshare e o preditor de história global TAGE [Seznec, 2011]. Devido a maior complexidade do BPD, o *Fetch* prolonga-se por 4 ciclos, no entanto, é iniciado em paralelo ao BTB.

Quando uma instrução de desvio condicional é encaminhada a partir da cache de instruções, é realizado um acesso ao BTB em busca de uma correspondência, e em caso positivo, o valor do contador de programa é redirecionado após apenas 1 ciclo, e em caso de falha na busca, uma nova entrada é alocada no BTB para essa instrução e o BPD calibra a decisão salva no BTB no último ciclo do estágio *Fetch*.

#### 3.2.2 Dependência de dados

Dependência de dados caracterizam-se quando duas ou mais instruções ativas no pipeline realizam requisições ao mesmo registrador, gerando inconsistência no resultado caso sua execução seja realizada em ordem oposta. Tais dependências podem ser distribuídas em três classificações como Read after write (RAW), Write after read (WAR) e Write after write (WAW) [Hennessy and Patterson, 2017].

A primeira dependência refere-se a uma situação, em que uma determinada instrução requisita o dado de um registrador que ainda não foi gerado por outra instrução, realizando uma leitura incorreta do dado, pela primeira instrução. Servindo como base o exemplo na Figura 3.3, a instrução I2, só deverá ser despachada após a execução da instrução I1, devido à dependência no registrador R1. Enquanto que a segunda, refere-se a uma situação em que um registrador tem seu valor alterado antes que outra instrução possa acessá-lo, realizando uma leitura incorreta do dado, pela segunda instrução. No exemplo apresentado, a instrução I3, só deverá ser despachada após a execução da instrução I2, devido à dependência no registrador R2. Por fim, a terceira, refere-se a uma situação em que duas ou mais instruções tentam modificar o valor de um mesmo registrador, e caso a escrita seja feita na ordem inversa, o valor final do registrador será comprometido. No exemplo apresentado, a instrução I5, só deverá ser despachada após a execução da instrução I4, devido à dependência no registrador R3.

O primeiro computador a apresentar um algoritmo de escalonamento dinâmico para realizar o tratamento de *Data Hazard* foi o CDC 6600 [Thornton, 1980], por meio de uma estrutura de *Scoreboard*, onde os registradores de destino e de entrada eram armazenados em tabelas, no entanto, essa estrutura gerava muitos comandos de "stall" durante o tratamento de dependência para garantir a integridade dos dados. Anos mais tarde, a IBM anunciou o System/360 Model 91 [Anderson et al., 1967], como um competidor do CDC 6600, introduzindo o algorítimo de Tomasulo, onde apresentou o conceito de renomeação de registradores para prevenir *Data Hazard* dos tipos *WAR* e *WAW*, mapeando os registradores conflitantes para outros registradores físicos [Tomasulo, 1967]. Para facilitar a visualização da técnica de remapeando dos registradores, na Figura 3.3, pode ser vista a sequência de instruções criadas após a etapa de remapeamento.

```

1

I1:

R1

<= Lw address(0)

R1

<= Lw address(0)

2

I2:

R5

R2

+

R1

R5

R2

+

R1

<=

<=

3

R2

R7

R6

I3:

<=

R6

=>

*

R9

R8

R9

R3

<=

R8

<=

4

RЗ

<= R8 + R10

=>

<=

R8 +

R.10

```

Figura 3.3: Exemplo de instruções antes e após a etapa de renomeação de registradores, para corrigir dependência de dados dos tipos WAR e WAW

#### 3.2.3 Escalonamento dinâmico de instruções

Para realizar o processo de escalonamento dinâmico, o núcleo BOOM divide o processo em duas etapas, a primeira de renomeação de registradores e a segunda de despacho dinâmico. Para realizar o processo de renomeação de registradores, o núcleo apresenta projeto design de "renomeação explícita", onde mantém: um banco de registro físico (em inglês, Physical Register File (PRF)), responsável por armazenar explicitamente os nomes dos registradores físicos direcionados para cada registrador lógico decodificado das instruções; tabelas de mapa de renomeação (abreviado em inglês, Map Tables), que mantém salvo o estado dos registradores mapeados para cada ramificação especulativa identificada; e por fim, duas tabelas, sendo que a primeira armazena os registradores físicos que não estão alocados, denominada de Freelist, enquanto que a segunda armazena os status dos registradores físicos, denominada de busy table.

Dessa forma, ao passar para o estágio de Decode, a controladora realiza uma requisição de endereçamento para cada registrador vinculado à instrução a ser decodificada. No caso dos registradores de origem é realizado uma requisição ao PRF, buscando a TAG do registrador físico na Map Table da ramificação correspondente. No caso do registrador de destino, a fim de eliminar qualquer dependência de dados, sempre é realizado uma requisição no Freelist solicitando uma realocação do registrador, dessa forma todas as instruções que tenham o registrador rd ativo, acarretará em uma modificação no Map Table. Devido ao formato rígido das instruções do padrão RV64G ISA, os Map Table podem ser acessados durante o estágio de Decode, isso permite que seja combinado com o estágio de Rename.

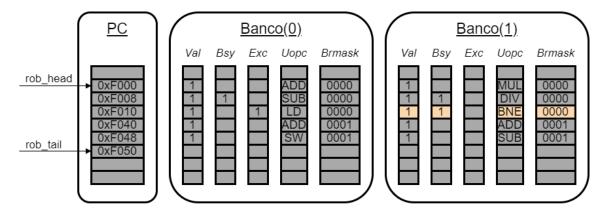

O processo de despacho dinâmico, realizado nos estágios de *Dispatch* e *Issue*, é responsável por analisar as instruções decodificadas, identificando os recursos e despachar para execução à medida que se tornam disponíveis. Para isso são mantidos um buffer de reordenamento (em inglês, *Reorder Buffer* (ROB)) e um *Issue Slot* para cada ramo de execução (inteiro, ponto flutuante ou acesso à memória).

O ROB opera similarmente a uma lista circular, como pode ser visto na Figura 3.4, e é composto principalmente pelo campo Val responsável por indicar se a informação na linha é válida, o campo Bsy, que indica que o registrado de destino se mantém bloqueado, isto é, a instrução ainda está em execução, o campo Exc, por indicar se é uma exceção, caso seja, quando chegar no topo do ROB é lançada a exceção no pipeline, o campo Uopc, que armazena o pacote contendo a instrução, os registradores de destino e origem, e por fim, Brmask que indica qual conjunto especulativo a instrução está associada.

Figura 3.4: Diagrama do Reorder Buffer de dois bancos

Quando uma instrução é emitida do estágio de *Decode/Rename*, é gerada uma nova entrada no ROB, que será adicionada no final da lista, indicado pelo endereço apontado por  $rob\_tail$ , onde o mesmo será realocado para o próximo endereço circular. Quando a instrução apontada por  $rob\_head$  não está mais ocupada, ela pode ser confirmada, ou seja, seu estado pode ser enviado para a memória. Após a emissão, a instrução é removida do ROB e o endereço  $rob\_head$  reajustado. Uma característica das instruções RoCC é o fato de não suportarem execução especulativa, dessa forma o projeto BOOM apenas emite para execução, quando estiverem na posição apontada pelo  $rob\_head$ .

Após ser gerada uma nova entrada no ROB, a instrução é repassada para a Unidade de Emissão (em inglês *Issue Unit*). Como pode ser visto na Figura 3.2, o núcleo BOOM particiona o *pipeline* em 3 ramos após as filas de emissões (em inglês *Issue Queues*), isolando a execução entre instruções de operandos inteiros, de ponto flutuante ou instruções de acesso à memória. Esses 3 *Issue Queues* operam de forma paralela, sendo responsáveis por reter as instruções até todos os operandos estiverem prontos e a unidade de execução livre. Cada *Queues* associa um bit a cada operando, para representar o estado do registrador, quando todos os bits de estados estiverem prontos, será emitido o sinal de solicitação ao componente de execução apropriado e aguardará ser emitido.

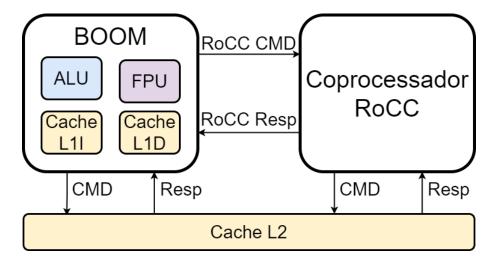

#### 3.3 Rocket Custom Coprocessor Interface (RoCC)

O Rocket Custom Coprocessor Interface (RoCC) é uma interface que estende o núcleo no SoC, permitindo uma comunicação desacoplada entre o núcleo e os coprocessadores [Asanović et al., 2016]. No caso específico desse trabalho desenvolvido, os coprocessadores atuaram como aceleradores, por apresentarem arquiteturas especializadas em multiplicação paralela. A interface RoCC proporciona uma conexão simples e direcional, e como pode ser visto na Figura 3.5, é composta principalmente por quatro canais de comunicação, dois para troca de dados entre o núcleo e o coprocessador, e dois canais para troca de dados entre o coprocessador e o sistema de memória.

A comunicação entre o núcleo e o coprocessador é baseada no algoritmo FIFO utilizando sinais pronto e válido. Dessa forma, para iniciar uma instrução de comando, o núcleo aciona o sinal válido e disponibiliza os dados, em seguida, espera até que o coprocessador eleve o sinal de pronto, onde a transferência é considerada aceita se ambos sinais

Figura 3.5: Diagrama do núcleo BOOM com um coprocessador conectados pela interface RoCC

estiverem no nível lógico 1, no mesmo ciclo de clock. Para a resposta do coprocessador é mantida uma estrutura análoga, mas em sentido oposto.

Uma vez que essa interface foi projetada para estender o núcleo Rocket, um processador de execução em ordem de *pipeline* clássico de 5 estágios, a resposta ocorre na mesma ordem das requisições recebidas. Como nesse trabalho desenvolvido será utilizado o núcleo BOOM, isso significa que, ao ser executado instruções de comando RoCC em sequência, terão suas emissões realizadas em ordem, pois o ROB só poderá confirmar e emitir a próxima instrução, a medida que identificar o comando de resposta por parte do coprocessador.

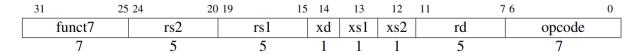

As instruções de comando apresentam comprimento de 32-bits e assemelham-se ao formato R-type, como mostrado na Figura 3.6, no entanto, os 3-bits do campo funct3 são reservados como Bits de validade, indicando se os registradores de origem e de destino devem ou não ser lidos. Para redirecionar a instrução para a porta RoCC, presente no núcleo, o campo opcode é fixado entre 0 e 3, valores reservados pelo RISC-V ISA para instruções customizadas [Waterman and Asanovic, 2019]. Como as instruções customizadas não são expostas através do GNU binutils assembler, é necessário descrever essa codificação diretamente em linhas de código assembly.

Figura 3.6: Formato da instrução de controle da interface RoCC

A interface de memória disponibilizada pelo RoCC, permite que o coprocessador se comunique diretamente com o barramento de memória, dentro do ecossistema Chipyard, o que representa uma conexão direta à cache L2, dessa forma evitando uma sobrecarga à controladora de memória do núcleo. Ao contrário das instruções de comando, as instruções de acesso à memória não podem ser confirmadas em ordem, pois o coprocessador não pode manter o cache aguardando, portanto, ele deve aceitar a resposta sem a possibilidade de

adiar a transação. Isso significa que o coprocessador deve aceitar todas as respostas da memória assim que a linha válida for alta. Com esta interface, a cache L2 conduz os dados e os sinais válidos e o coprocessador só precisa verificar se a linha válida está alta e aceitar os dados recebidos.

Além dos quatro canais principais, a interface RoCC também fornece canais para permitir funcionalidades avançadas como, por exemplo, conectar diretamente o *Page Table Walker* (PTW) ou a Unidade de Ponto Flutuante (FPU) do núcleo com o coprocessador, também pode permitir link direto com o sistema de memória externa. Esses canais extras fazem parte da chamada interface RoCC estendida.

#### 3.4 Coprocessador Hwacha

A plataforma Hwacha fornece um gerador de um coprocessador vetorial, parametrizável de código aberto[Lee et al., 2015]. O projeto é integrado ao ecossistema Chipyard, sendo desenvolvido com base em uma arquitetura de acesso à memória e execução desacopladas [Smith, 1984], permitindo assim que o Hwacha realize requisições ao barramento de memória em paralelo com a ativação da unidade de execução vetorial. A arquitetura foi projetada para permitir que o desenvolvedor configure, em tempo de compilação, a precisão da operação de ponto flutuante e a opcionalmente a execução predicada das instruções.

O coprocessador apresenta uma interface de *Frontend* independente, que realiza um estágio de *Fetch* das instruções vetoriais, fazendo com que o núcleo possa ativá-lo com apenas uma instrução, associada a um valor de contador de programa (PC) que aponta para o início do bloco de instruções vetoriais. O estágio de *Fetch* independente, permite que o núcleo continue realizando trabalho útil, enquanto o Hwacha esteja executando as operações vetoriais.

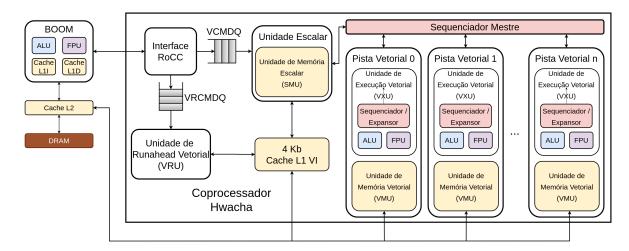

Como mostrado na Figura 3.7, o Hwacha é composto por 4 componentes principais, sendo uma cache L1 exclusiva, armazenando apenas as instruções vetoriais, uma Unidade de Runahead Vetorial (VRU), as unidades responsáveis por realizar a execução das operações primitivas, denominadas de Pistas Vetoriais, por fim, uma Unidade Escalar que realiza o estágio de Fetch das instruções vetoriais e, é responsável pela ativação das Pistas Vetoriais. A comunicação com o núcleo é realizada por uma unidade RoCC, que distribui as instruções para a Unidade Escalar e a VRU.

A estrutura das Pistas Vetoriais é dividida em dois componentes, a Unidade de Execução Vetorial (em inglês, Vector Execution Unit (VXU)), e a Unidade de Memória Vetorial (em inglês, Vector Memory Unit (VMU)). O VXU engloba os arquivos de registro vetorial (VRF) e predicado (PRF) e as unidades primitivas de processamento, separadas em unidades de meia precisão, precisão simples e dupla. O VXU é organizado em quatro bancos, onde cada banco é capaz de realizar uma operação primitiva e contém uma SRAM que forma uma parte do VRF e do PRF. Uma barra cruzada conecta os bancos às unidades funcionais, compartilhando as mesmas linhas de operando, predicado e resultado, enquanto que o VMU é responsável por controlar o movimento de dados entre a VXU e a cache L2, carregando o vetor e alimentando as unidades de processamento.

Figura 3.7: Visão geral do coprocessador Vetorial Hwacha.

#### 3.4.1 Fluxo de dados

O modelo de programação utilizado para a ativação do coprocessador, separa as instruções em dois blocos. O primeiro bloco denominado de *thread* de controle, é executado pelo núcleo, onde são mapeadas as instruções escalares, responsáveis pela etapa de configuração a Unidade Vetorial do Hwacha, além das instruções padrão do núcleo. O segundo, onde são mapeadas apenas as instruções de execução da Unidade Vetorial, é responsável pelo fluxo de execução e é denominado de *thread* de trabalho.

A unidade RoCC distribui as instruções da thread de controle proveniente do núcleo para a Unidade Escalar e a VRU, através do Vector Command Queue (VCMDQ) e do Vector Runahead Command Queue (VRCMDQ), respectivamente. Após ser decodificada a instrução para ativação, a Unidade Escalar inicia o estágio de Fetch das instruções vetoriais, a partir do valor de PC informado, continuando até atingir a instrução que sinaliza o final do bloco de busca.

No estágio de decode, a Unidade Escalar despacha as instruções para o sequenciador mestre, em seguida os dados dos vetores são despachados para cada Pista Vetorial. O sequenciador mestre emite operações para todas as pistas de forma síncrona, no entanto, cada pista é executada de forma desacoplada uma da outra. Em caso do comprimento vetor ser maior que o número de bancos para processamento, a Unidade de Memória Escalar (em inglês, Scalar Memory Unit (SMU)) irá carregar o vetor completo e salvar em registradores vetoriais, para isso é mantido um registrador de comprimento do vetor configurável que informa quantos dados devem ser carregados a partir da memória. Por fim, o sequenciador mestre irá separar os dados em blocos contínuos para serem despachados para as Pistas Vetoriais.

Um sequenciador interno é responsável por monitorar o progresso de cada operação ativa dentro de cada pista específica. Esse sequenciador realiza o despacho dinâmico das instruções, no entanto, ao contrário do núcleo BOOM, não apresenta uma etapa de realocação do registrador, mantendo as instruções paradas até que seus registradores estejam desocupados. Após liberado, as instruções seguem ao expansor, que encaminha as instruções para as respectivas unidades de execução. Por fim, os resultados são depositados em

filas, onde o sequenciador mestre monitora a retirada de forma assíncrona, e sequencializa os dados para serem salvos corretamente no registrador vetorial.

#### 3.4.2 Conjunto de instruções

As instruções da thread de controle Hwacha, são encaminhadas pelo núcleo, dessa forma, seguem o padrão de instruções de comando da interface RoCC, discutido na Seção 3.3. A API de controle é dividida em três tipos de instruções. O primeiro referente as instruções de Configuração do Vetor, responsável por configurar os parâmetros de execução do VXU. O segundo tipo é para as instruções de Movimento de Dados, que transferem vetores e valores escalares, entre a thread de controle e a thread de trabalho. Por fim, a instrução de Busca do Vetor, que informa o valor de PC que inicia a sequência das instruções da thread de trabalho.

São duas às instruções de Configuração do Vetor representadas pelos nomes VSETCFG e VSETVL. A primeira é responsável por configurar a Unidade Vetorial, alocando os registradores a serem utilizados na operação, para isso apenas o registrador rs1 é valido. O padrão utilizado no registrador rs1, pode ser visto abaixo.

- rs1[8:0]: Número de registradores de meia precisão;

- rs1[13:9]: Número de registradores predicados;

- rs1 [22:14]: Número de registradores de precisão simples;

- rs1[31:23]: Número de registradores de precisão dupla;

A instrução *VSETVL* configura o comprimento do vetor, para isso o registrador *rs1* é responsável por informar o valor requisitado, e o valor do comprimento do vetor alocado é salvo no registrador *rd*. Dessa forma, caso seja requisitado um valor maior que o disponível na arquitetura, o valor de retorno será menor que o requisitado, necessitando de uma nova chamada por parte do programador para processar os dados faltantes.

A instrução de Busca do Vetor é representada pelo nome vf nela, o endereço de PC referente ao bloco destinado às instruções vetoriais é transmitido pelo registrador apontado em rs1, e os valores campos funct7 e rd são combinados, formando um valor imediato de 12-bits, que após decodificado, é somado com o endereço informado para encontrar o endereço final.

Por fim, as instruções VMCS e VMCA compõem as instruções do tipo Movimento de Dados. A instrução VMCS move o conteúdo do registrador rs1 no processador de controle para um registrador de vetor compartilhado (vs). A instrução VMCA move o conteúdo do registrador rs1 no processador de controle para um registrador de endereço vetorial (va).

Como as instruções da *thread* de trabalho não são repassadas através da interface RoCC, elas não tem seu comprimento limitado, dessa forma apresentam formato de 64-bits. As instruções são divididas em 5 formatos, que podem ser visualizadas na Figura 3.8.

| 63 62 61 60 59 53 52 50 | 49 48 4 | 1 40 35 34 33 | 3 32 31 | 2I 23 | 16 15 12 | 11 0   |          |

|-------------------------|---------|---------------|---------|-------|----------|--------|----------|

| imm[31                  | :3]     | c2            | n rs1   | rd    | р        | opcode | VJ-type  |

|                         |         |               |         | '     |          |        |          |

| imm                     | [31:0]  |               | funct   | 3 rd  | funct4   | opcode | VU-type  |

|                         |         |               |         | •     | '        |        | •        |

| imm                     | [31:0]  |               | rs1     | rd    | funct4   | opcode | VI-type  |

|                         |         |               |         |       |          |        | •        |

| d 1 2 f funct7 funct3   | funct9  | rs2           | n rs1   | rd    | p        | opcode | VR-type  |

|                         |         |               |         |       |          |        |          |

| d 1 2 3 funct7 funct3   | f rs3   | rs2           | n rs1   | rd    | p        | opcode | VR4-type |

Figura 3.8: Formatos das instruções da thread de trabalho [Lee et al., 2015]

Como a ISA da *thread* de trabalho é composta por mais de 200 instruções, a fim de simplificar a apresentação, abaixo constam apenas as instruções que serão utilizadas nesse trabalho:

- vstop: Delimita o final do bloco de instruções vetoriais;

- vlw: Carrega um bloco da memória, a partir do endereço apontado por va, no registrador vetorial (vv) informado;

- vsw: Carrega os dados armazenado no registrador vetorial (vv) informado, no endereço de memória apontado por va;

- vfmadd.s: Realiza a multiplicação e acumulação dos dados armazenados no registrador vetorial (vv) informado, pelo escalar apontado em vs.

Na Figura 3.9 é apresentado um exemplo de código para a ativação do coprocessador Hwacha, onde é realizado o processo de multiplicação e acumulação de um vetor por um escalar, análogo ao apresentado na Seção 2.2. Para realizar a multiplicação, inicialmente a variável escalar é copiada para o registrador de vetor compartilhado (linha 1), dentro do escopo do loop, o comprimento do vetor é configurado (linha 3), e os endereços dos vetores carregados (linhas 4 e 5), por fim a instrução de Busca do Vetor é acionada para ativar o Hwacha (linha 6), encerrando a etapa de configuração. No bloco de instruções da thread de trabalho, os vetores são carregados a partir do sistema de memória e carregados nos registradores vetoriais (linhas 11 e 12), em seguida é realizado o procedimento de multiplicação e acumulação (linha 13), por fim, o resultado do registrador é salvo no sistema de memória (linha 14).

#### 3.5 Acelerador Gemmini

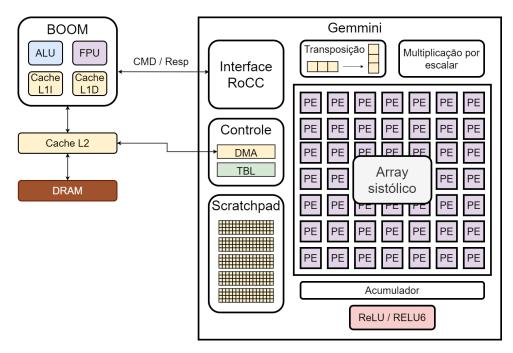

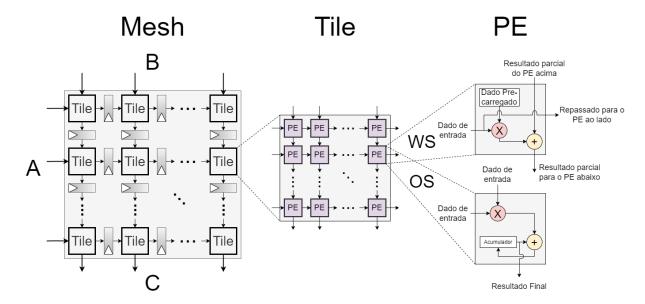

A plataforma Gemmini fornece um gerador full-stack de um acelerador para aplicações de Redes Neurais Profundas (em inglês, *Deep Neural Network* (DNN)), de código aberto, com total integração ao ecossistema Chipyard [Genc et al., 2021]. Foi desenvolvido baseado no modelo de Arrays Sistólicos (SA), onde cada elemento de processamento (PE) consegue executar operações de multiplicação e de acumulação (MAC) dos produtos parciais.

```

1

vmcs vs0, a1

// vs0 = a

2

Loop:

3

// a0 = DIM

vsetvl t0, a0

va0 = \mathcal{G}x[0]

vmca va0, a2

4

// va1 = &y[0]

vmca va1, a3

5

vf thread_trabalho

// Acionar Hwacha

6

7

sub a0, a0, t0

// a0 -= retorno do

vsetvl

8

bnez a0, Loop

9

thread_trabalho:

10

vlw vv0, va0

vv0 = x[i]

11

12

vlw vv1, va1

vv1 = y[i]

vs0, vv0, vv1

vfmadd.s vv1,

// vv1 += a*vv0;

13

vsw vv1 ,va1

y[i] = vv1

14

15

vstop

```

Figura 3.9: Código de multiplicação entre vetores mapeados para o coprocessador Hwacha

Como pode ser visto na Figura 3.10, o Gemmini apresenta um Scratchpad que armazena explicitamente blocos das matrizes de entrada e de saída do SA, a fim de facilitar a reutilização de dados, e um acumulador equipado com unidades somadoras, para reduzir a necessidade de escrita dos resultados parciais no Scratchpad. Ambas estruturas são implementadas em SRAM, a fim de prover alta largura de banda. O acelerador, também, inclui estruturas auxiliares capazes de realizar operação de transposição e de multiplicação por um escalar antes de carregar a matriz no SA, dessa forma, o Gemmini permite que sejam aceleradas operações de multiplicação de matrizes, de expressão C = alpha \* A \* B + beta \* D. Por fim, é oferecido suporte a funções de ativação como ReLU ou ReLU6, após a etapa de acumulação [Genc et al., 2021].

O gerador Gemmini inclui dois DMAs, um responsável por copiar as matrizes de entrada da cache L2 para os Scratchpad e outro, por mover a matriz resultante do Scratchpad para a cache L2. Ambos DMAs, operam com endereços virtuais e compartilham o acesso a um TLB para traduzi-los em endereços físicos. A fim de mascarar a latência de memórias de hierarquias inferiores, o acelerador permite que a movimentação de dados seja realizada em paralelo com a execução do SA, para isso, é implementado um ROB, análogo ao apresentado na Seção 3.2.3, responsável por garantir a resposta em ordem.

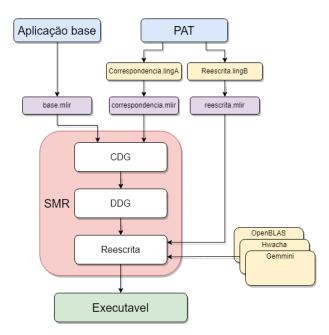

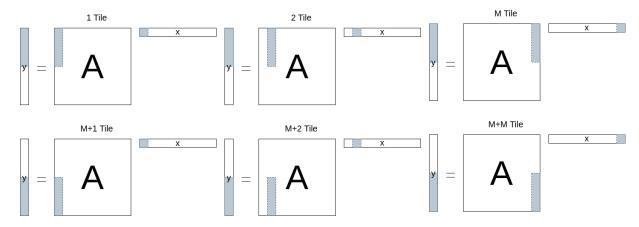

Para facilitar a ativação do acelerador, a plataforma oferece suporte a bibliotecas de baixo nível, escritas em linguagem C, fornecendo ao programador funções comuns em operação de DNN como multiplicação e adições de matrizes, convoluções (com ou sem pooling), entre outros. A API é gerada em conjunto com a arquitetura, baseado em seus parâmetros como, por exemplo, o tamanho do Scratchpad e do Acumulador, dimensão dos arrays sistólicos. A biblioteca também busca atender os casos onde as dimensões das matrizes são maiores que as dimensões dos SA, para isso, é realizado o processo de tiling da multiplicação das matrizes, visando otimizar a movimentação de dados entre a cache e o Scratchpad, maximizando a reutilização de dados.

Figura 3.10: Visão geral do Acelerador Gemmini

#### 3.5.1 Array sistólico