#### UNIVERSIDADE ESTADUAL DE CAMPINAS

Faculdade de Engenharia Elétrica e de Computação

#### RICARDO MALTIONE

# INTERFERÊNCIA DE RF EM CIRCUITOS INTEGRADOS DE POTÊNCIA INTELIGENTES COM ÊNFASE EM APLICAÇÕES INDUSTRIAIS, AUTOMOTIVAS E DE ENERGIA RENOVÁVEL

#### RICARDO MALTIONE

# INTERFERÊNCIA DE RF EM CIRCUITOS INTEGRADOS DE POTÊNCIA INTELIGENTES COM ÊNFASE EM APLICAÇÕES INDUSTRIAIS, AUTOMOTIVAS E DE ENERGIA RENOVÁVEL

Tese apresentada à Faculdade de Engenharia Elétrica e Computação da Universidade Estadual de Campinas como parte dos requisitos exigidos para a obtenção do título de Doutor em Engenharia Elétrica, na Área de Eletrônica, Optoeletrônica e, Microeletrônica.

Supervisor/Orientador: Prof. Dr. MARCELO GRADELLA VILLALVA

ESTE TRABALHO CORRESPONDE À VERSÃO FINAL DA TESE DEFENDIDA PELO ALUNO RICARDO MALTIONE, E ORIENTADA PELO PROF. DR. MARCELO GRADELLA VILLALVA

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca da Área de Engenharia e Arquitetura Rose Meire da Silva - CRB 8/5974

Maltione, Ricardo, 1963-

M299i

Interferência de RF em circuitos integrados de potência inteligentes com ênfase em aplicações industriais, automotivas e de energia renovável / Ricardo Maltione. – Campinas, SP: [s.n.], 2020.

Orientador: Marcelo Gradella Villalva.

Tese (doutorado) – Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Compatibilidade eletromagnética. 2. Rádio - Interferência. 3. Circuitos integrados. 4. Eletrônica de potência. 5. Inversores elétricos. I. Villalva, Marcelo Gradella, 1978-. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

#### Informações para Biblioteca Digital

**Título em outro idioma:** RF interference in smart power integrated circuits with emphasis in industrial, automotive and renewable energy applications

#### Palavras-chave em inglês:

Electromagnetic compatibility

Radio interference

Integrated circuits

Power electronics

**Electrical inverters**

Área de concentração: Eletrônica, Microeletrônica e Optoeletrônica

Titulação: Doutor em Engenharia Elétrica

Banca examinadora:

Marcelo Gradella Villalva [Orientador]

Luiz Carlos Kretly

Tárcio André dos Santos Barros Fernando Pinhabel Marafão

Elmer Pablo Tito Cari

Data de defesa: 04-08-2020

Programa de Pós-Graduação: Engenharia Elétrica

Identificação e informações acadêmicas do(a) aluno(a)

- ORCID do autor: https://orcid.org/0000-0002-2825-0250

- Currículo Lattes do autor: http://lattes.cnpq.br/0183328346386179

#### COMISSÃO EXAMINADORA - TESE DE DOUTORADO

Candidato: Ricardo Maltione RA 850901

Data da Defesa: 04 de agosto de 2020

Título da Tese: "Interferência de RF em circuitos integrados de potência inteligentes

com ênfase em aplicações industriais, automotivas e de energia renovável"

Prof. Dr. Marcelo Gradella Villalva (Presidente, FEEC/UNICAMP)

Prof. Dr. Luiz Carlos Kretly (FEEC/UNICAMP)

Prof. Dr. Tarcio André dos Santos Barros (FEM/UNICAMP)

Prof. Dr. Fernando Pinhabel Marafão (GASI/UNESP)

Prof. Dr. Elmer Pablo Tito Cari (EESC/USP)

A ata de defesa, com as respectivas assinaturas dos membros da Comissão Julgadora, encontra-se no SIGA (Sistema de Fluxo de Tese) e na secretaria de Pós-Graduação da Faculdade de Engenharia Elétrica e de Computação.

#### **DEDICATÓRIA**

Dedico este trabalho Ao meu pai Milton Maltione (in memoriam), minha mãe Darcy Apparecida Dias Maltione, meu irmão Claudio Maltione, e minha querida esposa Luciene Michella Baschiera

#### **AGRADECIMENTOS**

Agradeço ao meu orientador o Prof. Dr. Marcelo Gradella Villalva pela oportunidade de trabalhar com liberdade neste tema que faz parte da minha formação acadêmica e industrial, assim como o seu incentivo e apoio em desenvolvimentos conjuntos na área de Eletrônica de Potência e de Energia Renovável.

Agradeço ao Prof. Dr. Luiz Carlos Kretly pelo incentivo e apoio na área de compatibilidade eletromagnética e RF de micro-ondas envolvendo circuitos integrados, que levaram a execução deste trabalho.

Agradeço ao Prof. Dr. Carlos Alberto dos Reis Filho pelo aprendizado na área de microeletrônica e projeto de circuitos integrados analógicos.

Agradeço aos meus amigos da Motorola/Freescale/NXP, Magneti Marelli, CTI Renato Archer e Embraer Segurança e Defesa pela ajuda com a pesquisa, testes, discussões e sugestões.

Agradeço em particular ao Dr. Alfredo Olmos, Dr. André Villas Boas e o Eng. Eduardo Ribeiro da Silva pela parceria na pesquisa nesta temática, que culminou em várias publicações e patentes.

Agradeço também aos amigos do Laboratório de Potência e Fotovoltaico da Unicamp, ao Marcos V. G. dos Reis, Dante I. Narvaez e Hugo S. Moreira pela parceria no trabalho e em publicações.

Agradeço a AMS – Austria Mikro Systeme e XFAB pela assistência às informações e fabricação dos circuitos integrados via programas multiusuários (PMU, PMW).

Agradeço também ao programa CI Brasil pela oportunidade de fabricação de circuitos integrados por Design Houses, em particular a CTI Design House, CTI DSCH e DAPE.

Agradeço aos meus pais Milton e Darcy e meu irmão Claudio que sempre me incentivaram, e a minha esposa Luciene que sempre esteve ao meu lado em todas as horas desta jornada que culminou neste trabalho.

Agradeço também a todos aqueles que contribuíram de alguma forma para este trabalho e involuntariamente não foram aqui mencionados.

O presente trabalho foi realizado com apoio do CNPq, Conselho Nacional de Desenvolvimento Científico e Tecnológico - Brasil.

#### **RESUMO**

Este trabalho apresenta uma contribuição à pesquisa e desenvolvimento de circuitos integrados de potência inteligentes (*Smart Power*) robustos à interferência de RF (RFI) dedicados principalmente ao controle de conversores de energia de potência e inversores elétricos e projetados para atender padrões internacionais de compatibilidade eletromagnética (EMC).

O objetivo principal da pesquisa é apresentar uma nova metodologia de análise da susceptibilidade à interferência de RF (EMS), através de um projeto com maior robustez, analisando-se as principais técnicas para a sua mitigação, predição e simulação. São apresentados estudos teóricos sobre susceptibilidade em circuitos mistos (envolvendo analógicos, digitais e de potência), abordando-se o problema do efeito da interferência sobre circuitos não lineares para análises de pequenos e grandes sinais, com análises envolvendo Taylor, e Volterra-Wiener, dentre outras.

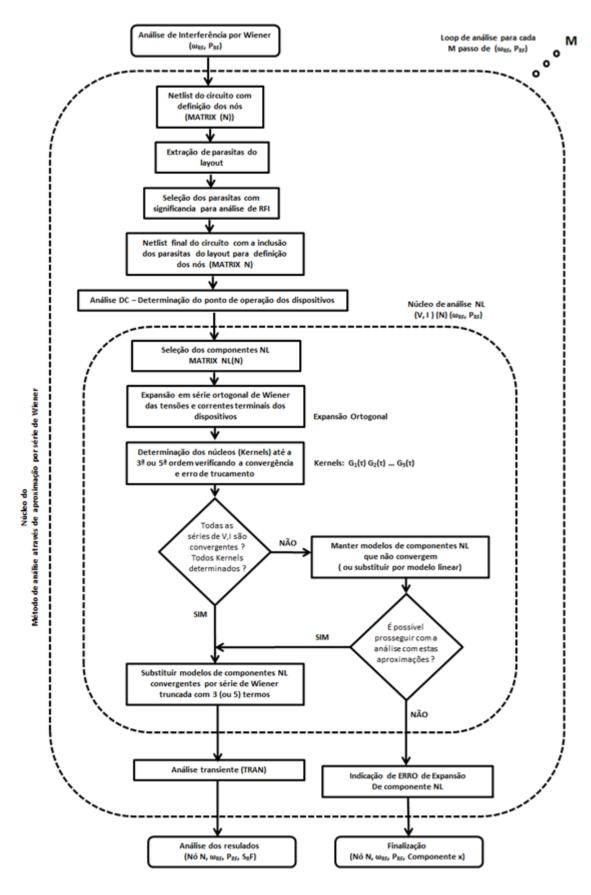

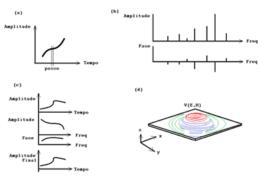

Como uma ferramenta de análise é apresentado um novo método de análise de interferência (interferência complexa) e seu algoritmo, permitindo uma rápida simulação e predição do estado final, permitindo ainda a introdução de efeitos não modelados ou disponíveis nos simuladores.

São apresentados resultados experimentais com testes de interferência de RF realizados em circuitos integrados de teste projetados em tecnologia CMOS 0.25μ, 0.35μ e 0.6μ das Foundries AMS e XFAB, além de testes com chaves de potência WBG.

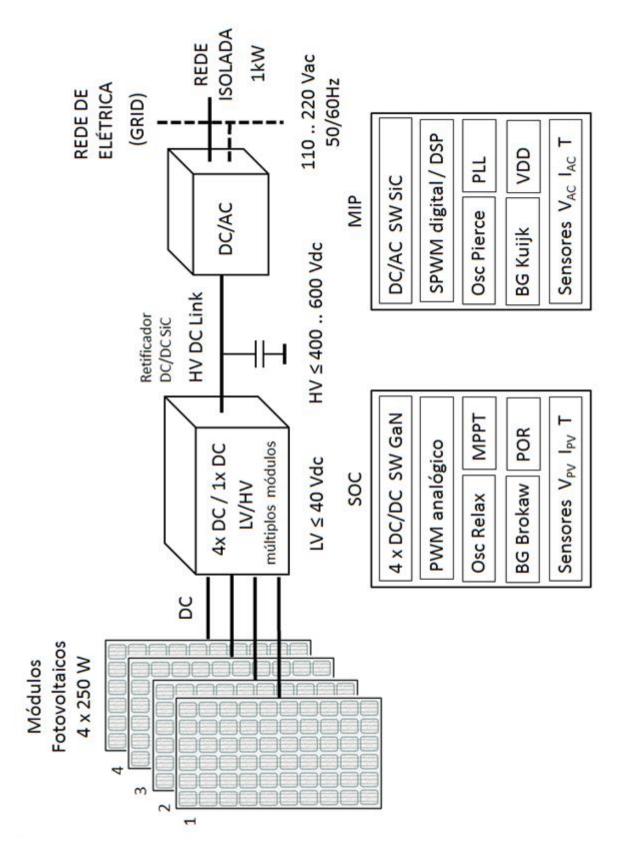

Para o estudo de interferência foram considerados vários estudos de caso, de circuitos *Smart Power*, incluindo um sistema inversor de 1kW usando chaves de potência SiC/GaN, sendo apresentados modelamentos, simulações e resultados de testes de interferência em laboratório usando a metodologia DPI, sendo proposto um novo método de teste, FRA-DPI.

Palavras-chave: Compatibilidade eletromagnética, interferência de rádio, circuitos integrados, eletrônica de potência, inversores elétricos.

#### **ABSTRACT**

This work presents a contribution to the research and development of robust smart power integrated circuits to the RF interference (RFI) mainly dedicated to control of energy power converts and electric inverters, designed to meet international standards for electromagnetic compatibility (EMC).

The main objective of the research is to present a new methodology of susceptibility analysis to RF interference (EMS), through a design with greater robustness, analyzing the main techniques for its mitigation, prediction and simulation. Theoretical studies on susceptibility in mixed circuits (involving analogue, digital and power) are presented, addressing the problem of the interference effect on nonlinear circuits for small and large signal analysis, with analysis involving Taylor and Volterra-Wiener, among others.

As an analysis tool, a new method of interference analysis (complex interference) and algorithm is presented, which allows the fast simulation and prediction of the final state, allowing yet the introduction of effects not modeled or available in the simulators.

Experimental results are presented with RF interference tests performed on integrated test circuits designed in CMOS  $0.25\mu$ ,  $0.35\mu$  and  $0.6\mu$  technology from Foundries AMS and XFAB, in addition to tests with WBG power switches.

For the interference study, several case studies of Smart Power circuits were considered, including a 1kW inverter system using SiC/GaN power switches, with modeling, simulations and results of interference tests in the laboratory using the DPI methodology, being presented a new test method, FRA-DPI.

Keywords: Electromagnetic compatibility, radio interference, integrated circuits, power electronics, electrical inverters.

#### LISTA DE ILUSTRAÇÕES

| Figura 1.1 – Aplicações na área industrial – forno de micro-ondas de estado sólido    | 23  |

|---------------------------------------------------------------------------------------|-----|

| Figura 1.2 – Aplicações no setor de transportes – veículos elétricos                  | 24  |

| Figura 1.3 – Aplicações na área automotiva – carro totalmente elétrico (EV)           | 25  |

| Figura 1.4 – Aplicação em energia renovável (solar fotovoltaica, sistema conectado)   |     |

| Figura 1.5 – Modelo clássico de interferência agressor - vítima                       |     |

| Figura 1.6 – Conceito de interferência de RF aplicado a um sistema de potência        |     |

| Figura 1.7 – Geração de ondas oscilatórias usando espirais de Knochcnhauer            |     |

| Figura 1.8 – Experiência de Hertz em 1888.                                            |     |

| Figura 1.9 – Classificação das fontes de interferência.                               |     |

| Figura 1.10 – Espectro de frequência das fontes de interferência.                     |     |

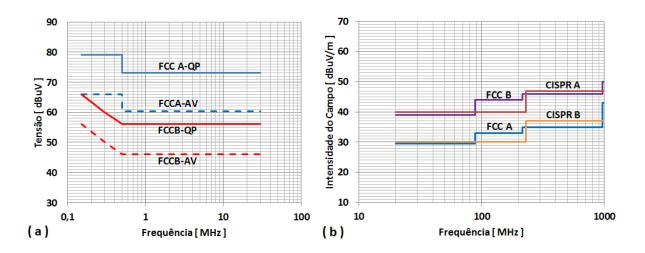

| Figura 1.11 – Limites de emissão para Normas FCC/CISPR                                |     |

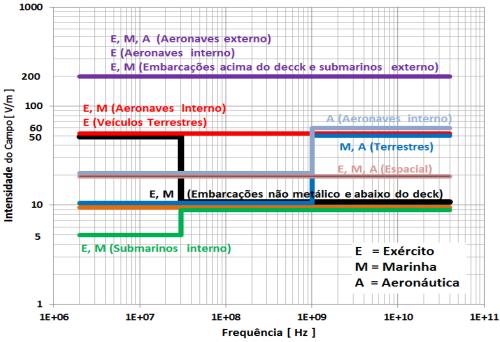

| Figura 1.12 – Limites de susceptibilidade radiada RS103 para Norma MIL STD 461F       |     |

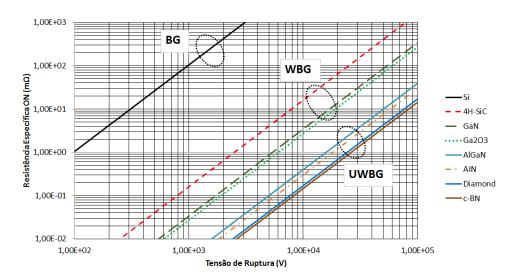

| Figura 2.1 – Figura de mérito de Baliga para semicondutores BG, WBG e UWBG            |     |

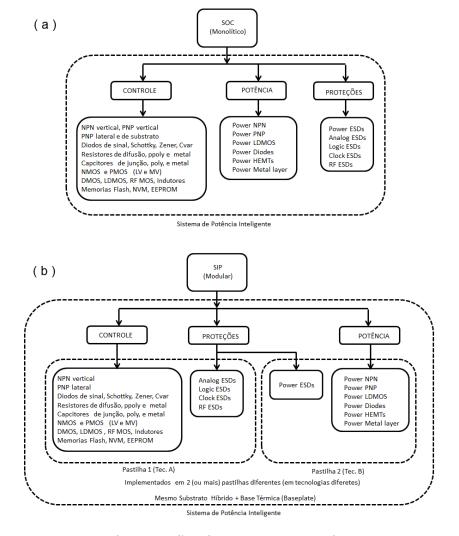

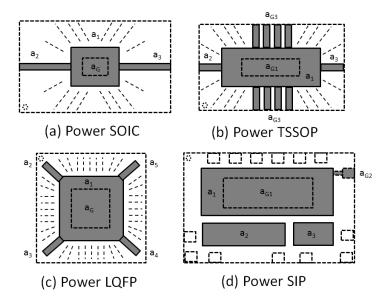

| Figura 2.2 – Implementações de circuitos integrados em Smart Power                    |     |

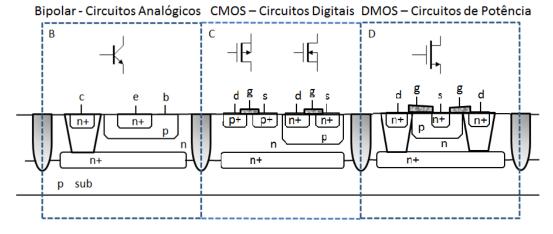

| Figura 2.3 – Tecnologia BCD Conceitual.                                               |     |

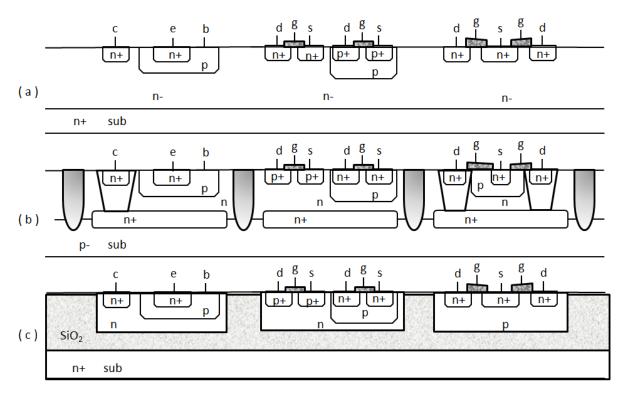

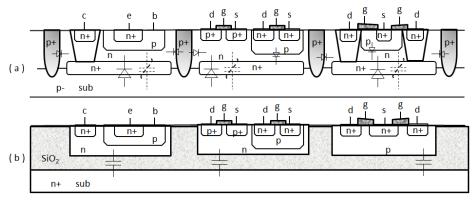

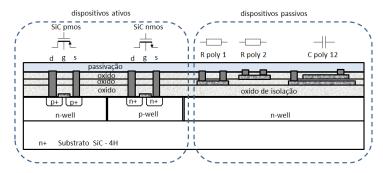

| Figura 2.4 – Técnicas de isolação de dispositivos em tecnologia BCD.                  |     |

| Figura 2.5 – Tecnologia Convencional versus SOI.                                      |     |

| Figura 2.6 – Tecnologia SiC CMOS para aplicações digitais e analógicas                |     |

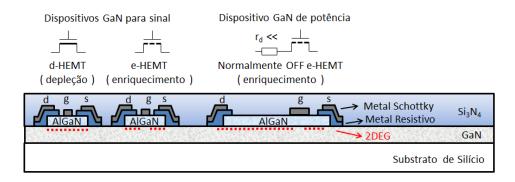

| Figura 2.7 – Tecnologia experimental GaN Smart Power (substrato de silício)           |     |

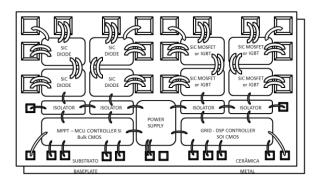

| Figura 2.8 – Exemplo conceitual de um módulo de potência MIP/SIP.                     |     |

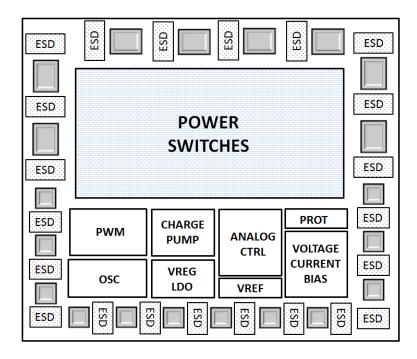

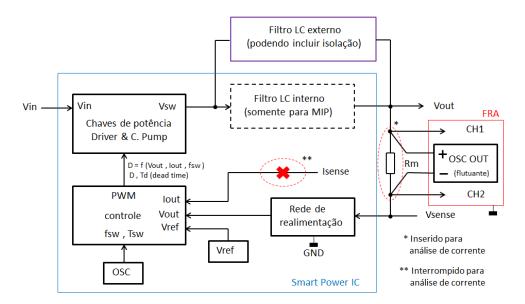

| Figura 2.9 – Regulador típico de tensão chaveada em Smart Power IC - analógico        |     |

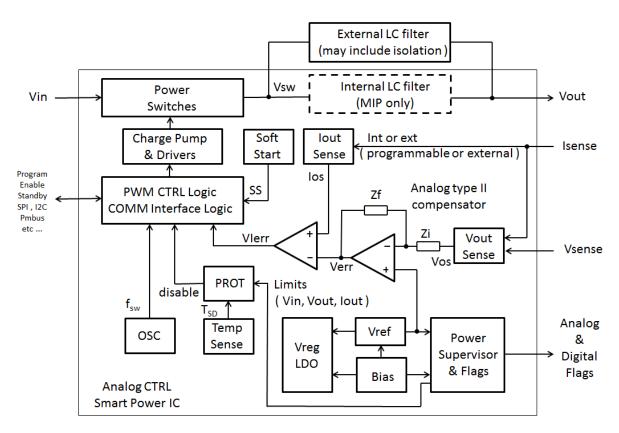

| Figura 2.10 – Diagrama de blocos típico do regulador de tensão chaveada - analógico   |     |

| Figura 2.11 – Regulador típico de tensão chaveada em Smart Power IC - digital         |     |

| Figura 2.12 – Diagrama de blocos típico do regulador de tensão chaveada – digital     |     |

| Figura 3.1 – Particionamento dos circuitos.                                           |     |

| Figura 3.2 – Algoritmo da análise de Resposta Transiente (TRAN).                      |     |

| Figura 3.3 – Métodos de integração.                                                   |     |

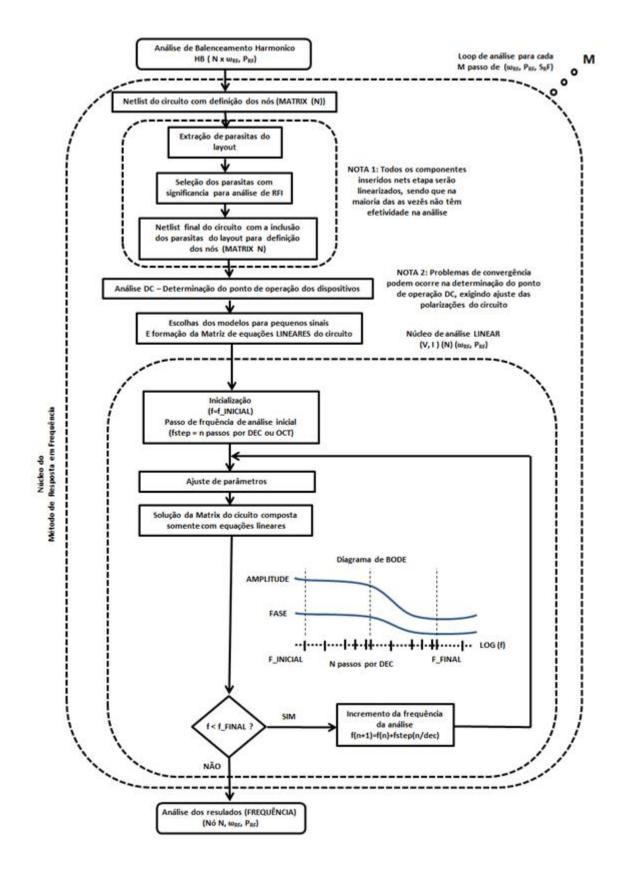

| Figura 3.4 – Algoritmo da análise de Resposta em Frequência (AC Spice).               |     |

|                                                                                       |     |

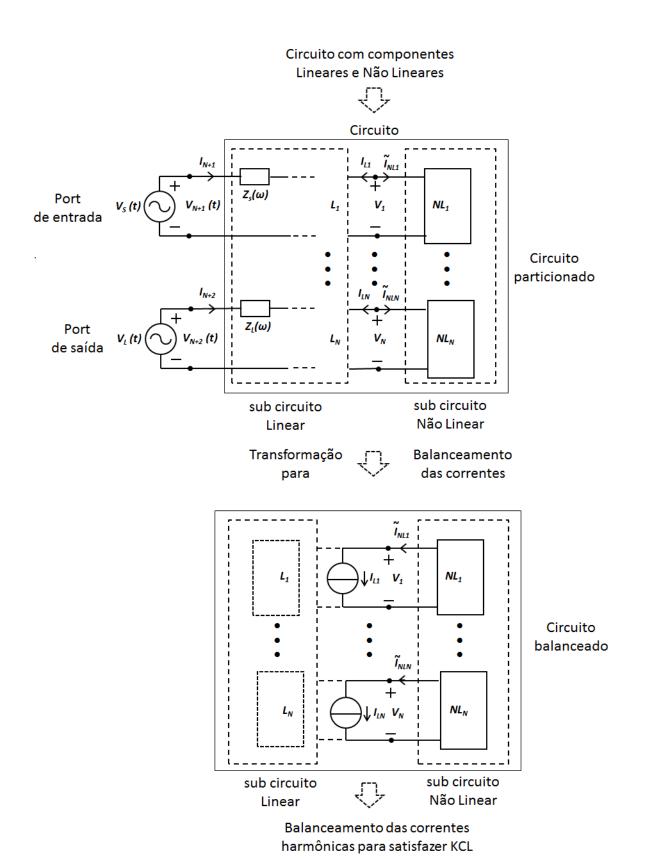

| Figura 3.5 – Particionamento do circuito em subcircuitos lineares e não lineares      |     |

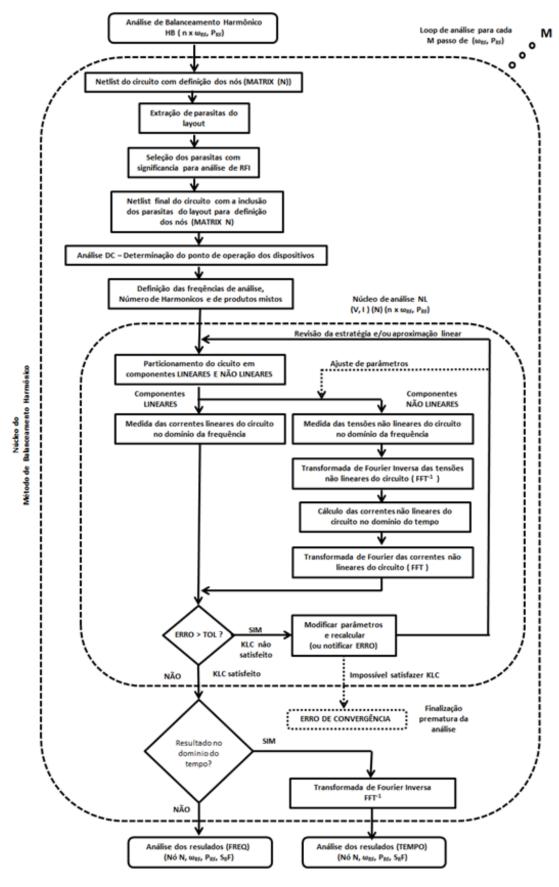

| Figura 3.6 – Algoritmo do método de Balanceamento Harmônico (HB)                      |     |

| Figura 3.7 – Classificação dos sistemas com relação à linearidade,                    |     |

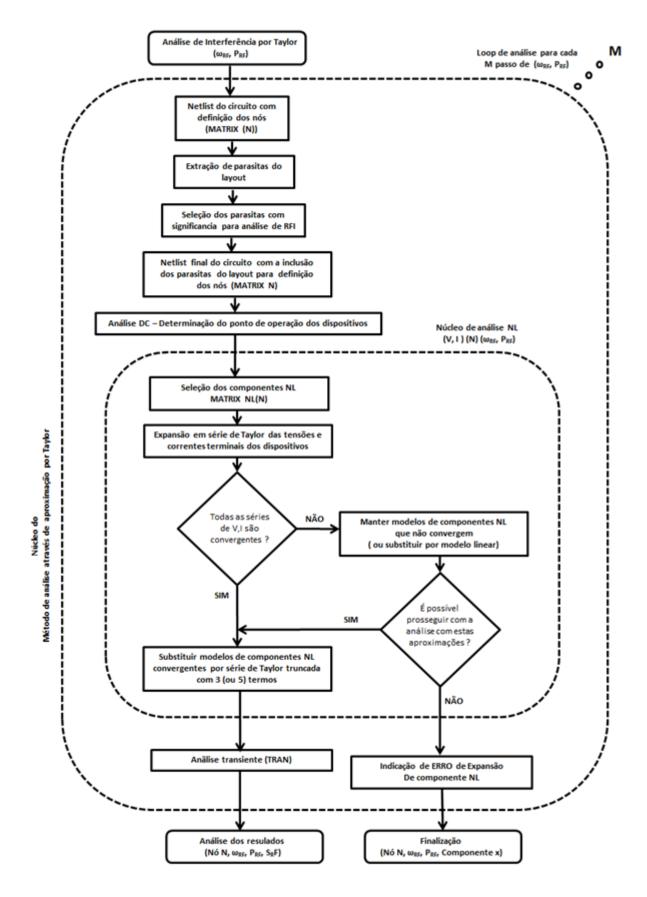

| Figura 3.8 – Fluxograma do método de análise por aproximação de Taylor.               |     |

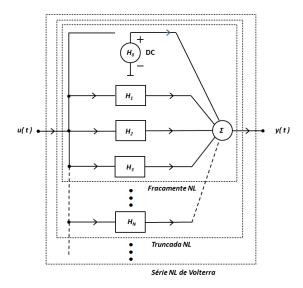

| Figura 3.9 – Interpretação da série de Volterra através da composição de seus núcleos |     |

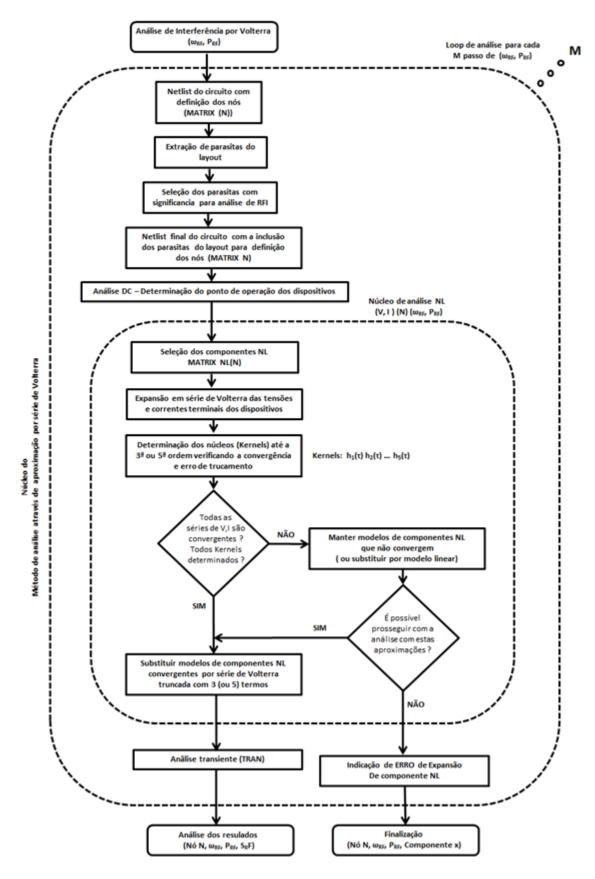

| Figura 3.10 – Fluxograma do método de análise por série de Volterra                   |     |

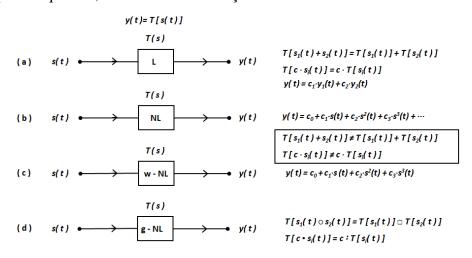

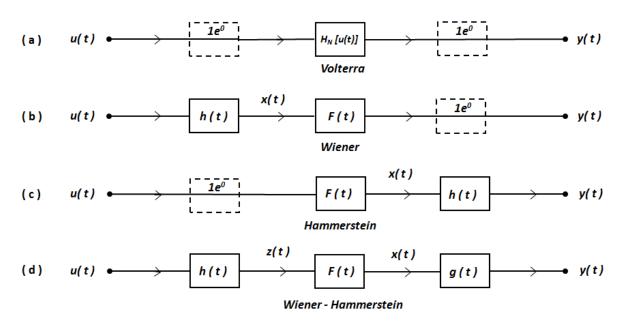

| Figura 3.11 – Interpretação da descrição de sistemas NL.                              |     |

| Figura 3.12 – Fluxograma do método de análise por série de Wiener.                    |     |

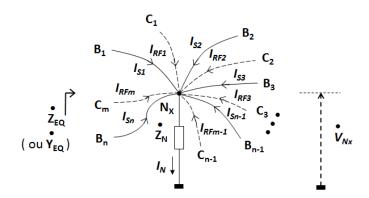

| Figura 3.13 – Caminhos de propagação da interferência entre os nós do circuito        |     |

| Figura 3.14 – Correntes e impedância complexa em um nó sob interferência              |     |

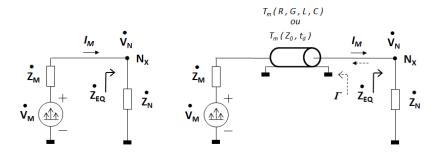

| Figura 3.15 – Determinação geral da impedância complexa em um nó do circuito          |     |

| Figura 3.16 – Determinação direta das correntes complexas em um nó do circuito        |     |

| Figura 3.17 – Esquema geral de um nó do circuito sobre interferência via TL           |     |

| Figura 3.18 – Esquema direto de um nó do circuito sobre interferência                 |     |

| Figura 3.19 – Estimação do valor médio via filtro passa baixa                         |     |

| Figura 3.20 – Circuito genérico sem interferência                                     |     |

| Figura 3.21 – Circuito genérico com interferência                                     |     |

| Figura 3.22 – Fluxograma do método de interferência complexa.                         |     |

| Figura 4.1 – Acoplamento de RFI via alimentações no modo tensão.                      |     |

| Figura 4.2 – Acoplamento de RFI via alimentações no modo corrente                     | 134 |

| Figura 4.3 – Faixa de excursão com acoplamento de RFI via alimentações                                                                                  | 134 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 4.4 – Diminuição da Faixa Dinâmica (DR) devido ao RFI                                                                                            | 136 |

| Figura 4.5 – Acoplamento de RFI via retificação (R <sub>N</sub> //C <sub>N</sub> ).                                                                     | 137 |

| Figura $4.6$ – Acoplamento de RFI no nó $N_x$ via retificação por junção                                                                                |     |

| Figura 4.7 – Acoplamento de RFI no nó $N_x$ via dispositivo parasita ativado                                                                            |     |

| Figura $4.8$ – Acoplamento capacitivo de RFI no nó $N_x$ (modo tensão)                                                                                  |     |

| Figura 4.9 – Acoplamento indutivo de RFI no nó $N_x$ (modo corrente)                                                                                    |     |

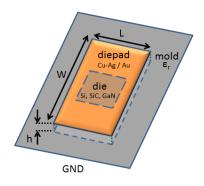

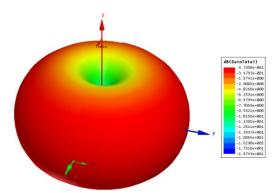

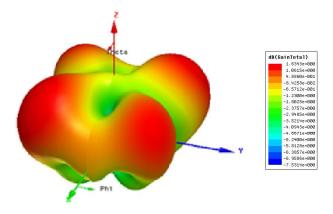

| Figura 4.10 – Modelamento do diepad/baseplate como antenas patch.                                                                                       |     |

| Figura 4.11 – Elementos do modelo do diepad como antena patch                                                                                           |     |

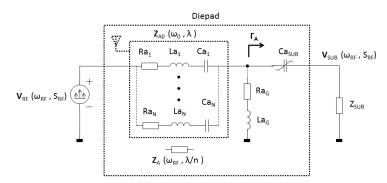

| Figura 4.12 – Modelamento elétrico proposto para o diepad/baseplate                                                                                     |     |

| Figura 4.13 – Modelamento em HFSS do diepad/baseplate.                                                                                                  |     |

| Figura 4.14 – Simulação HFSS do diepad SOIC de um circuito integrado de potência                                                                        |     |

| Figura 4.15 – Simulação HFSS do baseplate retangular de um módulo SiC de potência                                                                       |     |

| Figura 5.1 – Métodos de simulação/predição dos efeitos de RFI em circuitos complexos                                                                    |     |

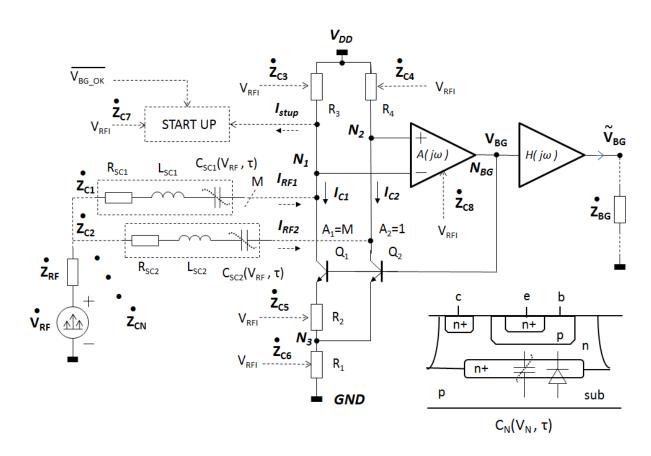

| Figura 5.2 – Circuito Inversor PV com 2 estágios para ilustração dos efeitos de RFI                                                                     |     |

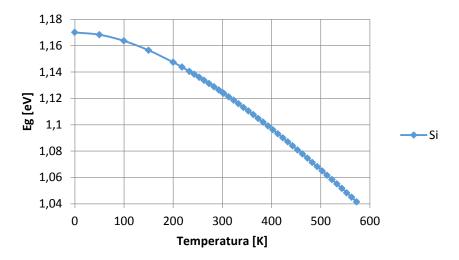

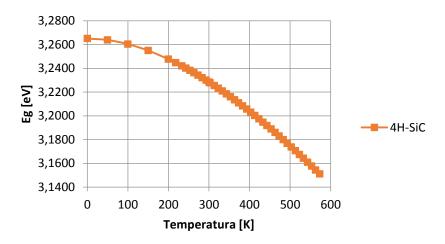

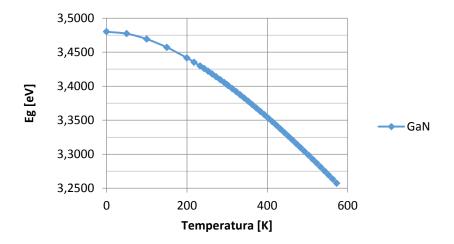

| Figura 5.3 – Função da energia do bandgap para o Si                                                                                                     |     |

| Figura 5.4 – Função da energia do bandgap para o SiC.                                                                                                   |     |

| Figura 5.5 – Função da energia do bandgap para o GaN.                                                                                                   |     |

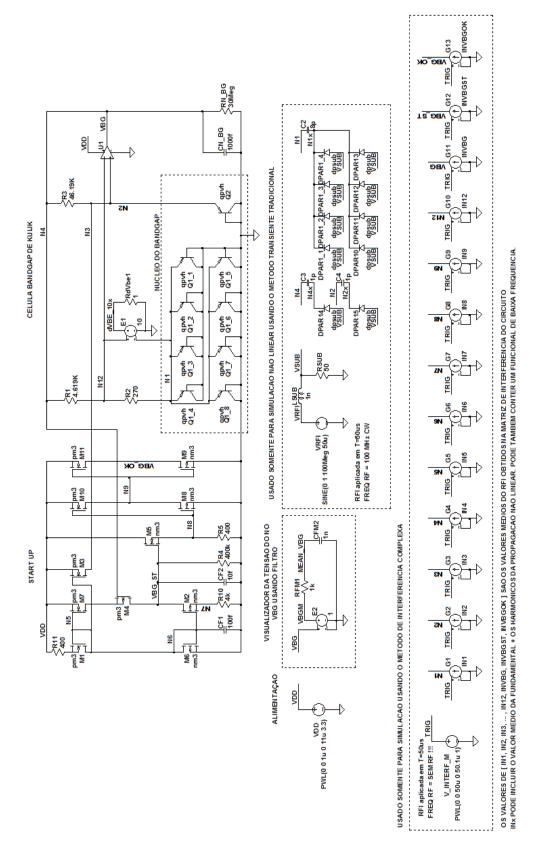

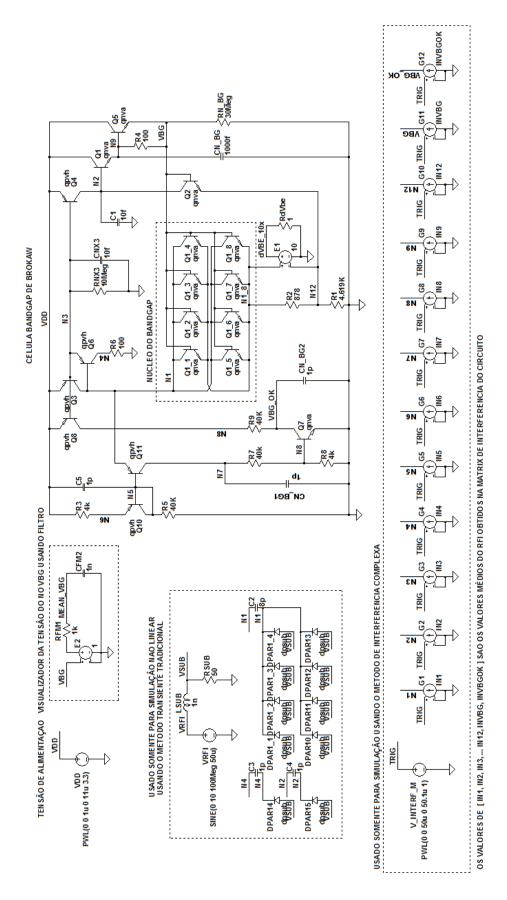

| Figura 5.6 – Simulação e predição dos efeitos de RFI em referências tipo Brokaw                                                                         |     |

| Figura 5.7 – Simulação e predição dos efeitos de RFI em referências tipo Biokaw                                                                         |     |

| Figura 5.8 – Simulação numérica dos efeitos do RFI em referências bandgaps                                                                              |     |

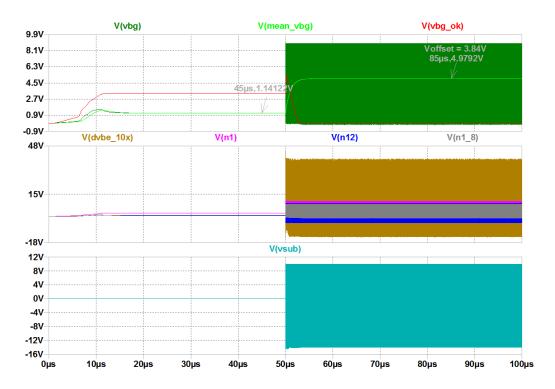

| Figura 5.9 – Simulação do bandgap Brokaw com RFI @ 100MHz, +10dBm                                                                                       |     |

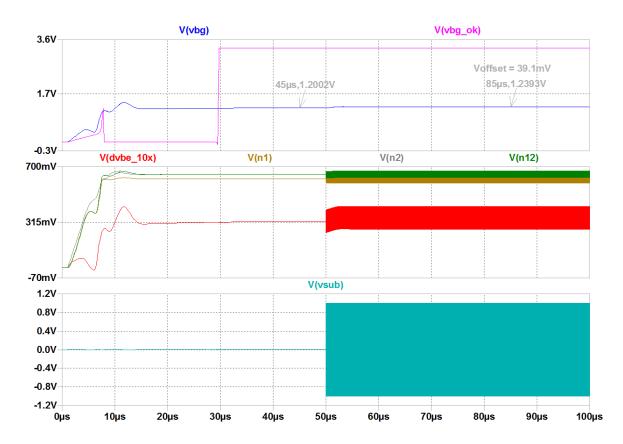

| Figura 5.10 – Simulação do BG Brokaw com RFI @ 100MHz, +10dBm – Zoom @ 90us                                                                             |     |

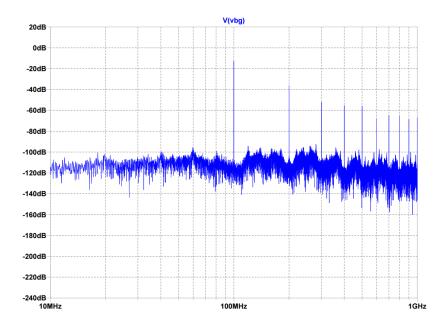

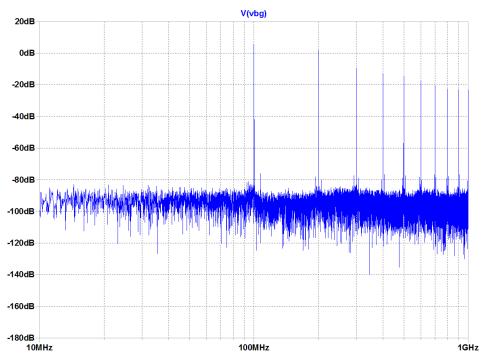

| Figura 5.11 – FFT do $V_{BG}$ do bandgap Brokaw com RFI @ 100MHz, +10dBm                                                                                |     |

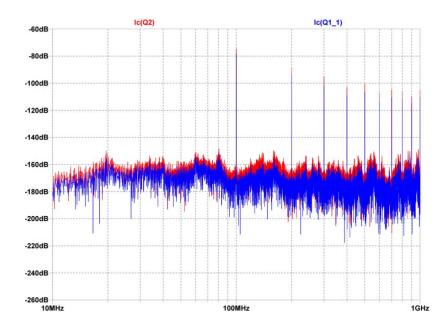

| Figura 5.12 – FFT de iQ1 e Q2 do BG Brokaw com RFI @ 100MHz, +10dBm                                                                                     |     |

| Figura 5.13 – Simulação do bandgap Brokaw com RFI @ 100MHz, +30dBm,                                                                                     |     |

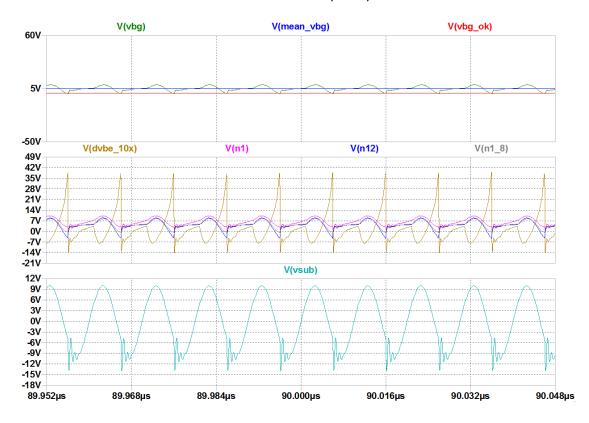

| Figura 5.14 – Simulação do BG Brokaw com RFI @ 100MHz, +30dBm – Zoom @ 90us                                                                             |     |

| Figura 5.15 – FFT do $V_{BG}$ do BG Brokaw com RFI @ 100MHz, +30dBm                                                                                     |     |

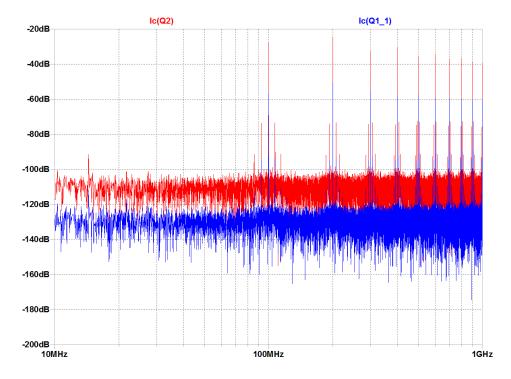

| Figura 5.16 – FFT de iQ1, iQ2 do BG Brokaw com RFI @ 100MHz, $+30$ dBm                                                                                  |     |

|                                                                                                                                                         |     |

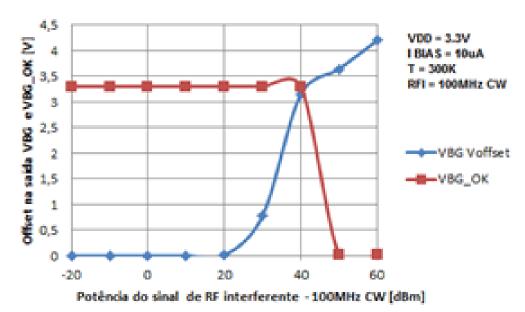

| Figura 5.17 – Simulação do comportamento da saída $V_{BG}$ do bandgap Brokaw com RFI Figura 5.18 – Simulação do bandgap Kuijk com RFI @ 100MHz, +10dBm, |     |

|                                                                                                                                                         |     |

| Figura 5.19 – Simulação do bandgap Kuijk com RFI @ 100MHz, +40dBm,                                                                                      |     |

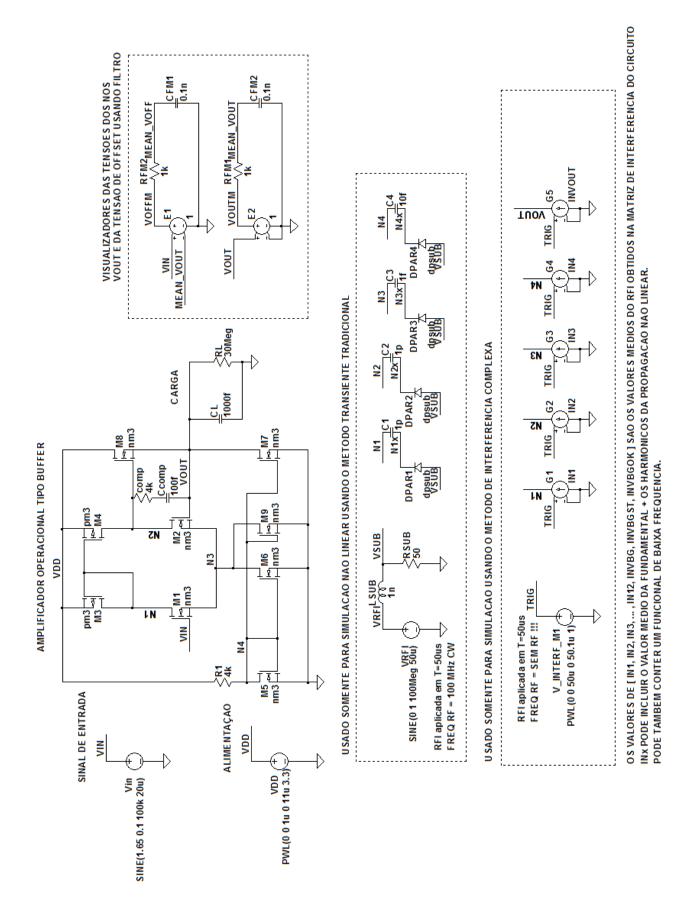

| Figura 5.20 – Simulação do OPAMP com RFI @ 100MHz, +10dBm,                                                                                              |     |

| Figura 5.21 – Simulação do OPAMP com RFI @ 100MHz, +30dBm,                                                                                              |     |

| Figura 5.22 – Simulação do offset de saída <i>do OPAMP</i> em função da potência do RFI                                                                 |     |

| Figura 5.23 – Oscilador de Relaxação de duas fases.                                                                                                     |     |

| Figura 5.24 – Circuito para análise de interferência do nó NI ou N2 de carga do capacitor.                                                              |     |

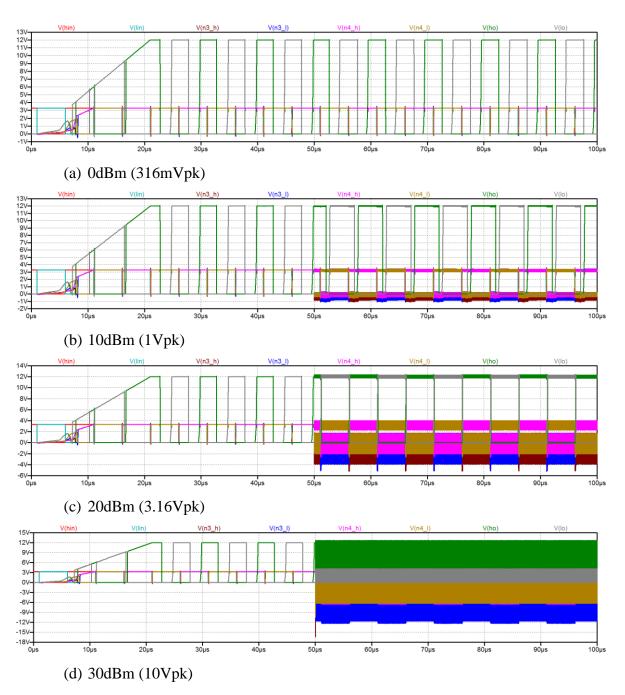

| Figura 5.25 – Simulação transiente para vários níveis de interferência de RF.                                                                           |     |

| Figura 5.26 – Desvio da frequência de oscilação em função da potência do RFI                                                                            |     |

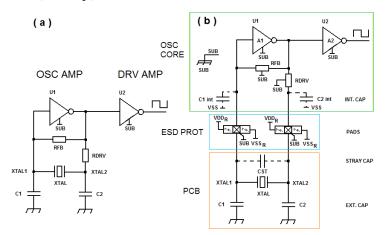

| Figura 5.27 – Oscilador Pierce com capacitores C1 e C2 internos e externos                                                                              |     |

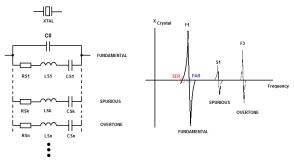

| Figura 5.28 – Modelo equivalente do cristal de quartzo e diagrama de impedância                                                                         |     |

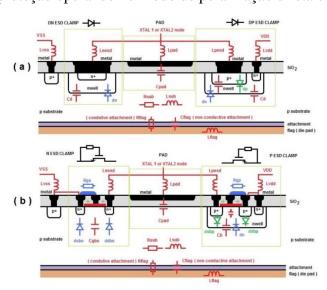

| Figura 5.29 – Proteção de ESD e parasitas considerados para a análise de interferência                                                                  |     |

| Figura 5.30 – Condição de estabilidade de um oscilador Pierce CMOS                                                                                      |     |

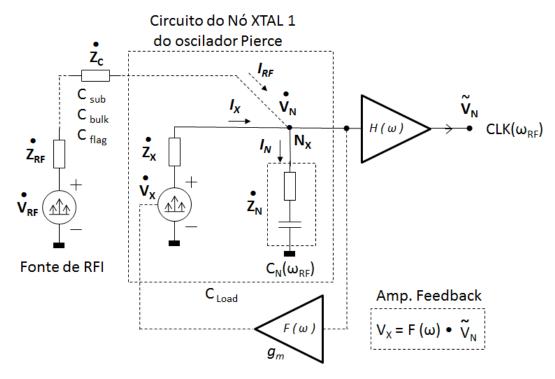

| Figura 5.31 – Caminho de acoplamento para a entrada do amplificador de realimentação                                                                    |     |

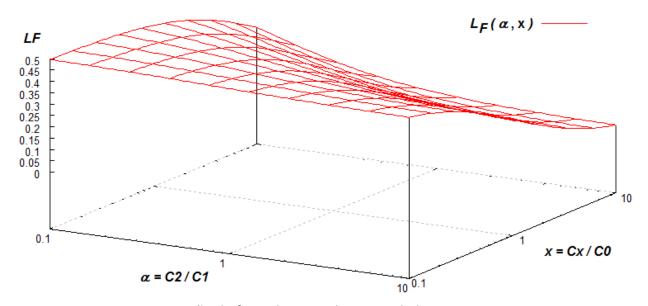

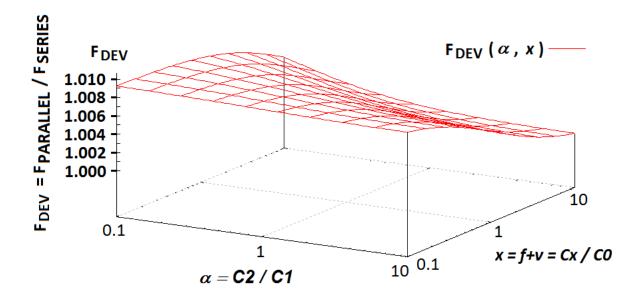

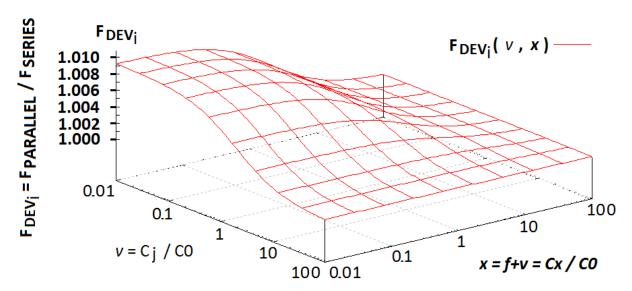

| Figura 5.32 – Função do fator de carga de um oscilador a XTAL tipo Pierce                                                                               |     |

| Figura 5.33 – Desvio de frequência do oscilador sem interferência                                                                                       |     |

| Figura 5.34 – Desvio de frequência do oscilador com interferência                                                                                       |     |

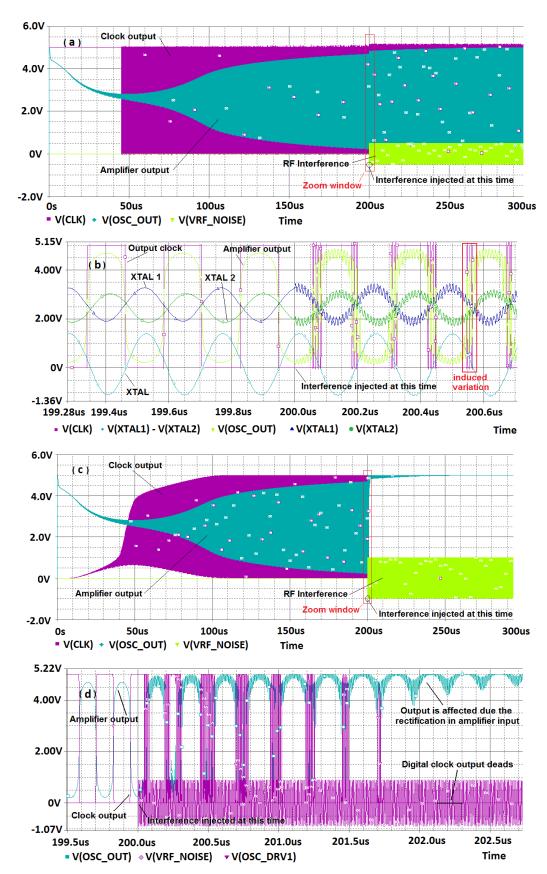

| Figura 5.35 – Simulação transiente do Pierce para vários níveis de RFI @ 100MHz                                                                         |     |

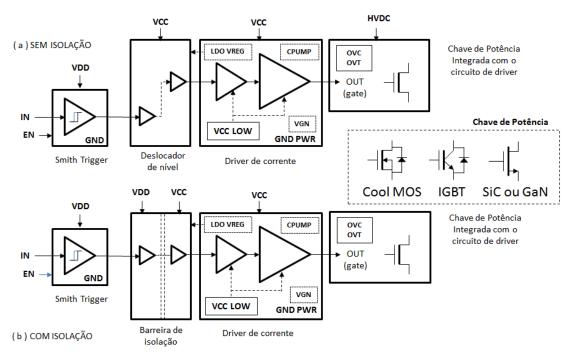

| Figura 5.36 – Driver para chaves de potência em Smart Power                                                                                             |     |

| Figura 5.37 – Simulação <i>Driver</i> Si, para vários níveis de interferência @ 100Mhz                                                                  | 193 |

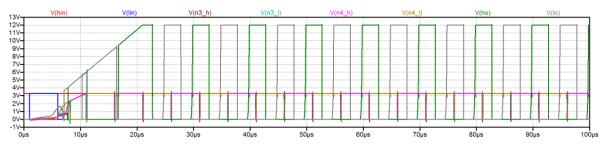

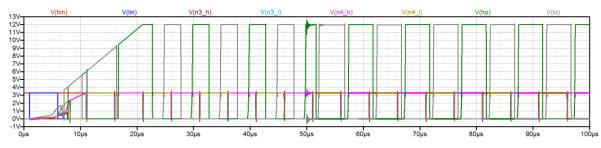

| Figura 5.38 – Simulação <i>Driver</i> SOI, para vários níveis de interferência @ 100MHz.      | 194     |

|-----------------------------------------------------------------------------------------------|---------|

| Figura 5.39 – Simulação TOP de um DC/DC com RFI, mostrando a falha no HVDC                    | 196     |

| Figura 5.40 – Simulação TOP de um DC/DC com RFI, mostrando a falha no MPPT.                   | 196     |

| Figura 5.41 – Simulação TOP de operação normal do inversor conectado (sem RFI).               | 197     |

| Figura 5.42 – Simulação TOP da geração do SPWM para o inversor (sem RFI)                      | 197     |

| Figura 5.43 – Simulação TOP do inversor conectado com RFI no PID                              |         |

| Figura 5.44 – Simulação TOP de operação do inversor conectado com RFI no AD                   | 198     |

| gura 5.45 – Regulador SMP chaveado configurado para análise FRA                               |         |

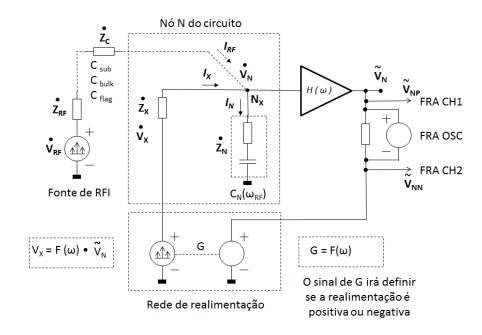

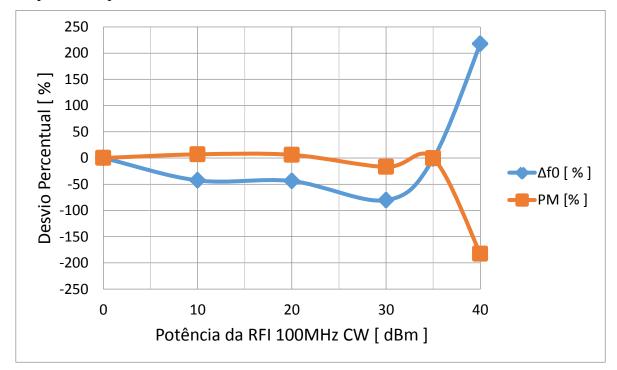

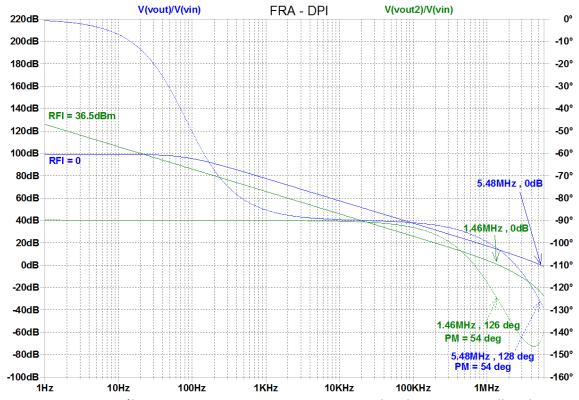

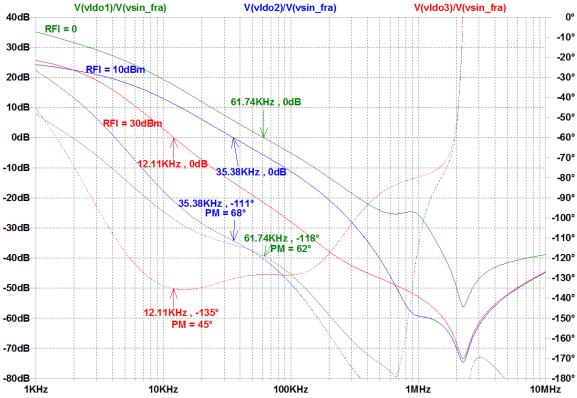

| Figura 5.46 – Análise de interferência de RF combinada com análise de FRA                     | 201     |

| Figura 5.47 – Desvio percentual de $\omega_0$ ( $ A $ = 0dB) e da margem de fase devido ao RF |         |

| igura 5.48 - Análise FRA-RFI para o OPAMP compensador do LDO em malha ab                      |         |

| figura 5.49 – Análise FRA-DPI para o regulador de tensão LDO em malha fechada                 |         |

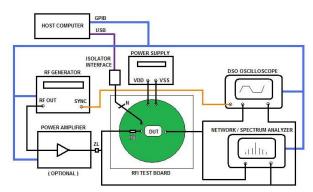

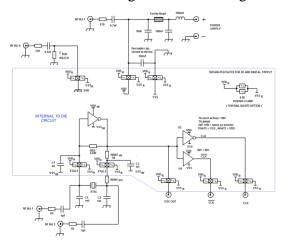

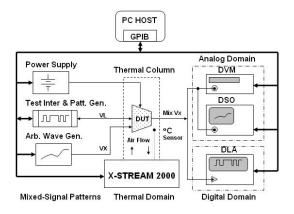

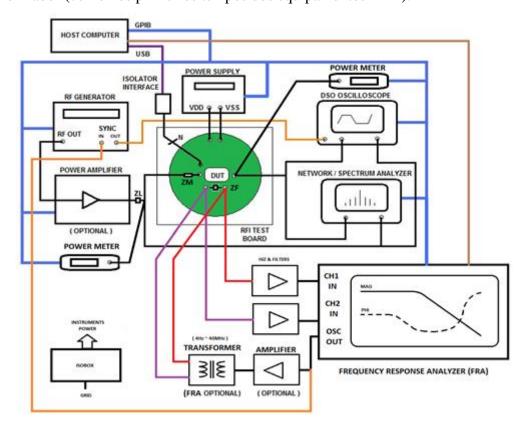

| igura 6.1 – Setup de teste usado para DPI do oscilador de relaxação de duas fases             | 212     |

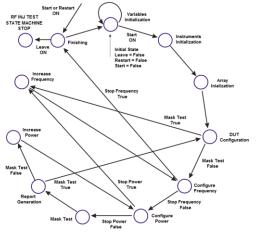

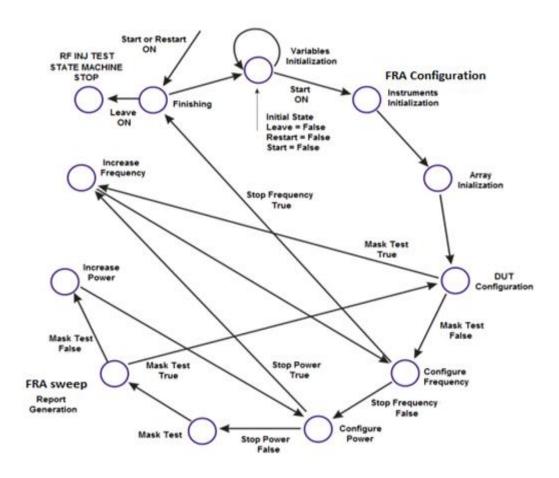

| Figura 6.2 – Máquina de estados do software de controle para o teste de DPI                   | 212     |

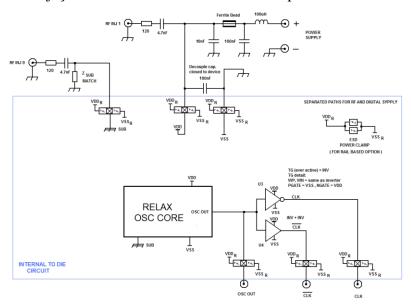

| Figura 6.3 – Configuração usada para o teste DPI do Oscilador de Relaxação                    | 213     |

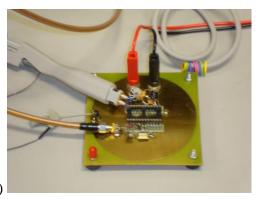

| igura 6.4 – Fotografia da bancada de teste do oscilador de relaxação                          |         |

| Figura 6.5 – Resultados do teste de susceptibilidade a RFI do oscilador de relaxação.         |         |

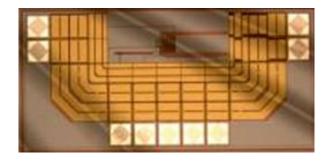

| Figura 6.6 – Microfotografias dos circuitos integrados de teste do oscilador de relaxa        |         |

| Figura 6.7 – Configuração de teste usado para DPI do oscilador xtal Pierce                    | •       |

| gura 6.8 – Máquina de estados do software de controle para o teste de DPI                     |         |

| igura 6.9 – Configuração usada para o teste DPI do Oscilador a cristal tipo Pierce            |         |

| igura 6.10 – Fotografia da bancada de teste do oscilador xtal Pierce                          | 216     |

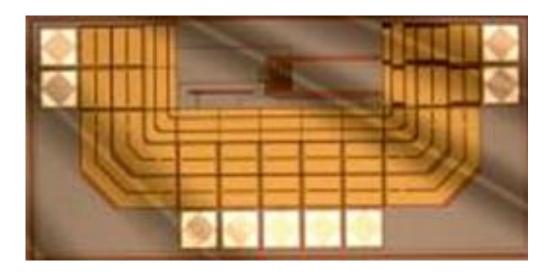

| Figura 6.11 – Microfotografia do circuito integrado teste do oscilador xtal Pierce (V'        |         |

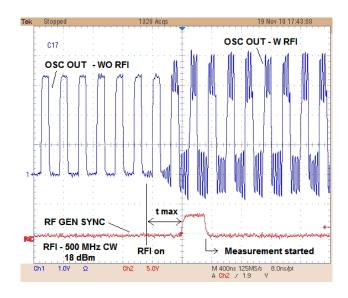

| igura 6.12 – Resposta transiente do Pierce para injeção de RFI @ 500MHz CW 180                | dBm217  |

| Figura 6.13 – Desvio da frequência do oscilador Pierce conforme a capacitância de c           | arga218 |

| igura 6.14 – Desvio do oscilador Pierce de acordo com a Potência de RFI 500MHz                | CW219   |

| igura 6.15 – Desvio do oscilador Pierce com capacitores externos C1 e C2 de 10pF              | 219     |

| igura 6.16 – Desvio do oscilador Pierce somente com capacitores C1 e C2 internos.             | 219     |

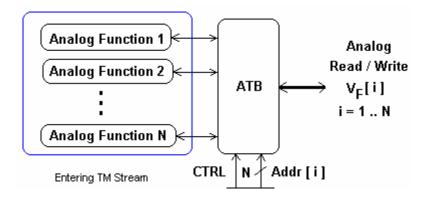

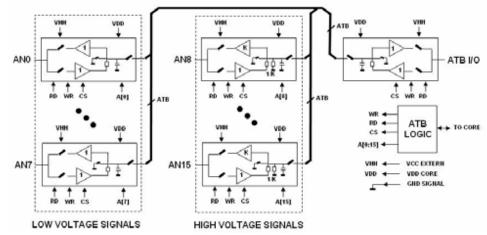

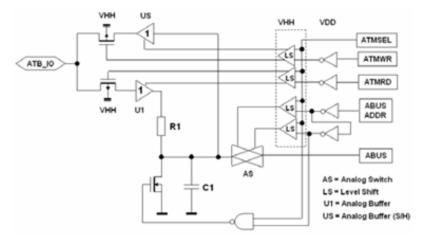

| igura 6.17 – Estratégia de teste via barramento analógico integrado                           | 220     |

| Figura 6.18 – Diagrama de blocos do barramento de teste analógico integrado                   | 221     |

| Figura 6.19 – Circuito de uma célula do barramento de teste analógico integrado               | 221     |

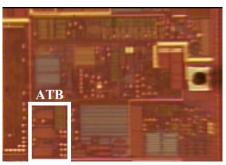

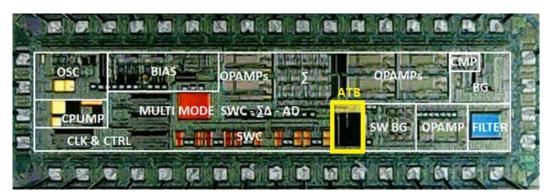

| Figura 6.20 – Microfotografia do barramento de teste integrado em Smart Power                 |         |

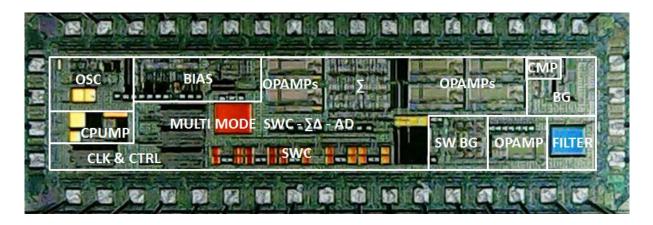

| Figura 6.21 – Microfotografia de um controlador A/D chaveado com ATB (VT3)                    | 222     |

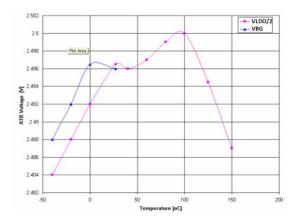

| Figura 6.22 – Setup da caracterização em temperatura de um bandgap e regulador LI             |         |

| Figura 6.23 – Resultados da caracterização em temperatura de um bandgap e um LD               | O 223   |

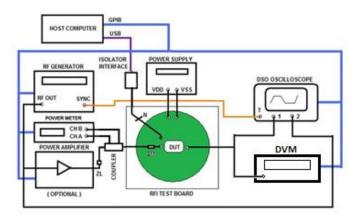

| Figura 6.24 – Configuração do teste de interferência de um bandgap e regulador LDG            | O223    |

| Figura 6.25 – Comportamento do Bandgap e LDO com interferência de RF 200MHz                   |         |

| Figura 6.26 – Desvio percentual do Bandgap com a interferência de RF                          |         |

| Figura 6.27 – Resposta transiente para injeção de RFI @ 100MHz CW 20dBm                       |         |

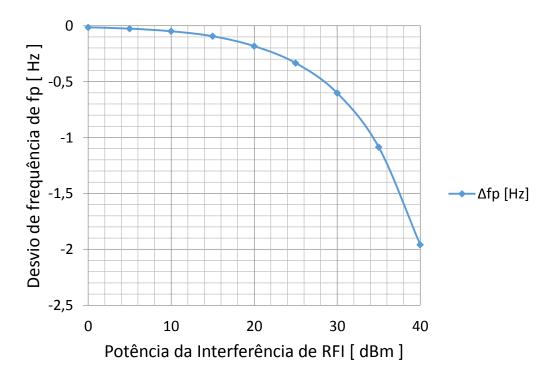

| Figura 6.28 – Desvio da frequência do oscilador relaxação em função da potência de            | RF225   |

| Figura 6.29 – Configuração de teste para análise FRA de falhas de Injeção de RFI              |         |

| Figura 6.30 – Máquina de estado de teste para análise FRA-DPI                                 |         |

| Figura 6.31 – Configuração de teste dos componentes magnéticos utilizados                     | 229     |

| Figura 6.32 – Configuração de teste do FRA utilizado.                                         |         |

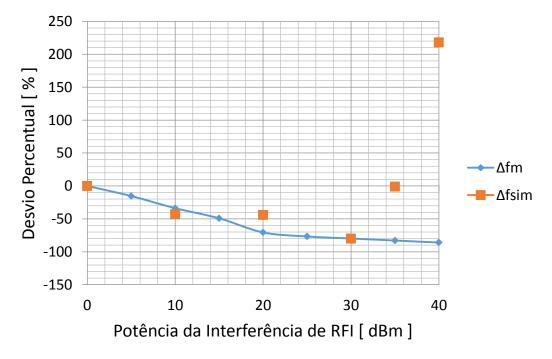

| Figura 6.33 – Desvio da resposta em frequência do Smart Power MIP em função do                |         |

|                                                                                               | 231     |

#### LISTA DE TABELAS

| Tabela 1.1 – Aplicações de Sistemas de Potência                                         | 27    |

|-----------------------------------------------------------------------------------------|-------|

| Tabela 1.2 – Requisitos comuns de robustez conforme mercado de aplicações               | 28    |

| Tabela 1.3 – Fontes de interferência de RF                                              | 37    |

| Tabela 2.1 – Características dos materiais semicondutores: Si versus WBG e UWBG         | 52    |

| Tabela 2.2 – Aplicações de Smart Power em alta temperatura                              | 61    |

| Tabela 2.3 – Implementações Smart Power monolíticas (SOC) versus modular (MIP/SIP).     | 67    |

| Tabela 2.4 – Efetividade da blindagem para uma camada de 100μ @ 300K                    | 70    |

| Tabela 2.5 – Sumário da abordagem da literatura sobre RFI em blocos Smart Power         | 77    |

| Tabela 3.1 – Categorias dos circuitos.                                                  | 80    |

| Tabela 3.2 – Tipos dos métodos de análise                                               | 82    |

| Tabela 3.3 – Energia e Potência Espectral de um sinal $V_{RF}(t)$                       | .112  |

| Tabela 3.4 – Comparação entre os métodos de análise de interferência de RF              | .130  |

| Tabela 4.1 – Frequências de ressonância de diepads/baseplates de circuitos Smart Power  | .148  |

| Tabela 4.2 – Efeitos e Mecanismos de falha devido a RFI.                                | . 150 |

| Tabela 5.1 – Função da energia do bandgap para semicondutores BG, WBG e UWBG            | . 155 |

| Tabela 5.2 – Consequências em outros módulos em função dos desvios no bandgap           | .169  |

| Tabela 5.3 - Conversão A/D em função dos efeitos do RFI no bandgap (100MHz CW)          | .171  |

| Tabela 5.4 – Desvio de frequência no oscilador devido ao RFI (100MHz CW)                | .177  |

| Tabela 6.1 – Circuitos integrados - veículos de teste usados para caracterização de RFI | .210  |

|                                                                                         |       |

#### LISTA DE ABREVIATURAS E SIGLAS

| DISTRIBE RISKE VIRTURAS E SIGERIS |                                         |                                       |  |

|-----------------------------------|-----------------------------------------|---------------------------------------|--|

| TERMO                             | Significado em língua inglesa           | Significado em língua portuguesa      |  |

| AC                                | Alternating Current                     | Corrente Alternada                    |  |

| ADAS                              | Advanced Driver-Assistance Systems      | Sistemas Avançados de Assistência ao  |  |

|                                   |                                         | Motorista                             |  |

| ADC                               | Analog to Digital Converter             | Conversor Analógico para Digital      |  |

| AEV                               | All-Electrical Vehicle                  | Veículo Totalmente Elétrico           |  |

| ASIC                              | Application Specific Integrated Circuit | Circuito Integrado de Aplicação       |  |

|                                   |                                         | Específica                            |  |

| BCD                               | BIPOLAR- CMOS- DMOS                     | BIPOLAR- CMOS- DMOS                   |  |

| BCI                               | Bulk Current Injection                  | Injeção de Corrente de Massa          |  |

| <b>BiCMOS</b>                     | Bipolar CMOS                            | Bipolar CMOS                          |  |

| BIPOLAR                           | Bipolar transistor                      | Transistor bipolar                    |  |

| BJT                               | Bipolar transistor                      | Transistor bipolar                    |  |

| CAN                               | Controller Area Network (CAN bus)       | Controlador de Área de Rede           |  |

| CMOS                              | Complementary Metal Oxide               | Metal Óxido Semicondutor              |  |

|                                   | Semiconductor                           | Complementar                          |  |

| CMRR                              | Common Mode Rejection Ratio             | Relação de Rejeição em Modo Comum     |  |

| CPU                               | Central Processing Unit                 | Unidade Central de Processamento      |  |

| DAC                               | Digital to Analog Converter             | Conversor Digital para Analógico      |  |

| DC                                | Direct Current                          | Corrente Contínua                     |  |

| DDR                               | Double Data Rate                        | Taxa Dobrada de Dados                 |  |

| <b>DMOS</b>                       | Double-Diffused MOS                     | Transistor MOS Duplamente Difundido   |  |

| DPI                               | Direct Power Injection                  | Injeção Direta de Potência            |  |

| DRAM                              | Dynamic RAM                             | RAM dinâmica                          |  |

| DSP                               | Digital Signal Processor                | Processador Digital de Sinais         |  |

| DSO                               | Digital Storage Oscilloscope            | Osciloscópio de Armazenamento Digital |  |

| DUT                               | Device Under Test                       | Dispositivo sob Teste                 |  |

| <b>EEPROM</b>                     | Electrically Erasable Programmable      | Memória ROM Programável               |  |

|                                   | ROM                                     | Eletricamente Apagável                |  |

| <b>EMC</b>                        | Electromagnetic Compatibility           | Compatibilidade Eletromagnética       |  |

| <b>EME</b>                        | Electromagnetic Emission                | Emissão Eletromagnética               |  |

| EMI | Electromagnetic Interference | Interferência Eletromagnética |

|-----|------------------------------|-------------------------------|

|     |                              |                               |

**EMS** Electromagnetic Susceptibility Susceptibilidade Eletromagnética

**ESD** Electrostatic Discharge Descarga Eletrostática

$\mathbf{EV}$ Electrical Vehicle Veículo Elétrico

SOI completamente isolado FD-SOI Fully Depleted Silicon On Insulator

**FPGA** Field-Programmable Gate Array Arranjo de Portas Programáveis em

Campo

Circuito Integrado ou CI

**FRA** Analisador de Resposta em Frequência Frequency Response Analyzer

Nitreto de Gálio **GaN** Gallium Nitride

**Integrated Circuit**

**HEV** Hybrid Electrical Vehicle Veículo Elétrico Híbrido

HB Harmonic Balance Balanceamento Harmônico

I2C **Inter-Integrated Circuit** Circuito Inter Integrado IC

**IGBT Insulated Gate Bipolar Transistor** Transistor Bipolar de Porta Isolada Kirchhoff's Current Law (nodes) **KCL** Lei das Correntes de Kirchoff (nós)

Core of functional Núcleo de um funcional **KERNEL**

KVL Kirchhoff's Voltage Law (meshes) Lei das Tensões de Kirchoff (malhas)

**LDMOS** Laterally Diffused MOS Transistor MOS com difusão Lateral

LIN Rede de interconexão local Local Interconnect Network

LTI Linear Time Invariant system Sistema Linear Invariante no Tempo

MOS Metal Oxide Semiconductor Metal-Oxido-Semicondutor

MOS transistor **Transistor MOS MOSFET**

**MPPT** Maximum Power Point Tracker Rastreador do Ponto de Máxima

Potência

**MPW** Multi-Product-Wafer Wafer com vários produtos

**NMOS** N-Channel MOS transistor Transistor MOS canal N

**OCP** Over Current Protection Proteção de sobre corrente

**OVP** Over Voltage Protection Proteção de sobre tensão

**OTP** Over Temperature Protection Proteção de sobre temperatura

PF Power Factor Fator de Potência

**PFC** Power Factor Correction Fator de Correção de Potência

PLL Phase-Locked Loop Laço Fechado em Fase

**PMOS** P-Channel MOS transistor Transistor MOS canal P **PSD** Power Spectral Density Densidade Espectral de Potência

PV Photovoltaic Fotovoltaico

PMU Multiuser Program Programa Multiusuário

PWM Pulse Width Modulation Modulação de Largura de Pulso

RAM Random Access Memory Memória de Acesso Aleatório

**RE** Radiated Emission Emissão Radiada

**RF** Radio Frequency Frequência de Rádio

**ROM** Read Only Memory Memória Apenas de Leitura

RFI Radio Frequency Interference Interferência de Frequência de Rádio SCI Serial Communications Interface Interface de Comunicação Serial

SCL Serial Clock line Linha de Relógio Serial

SCR Silicon Controlled Rectifier Retificador Controlado de Silício

SDASerial Data lineLinha de Dados SeriaisSDRAMSynchronous Dynamic RAMRAM Dinâmica Síncrona

SiGeSilicon-GermaniumSilício-GermânioSiCSilicon CarbideCarbeto de Silício

SIP System In a Package Sistema em um encapsulamento

SMART Smart Power Integrated Circuit Circuito Integrado de Potência

**POWER** Inteligente

SOASafe Operating AreaÁrea de Operação SeguraSOARSafe Operating AReaÁrea de Operação Segura

**SOC** System On a Chip Sistema em um circuito integrado

**SOI** Silicon On Insulator Silício sobre isolador

SPI Serial Peripheral Interface Interface Periférica Serial

SRAMStatic RAMRAM estáticaSPWMSine PWMPWM senoidal

**THD** Total Harmonic Distortion Distorção Harmônica Total

**TRAN** Transient Analysis Análise Transiente

USB Universal Serial Bus Barramento Serial Universal

VMOS Vertical MOS transistor Transistor MOS Vertical

UWBG Ultra Wide BandGap semiconductor Semicondutor de BandGap Ultra Largo

WBG Wide BandGap semiconductor Semicondutor de BandGap Largo

ZCS Zero-Current-Switching Chaveamento em Corrente Zero

ZVS Zero-Voltage-Switching Chaveamento em Voltagem Zero

#### LISTA DE SIMBOLOS

| Símbolo           | Significado em língua inglesa   | Significado em língua portuguesa    |

|-------------------|---------------------------------|-------------------------------------|

| α                 | Quadratic adjust constant       | Constante de ajuste quadrático      |

| β                 | Linear adjust constant          | Constante de ajuste linear          |

| γ                 | Nonlinear adjust constant       | Constante de ajuste não linear      |

| $\mathcal{E}_{S}$ | Material permissivity           | Constante dielétrica relativa       |

| $\varepsilon_0$   | Vacuum permissivity             | Permissividade do vácuo             |

| λ                 | Waveform Length                 | Comprimento de onda                 |

| h                 | Nonlinear temperature constant  | Constante não linear de temperatura |

| $\mu_n$           | Electron Mobility               | Mobilidade dos elétrons             |

| $\omega_{RF}$     | RF Frequency in rad/s           | Frequência de RF em rad/s           |

| $\psi_{RF}$       | Spectral energy density         | Densidade de energia espectral      |

| A                 | Area                            | Área                                |

| В                 | Magnetic Field                  | Campo magnético                     |

| $B_V$             | Breakdown Voltage               | Tensão de ruptura                   |

| c                 | Light Velocity                  | Velocidade da Luz                   |

| $C_J$             | Junction capacitance            | Capacitância de junção              |

| $C_L$             | Load capacitance                | Capacitância de carga               |

| $C_{SC}$          | Series coupling capacitance     | Capacitância de acoplamento série   |

| DR                | Dynamic range                   | Faixa dinâmica                      |

| E                 | Electric Field                  | Campo elétrico                      |

| $E_C$             | Critical electric field         | Campo elétrico crítico              |

| $E_{FF}$          | Efficiency                      | Eficiência                          |

| $E_G$             | Bandgap energy                  | Energia de bandgap                  |

| $E_{G0}$          | Bandgap energy at 0K            | Energia de bandgap a 0K             |

| $E_{GE}$          | Normalized bandgap energy       | Energia de bandgap normalizada      |

| $g_m$             | Transconductance                | Transcondutância                    |

| H                 | Absolute normalized temperature | Temperatura absoluta normalizada    |

| $I_C$             | BJT collector current           | Corrente de coletor de um BJT       |

| $I_D$             | MOS drain current               | Corrente de dreno de um MOS         |

| $I_N$             | Node current                    | Corrente no nó N                    |

| $f$ , $f_{RF}$    | Frequency in Hz                 | Frequência em Hz                    |

| J                 | Current density                 | Densidade de corrente               |

| k | Boltzmann's constant | Constante de Boltsmann |

|---|----------------------|------------------------|

|   | ~ .                  | ~                      |

K Gain constant Constante de ganho

$L_{SC}$  Series coupling inductance Indutância de acoplamento série M Number of devices or terms Número de dispositivos ou termos

N Number of nodes Número de nós

$N_A$ ,  $N_D$  N and P dopants concentration Concentração de dopantes N e P

q Electron charge Carga do elétron

$R_{ON}$  ON state resistance Resistência no estado ligado  $R_{ON\text{-}SP}$  Specific ON state resistance Resistência ligado específica

$R_L$  Load resistance Resistência de carga

$R_{SC}$  Series coupling resistance Resistência de acoplamento série  $S_{RF}$  Spectral power density of RF Densidade de potência espectral  $S_X$  Spectral power density of signal Densidade de potência espectral

T Temperature Temperatura

$T_R$  Reference temperature Temperatura de referência

$T_{RF}$  RF interference period Período da interferência de RF  $t_{RR}$  Reverse recovery time Tempo de recuperação inversa  $V_{BE}$  BJT base to emitter voltage Tensão base-emissor de um BJT

$V_{BG}$  Bandgap voltage Tensão de bandgap

$V_{DS}$  MOS drain to source voltage Tensão dreno-source MOS  $V_{GS}$  MOS gate to source voltage Tensão gate-source MOS

$V_L$  Load voltage Tensão na carga  $V_N$  N node voltage Tensão no nó N

$V_{REF}$  Reference voltage Tensão de referência

$V_{S\_S}$  Supply to supply voltage Tensão entre alimentações  $V_T$  Thermodynamic voltage Tensão termodinâmica  $V_{TH}$  MOS threshold voltage Tensão de limiar MOS

$V_{TN}$  Thermodynamic voltage at  $T_N$  Tensão termodinâmica para  $T_N$

$V_X$  X node voltage Tensão no nó X

$Y_N$  Node admittance Admitância no nó N  $Z_N$  Node impedance Impedância no nó N

$Z_C$  Coupling impedance Impedância de acoplamento

### **SUMÁRIO**

| Capítulo 1                                                                     | 22 |

|--------------------------------------------------------------------------------|----|

| 1 Introdução                                                                   | 22 |

| 1.1 Circuitos Integrados de Potência - Cenário                                 | 22 |

| 1.1.1 Aplicações segundo segmentos de mercado                                  | 23 |

| 1.1.2 Requisitos de Robustez                                                   | 28 |

| 1.2 Compatibilidade Eletromagnética                                            |    |

| 1.2.1 Perspectiva histórica do problema de interferência de RF                 |    |

| 1.2.2 Principais fontes de interferência de RF                                 |    |

| 1.2.3 A questão da Normalização                                                |    |

| 1.3 Interferência de RF em circuitos integrados de potência                    |    |

| 1.4 Motivações e definição do problema                                         |    |

| 1.5 Objetivos                                                                  |    |

| 1.6 Metodologia                                                                |    |

| 1.7 Contribuições da tese                                                      | 44 |

| 1.8 Organização da tese                                                        | 46 |

| 1.9 Resumo e conclusões do Capítulo 1                                          | 47 |

| Capítulo 2                                                                     | 48 |

| 2 Tecnologias de Circuitos Integrados de Potência                              | 48 |

| 2.1 Introdução                                                                 | 48 |

| 2.2 Revisão da Literatura – Estado da Arte                                     | 48 |

| 2.3 Tecnologias Monolíticas de Potência Inteligente (Smart Power)              | 55 |

| 2.4 Tecnologias Hibridas Modulares de Potência Inteligente (SIP)               |    |

| 2.5 Principais contribuições da tecnologia para o RFI                          |    |

| 2.5.1 Fontes e caminhos de acoplamento                                         |    |

| 2.5.2 Influências do substrato                                                 | 68 |

| 2.5.3 Contribuições do encapsulamento                                          |    |

| 2.5.4 Uso de blindagens e sua efetividade                                      |    |

| 2.6 Tecnologia e Arquitetura de Circuitos Integrados Smart Power               |    |

| 2.7 Interferência RFI em blocos de construção de circuitos Smart Power         |    |

| 2.8 Resumo e conclusões do Capítulo 2                                          | 78 |

| Capítulo 3                                                                     |    |

| 3 Métodos de Análise da Interferência de RF                                    | 79 |

| 3.1 Introdução - Análise da interferência                                      | 79 |

| 3.1.1 Particionamento para análise dos circuitos                               |    |

| 3.1.2 Domínios dos métodos de análise                                          |    |

| 3.2 Metodologias tradicionais de análise                                       |    |

| 3.2.1 Análise transiente (Spice TRAN)                                          |    |

| 3.2.2 Análise em frequência (Frequency response)                               |    |

| 3.2.3 Análise de Balanço Harmônico (Harmonic Balance)                          |    |

| 3.3 Métodos de modelagem dos circuitos                                         |    |

| 3.4 Métodos clássicos de análise não linear                                    |    |

| 3.4.1 Métodos de análise da série de Taylor (Domínio do tempo, comportamental) |    |

| 3.4.2 Métodos de análise da série Volterra (Domínio do tempo)                  |    |

| \ I /                                                                          |    |

| 3.4.2.1 Relação entre as séries de Taylor e de Volterra                | 104 |

|------------------------------------------------------------------------|-----|

| 3.4.2.2 A questão da convergência das séries de Volterra               | 106 |

| 3.4.2.3 A questão da identificação de Núcleos das séries de Volterra   |     |

| 3.4.2.4 Métodos de análise por série de Volterra modificada            |     |

| 3.4.3 Métodos de análise da série Wiener (Domínio da frequência)       |     |

| 3.5 Proposição de um novo método: Interferência Complexa (t, NL, $x$ ) |     |

| 3.5.1 Fundamentação                                                    |     |

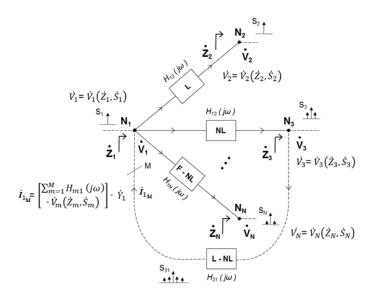

| 3.5.2 Propagação de um sinal com funcionais                            |     |

| 3.5.2.1 Propagação de um sinal linear com funcionais                   |     |

| 3.5.2.2 Propagação de um sinal não linear com funcionais               |     |

| 3.5.2.3 Propagação de um sinal fracamente não linear com funcionais    |     |

| 3.5.2.4 Propagação geral do sinal em cascata com M caminhos            |     |

| 3.5.4 Estimação do valor médio por integração                          |     |

| 3.5.5 Estimação do valor médio através de um filtro                    |     |

| 3.5.6 Fluxograma de aplicação do método de interferência complexa      |     |

| 3.6 Comparação entre os métodos                                        |     |

| 3.7 Resumo e conclusões do Capítulo 3                                  |     |

| Capítulo 4                                                             |     |

| 4 Efeitos e Mecanismos de Falhas devido a RFI                          |     |

|                                                                        |     |

| 4.1 Introdução                                                         |     |

| 4.2 Mecanismos de falha devido a RFI em circuitos Smart Power          |     |

| 4.2.1 Propagação do RFI acoplado via tensão de alimentação             |     |

| 4.2.1.1 Diminuição da Faixa de Excursão dos Sinais                     |     |

| 4.2.1.2 Diminuição da Faixa Dinâmica                                   |     |

| 4.2.3 Propagação do RFI acoplado via substrato (ou outro ZC)           |     |

| 4.3 Proposição de modelamento do efeito antena do diepad/baseplate     |     |

| 4.4 Discussão sobre efeitos, mecanismos de falha e mitigação do RFI    |     |

| <u>e</u>                                                               |     |

| 4.5 Resumo e conclusões do Capítulo 4                                  |     |

| Capítulo 5                                                             | 152 |

| 5 Simulação e Predição usando o método de Interferência Complexa       |     |

| 5.1 Introdução                                                         | 152 |

| 5.2 Métodos de simulação para predição dos efeitos do RFI              | 152 |

| 5.3 Estudo de casos: Blocos Smart Power fundamentais                   | 153 |

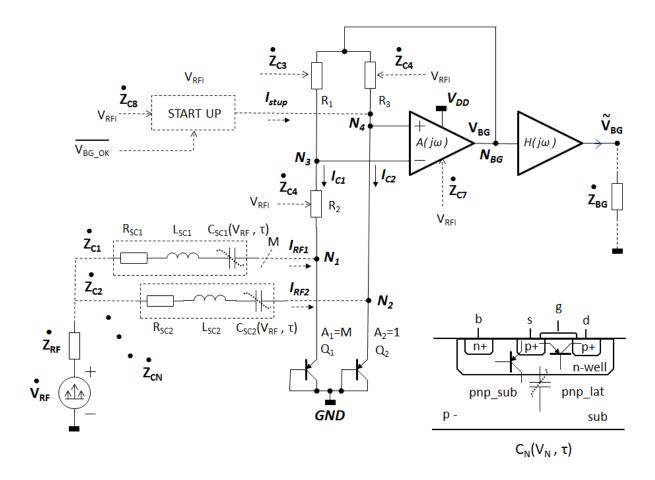

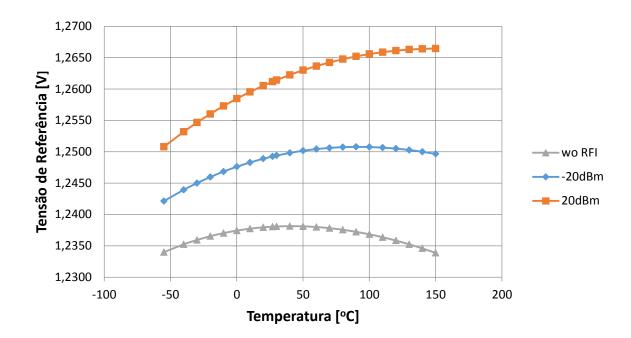

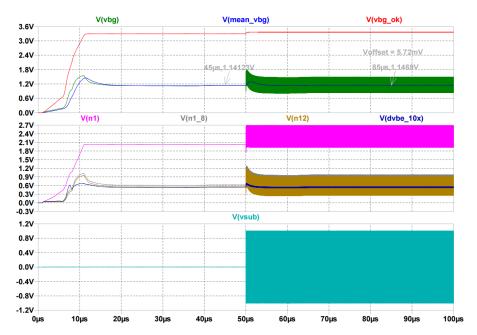

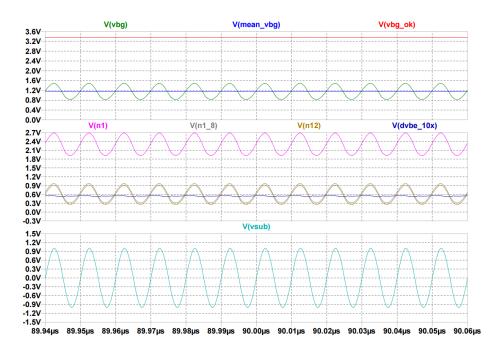

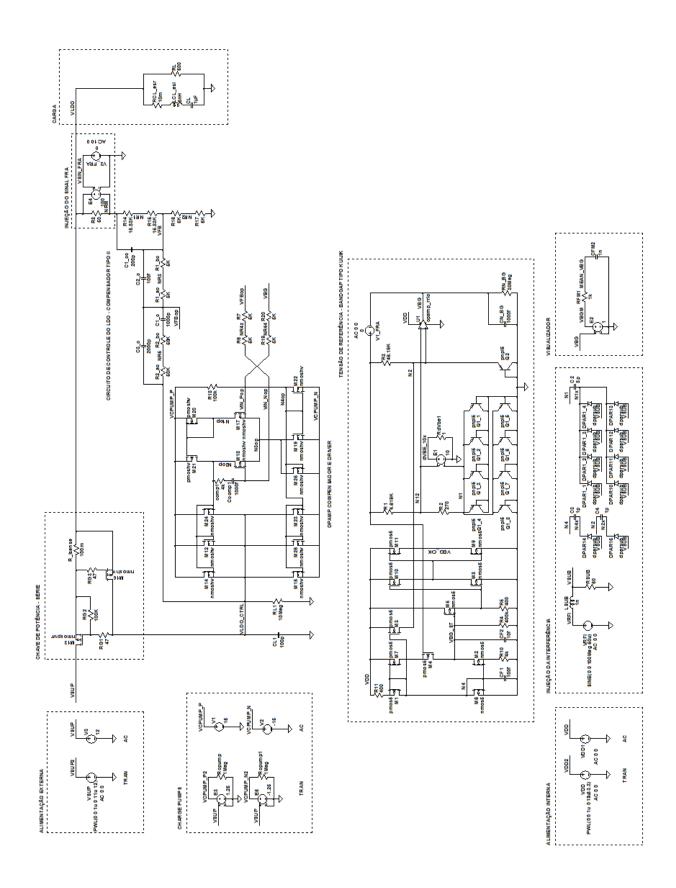

| 5.3.1 Estudo de Caso 1: RFI em referências Bandagap                    | 155 |

| 5.3.2 Estudo de Caso 2: RFI em condicionadores de sinal (OPAMPs)       |     |

| 5.3.3 Estudo de Caso 3: RFI em osciladores de relaxação                |     |

| 5.3.4 Estudo de Caso 4: RFI em osciladores em osciladores harmônicos   |     |

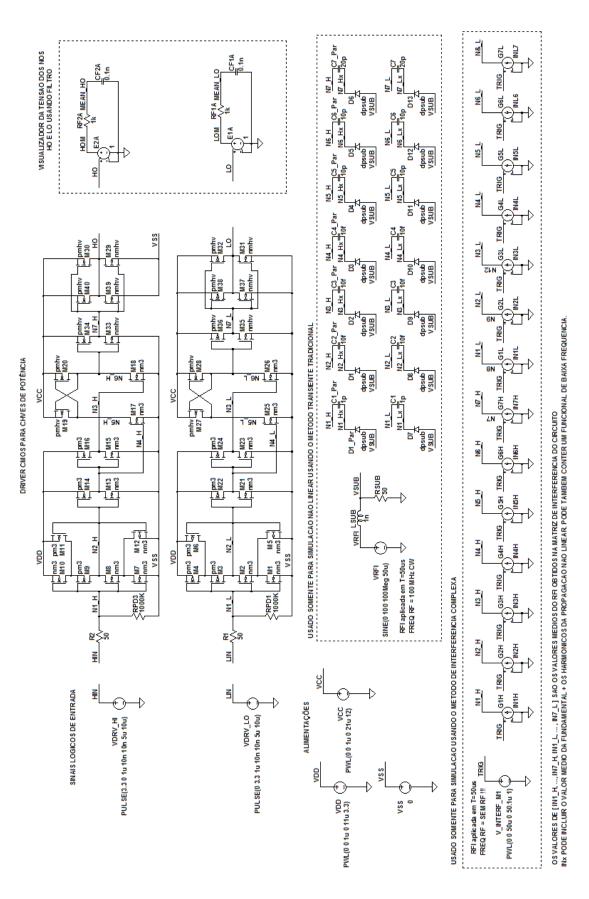

| 5.3.5 Estudo de Caso 5: RFI em drivers para chaves de potência         |     |

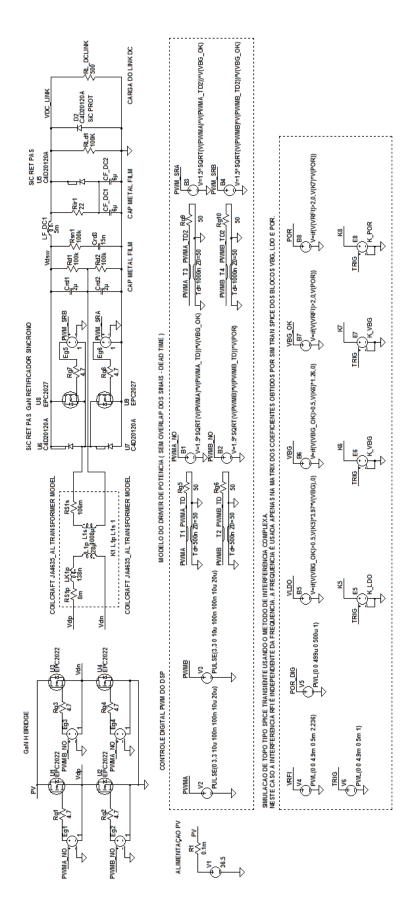

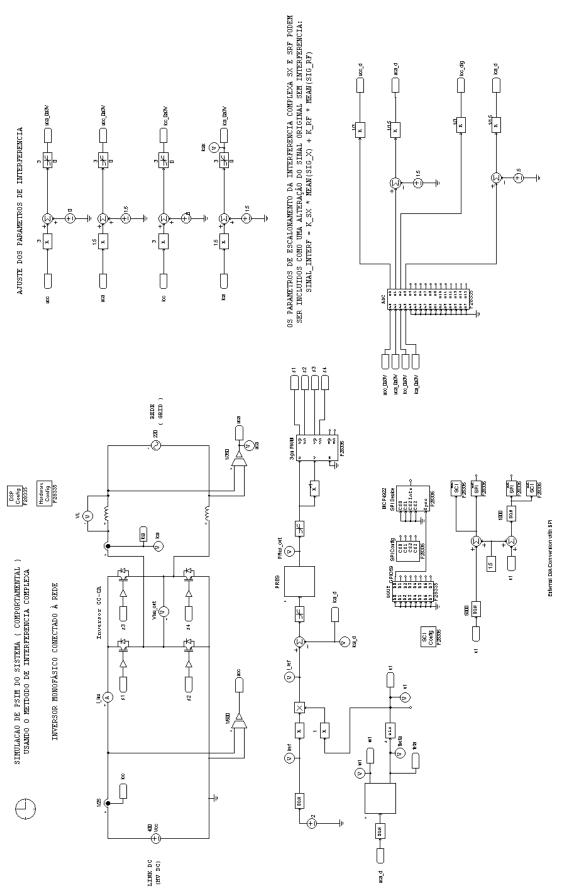

| 5.3.6 Estudo de Caso 6: RFI em um inversor WBG de 1kW de potência      |     |

| 5.4 Proposição de um novo método de prospecção: FRA-DPI                |     |

| 5.5 Resumo e conclusões do Capítulo 5                                  |     |

| Capítulo 6                                                             | 207 |

| 6 Caracterização e Testes                                              | 207 |

| 6.1 Introdução                                                         | 207 |

| 6.2 Metodologia experimental de caracterização e testes em laboratório | 207 |

|                                                                        |     |

| 6.3 Métodos de teste no domínio do tempo                          | 207 |

|-------------------------------------------------------------------|-----|

| 6.3.1 Método de BCI (Bulk Current Injection)                      | 208 |

| 6.3.2 Método de DPI (Direct Power Injection)                      |     |

| 6.3.3 Método de surtos transientes e ESD                          |     |

| 6.4 Métodos de teste no domínio de frequência                     |     |

| 6.4.1 Método de Análise de Resposta Harmônica (multitonal)        |     |

| 6.4.2 Método de Análise de Resposta em Frequência (FRA)           |     |

| 6.5 Outros métodos de teste e análise                             |     |

| 6.6 Caracterização de RFI em circuitos Smart Power                |     |

| 6.7 Caracterização tradicional de RFI em blocos Smart Power (DPI) |     |

| 6.7.1 Exemplo 1 – Oscilador de relaxação de duas fases            |     |

| 6.7.2 Exemplo 2 – Oscilador harmônico a cristal tipo Pierce       |     |

| 6.8 Proposta de um barramento de testes de RFI analógico: ATB-RFI |     |

| 6.9 Proposta de um novo método de caracterização: FRA-DPI         |     |

| 6.10 Resumo e conclusões do Capítulo 6                            | 232 |

| Capítulo 7                                                        | 233 |

| 7 Conclusões                                                      | 233 |

| 7.1 Introdução                                                    | 233 |

| 7.2 Resultados, discussões e conclusões                           | 233 |

| 7.3 Sugestões para trabalhos futuros                              | 234 |

| 7.4 Considerações finais                                          | 234 |

| 8 Publicações                                                     | 235 |

| Lista de publicações do autor                                     |     |

| 9 Referências Bibliográficas                                      |     |

| 10 Apêndices                                                      |     |

| Apêndice A – Informações e tabelas de conversão usadas            |     |

| Apêndice B – Dados sobre tecnologias BG, WBG e UWBG               |     |

| Apêndice C – Métodos matemáticos                                  |     |

| Apêndice D – Modelamentos                                         |     |

| Apêndice E – Circuitos de teste usados nas simulações             |     |

| Apêndice F – Circuitos integrados projetados e usados para teste  |     |

| riperialee i Circuitos integrados projetados e asados para teste  | 200 |

|                                                                   |     |

## Capítulo 1

### Introdução

#### 1.1 Circuitos Integrados de Potência - Cenário

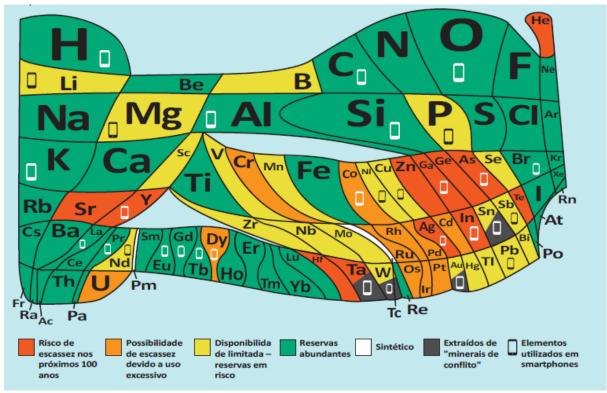

Os dispositivos eletrônicos de potência são amplamente utilizados em sistemas de conversão de energia, que são fundamentais para o funcionamento de vários tipos de equipamentos, sendo essenciais aos mesmos. Eles atuam no processo da transformação da energia no que diz respeito à adequação dos seus níveis (amplitude) e da sua forma de condução (contínua ou alternada). Outro ponto importante diz respeito à questão da eficiência energética da conversão, sendo notável sempre a busca por sistemas cada vez mais eficientes. Os dispositivos semicondutores de potência foram usados primariamente nestes tipos de circuito como dispositivos de controle do fluxo de potência, atuando como resistores controlados. Entretanto com a introdução dos sistemas chaveados, eles encontraram sua principal aplicação, tornando-se possível reduzir o montante de energia perdida por efeito Joule, reduzindo-se as perdas, assim como propiciando um mecanismo de conversão de corrente contínua em corrente alternada. Do ponto de vista da industrialização, este ponto contribuiu para o desenvolvimento de produtos e equipamentos mais compactos, com menor custo e maior complexidade, o que levou a necessidade de dispositivos cada vez mais complexos, incluindo não só as chaves de potência, mas contendo todos os circuitos de controle das mesmas, assim como associando inteligência aos mesmos (Smart Power). Além disto, a inclusão de processadores lógicos nestes sistemas possibilitou o acesso remoto aos equipamentos (via grid e wireless), assim como conexão em redes ethernet e recentemente conexão em nuvem com a internet (IoT). Neste contexto, as necessidades de mercado levaram as principais indústrias de semicondutores ao desenvolvimento de uma gama de produtos dedicados a sistemas de potência, em particular os circuitos integrados de potência inteligentes, assim como no desenvolvimento e pesquisa em novas tecnologias, ultrapassando as limitações das anteriores com relação à frequência e aos limites de potência e tensão de operação impostas pelas tecnologias anteriores baseadas no silício. Paralelamente a este desenvolvimento tivemos uma grande evolução dos sistemas de radiofrequência, com ampla utilização de RF em várias bandas, cuja interação com estes sistemas geraram situações de conflito conhecidas como Compatibilidade Eletromagnética (EMC).

#### 1.1.1 Aplicações segundo segmentos de mercado

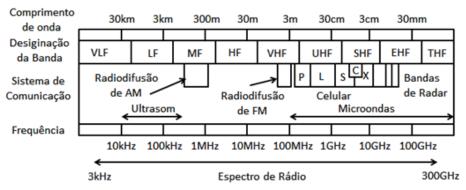

Atualmente temos várias aplicações para os conversores de energia, operando nos modos DC/DC, AC/DC, DC/AC e AC/AC, nas mais variadas áreas de aplicação, conforme as listadas e discutidas em Mohan *et al.* (1995, p.7-9), abrangendo aplicações de baixa a alta potência, podendo ser lineares ou chaveadas. Para o escopo deste trabalho, foi listado um subconjunto destas aplicações conforme as principais áreas de aplicações, com faixas de potência de 1W a 180kW, com especial interesse na faixa de 1kW a 10kW (faixa de potência com grande volume de produção industrial), relacionando-se com as frequências de chaveamento destes conversores. Elas são utilizadas em projetos industriais, e também são encontrados em aplicações na literatura, estando sumarizados na Tabela 1.1. Considerando-se questões de Compatibilidade Eletromagnética (EMC), estas frequências são importantes do ponto de vista da interferência, devido ao chaveamento de potência com transições abruptas, que podem resultar em emissão eletromagnética de RF.

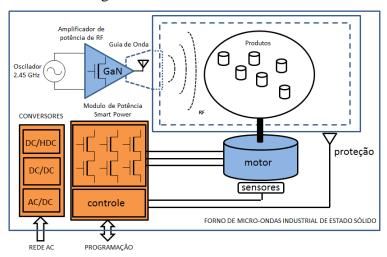

Assim, partindo deste subconjunto, como exemplos, temos as aplicações no setor industrial com a utilização de módulos para controle de motor (bifásicos e trifásicos), retificadores de potência, e conversores de energia, para máquinas de solda (e.g. Mohan *et al.* (1995, p. 458).), fornos de indução e fornos de micro-ondas com válvulas *Magnetron* (e.g. Georghiou *et al.* (1999)), envolvendo o uso de módulos de potência (IGBT e SiC principalmente). Com a evolução dos dispositivos WBG, começam a surgir fornos de micro-ondas usando dispositivos de estado sólido GaN, em substituição as *magnetrons* (e.g. Nakatani e Ishizaki (2015)), o que abre mercado para módulos *Smart Power* para tais aplicações, como ilustrado na Figura 1.1.

Figura 1.1 – Aplicações na área industrial – forno de micro-ondas de estado sólido. Fonte: Maltione (2020).

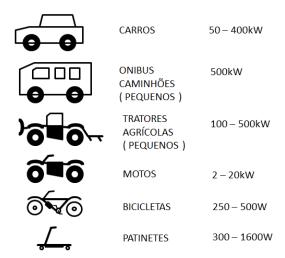

No setor automotivo, a conversão de energia de potência, encontrou sua principal forma de expansão com o advento dos veículos totalmente elétricos (EV) ou híbridos (HEV) onde são necessárias várias formas de conversão tais como a carga das baterias (AC/DC), acionamento do motor de propulsão (DC/AC) e geração da alimentação interna (DC/DC), conforme ilustrado na Figura 1.2, em uma diversidade de aplicações e potências. Segundo Elva (2013, p. 12-13), espera-se um market de 5% de EVs em 2020, que deve ser acelerado ao longo das próximas décadas devido ao compromisso assumido pelos países dos grupos G8 e EU para redução de das emissões de CO<sub>2</sub> em 80% para 2050. Segundo dados da Tabela 1.1, podemos verificar que com a transição dos veículos híbridos (HEV) para os totalmente elétricos (EV), teremos uma demanda maior em cerca de uma ordem de grandeza na potência elétrica empregada.

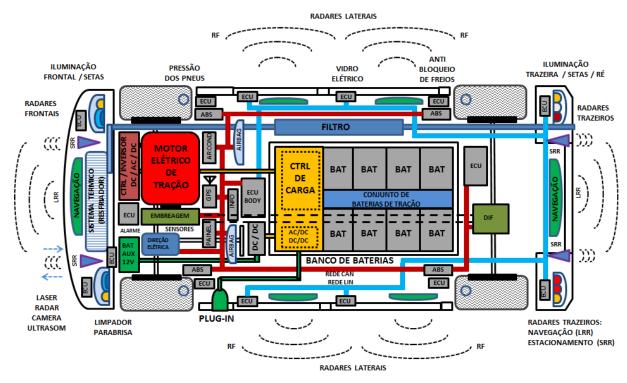

Com relação ao sistema podemos verificar na Figura 1.3, que temos vários módulos de controle (e.g. AFDC (2020), NPTEL (2020), etc.) podendo utilizar circuitos *Smart Power* com função integrada de sensoriamento, controle/processamento e conversão de energia com uso chaves de potência (MOS, IGBT, SiC e GaN) e com ampla utilização das redes de comunicação automotivas, CAN e LIN. Em cenário de futuro próximo, temos a aplicação de vários sistemas de radar usando RF, Laser ou ultrassom, para navegação (*Laser*), proteção anticolisão (curta distância – SRR, larga distância – LRR) e assistência a estacionamento (podendo usar também ultrassom ou câmeras). Os sistemas de radares iniciaram operando na faixa de micro-ondas de 24GHz, sendo que atualmente operam na faixa de 77GHz. Outros sistemas para navegação utilizam o sistema de posicionamento global (GPS) e redes de telefonia celular (3G, 4G e 5G) para auxílio à navegação e trânsito.

Figura 1.2 – Aplicações no setor de transportes – veículos elétricos. Fonte: Maltione (2020).

Figura 1.3 – Aplicações na área automotiva – carro totalmente elétrico (EV). Fonte: Maltione (2020).

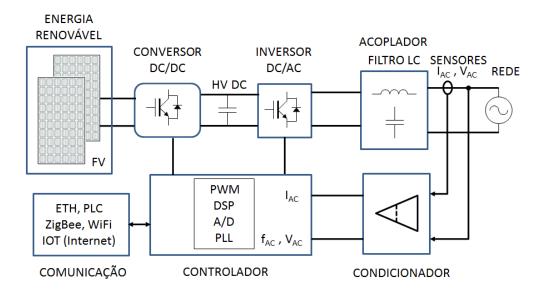

No setor de Energia Renovável, temos o uso para a conversão da energia captada do ambiente, tais como solar, eólica e hidráulica que é transformada ou escalonada para outros níveis para a sua utilização (e.g. Abu-Rub *et al.* (2014, p. 53 e p. 56)). Com relação à energia solar, temos várias aplicações para conversão de energia DC proveniente dos módulos fotovoltaicos (FV), envolvendo a carga inteligente de baterias (DC/DC), busca do ponto de máximo rendimento (MPPT) e conversão em corrente alternada (DC/AC) para alimentação de sistemas de abastecimento isolados ou conectados a rede elétrica (grid) em 60Hz (ou 50Hz).

Para estas aplicações os inversores de energia são os principais equipamentos utilizados (Figura 1.4). Como exemplo, em sistemas FV conectados modernos temos vários conversores acoplados, controlados via DSP que gera sinais PWM que controlam as chaves de potência (IGBT, SiC ou GaN) sincronizando a energia produzida com a rede de alimentação (através das amostras dos sinais condicionados de tensão e corrente, convertidos pelos A/D e processadas no controlador digital), e com comunicação externa que pode ser via rede (PLC), wireless (ZigBee ou WiFi) ou via internet. Com foco neste mercado, temos a necessidade de controladores integrados que englobem tais funcionalidades, tais como controladores *Smart Power* e Módulos de Potência integrados, abrangendo vários tipos de produtos e dispositivos dedicados para aplicação em energia renovável.

Figura 1.4 – Aplicação em energia renovável (solar fotovoltaica, sistema conectado)

Fonte: Maltione (2020).

Outros setores, além destes também requerem sistemas robustos. O setor de Telecomunicações, por exemplo, exibe uma demanda para conversores de energia de ata eficiência e baixo ruído principalmente para alimentação de sistemas de comunicação tais como: radiotransmissores para radiodifusão (broadcasting) ou telefonia móvel, TV analógica e digital, etc. Segundo Liu (2002, p. 1478), a principal aplicação são retificadores AC/DC, que convertem a tensão da rede AC de abastecimento em um barramento DC de -48V, que é distribuído por todo o sistema. Outra parte desta alimentação é feita por conversores DC/DC que convertem a tensão de -48V em alimentações com múltiplas saídas, para alimentar as placas, com circuitos lógicos, analógicos e de RF. A alta qualidade e a robustez são requisitos muito importantes para o sistema, sendo que se pode degradar a qualidade do som, imagens ou dados, exigindo-se assim sistemas com redundância e uso de fontes de alimentação ininterruptas (UPS) com baterias de backup.

Também encontramos aplicações robustas nas áreas da Medicina e Biomédicas, com o crescente surgimento dos equipamentos de diagnóstico e tratamento cada vez mais complexos. As aplicações incluem equipamentos para diagnóstico tais como, imagens de ressonância magnética, tomografia computadorizada, tomografia de emissão de pósitron, Raios-X e ultrassom, equipamentos de hemodiálise, robôs cirúrgicos, *lasers* e monitoramento de pacientes (FLYNN, 2015, p. 32) tais como pressão sanguínea, ECG, EGG etc. Existem ainda também aplicações dedicadas para uso em laboratórios (análises químicas e automação de processos), *Home Care* (camas médicas, CPAP, bombas de infusão) e equipamentos odontológicos.

Além dos requisitos de tamanho reduzido, robustez, funcionalidades e alta eficiência, este setor tem como principal requisito a segurança para o paciente e para o operador (normalizadas pela IEC 60601-1). Questões como isolação e interferência eletromagnética (EMI) são questões fundamentais no projeto, uma vez que muitos destes equipamentos envolvem o uso de alta tensão, devendo-se ter especial atenção com relação às correntes de fuga (FLYNN, 2015, p. 33; CUI, 2017, p. 5).

Com relação à questão da conversão de energia em aplicações extremamente robustas encontramos os setores Aeronáutico (aeronaves), Aeroespacial (satélites e veículos tripulados ou não) e Militar, Segurança e Defesa (armamentos e radares), que exigem o uso de conversores operando initerruptamente com extrema robustez a falhas.

A Tabela 1.1 apresenta resumidamente uma coletânea destas aplicações relacionando com as frequências normalmente utilizadas usando chaves com tecnologias convencionais (Si, IGBT e MOS) e a projeção de um futuro próximo para chaves WBG (SiC e GaN), que já começam a se tornar viáveis.

Tabela 1.1 – Aplicações de Sistemas de Potência

| Área de Aplicação  | Aplicação            | Potência    | Frequências de   | Limites futuros |

|--------------------|----------------------|-------------|------------------|-----------------|

|                    |                      | [W]         | chaveamento [Hz] | para WBG [Hz] * |

| Conversores        | Fontes chaveadas     | 10 a 1k     | 20k a 2M         | 200k a 20M      |

| Energia Renovável  | Inversor isolado     | 500 a 5k    | 10k a 100k       | 100k a 10M      |

|                    | Inversor conectado   | 1k a 50k    | 10k a 100k       | 100k a 10M      |

|                    | Controlador de       | 550 a 5,5k  | 10k a 100k       | 100k a 10M      |

|                    | carga                |             |                  |                 |

|                    | Microinversor        | 180 a 480   | 20k a 500k       | 200k a 50M      |

|                    | Mini-inversor        | 720 a 1,92k | 20k a 500k       | 200k a 50M      |

| Automotivo         | Inversor para HEV    | 3k a 30k    | 50k a 500k       | 500k a 50M      |

|                    | Inversor para HV     | 10k a 180k  | 50k a 500k       | 500k a 50M      |

| Telecomunicações   | Alimentação (UPS)    | 500 a 120k  | 20k a 2M         | 200k a 20M      |

| Industrial         | Alimentação/Fontes   | 100 a 2k    | 20k a 2M         | 2M a 20M        |

|                    | Inversores           | 100 a 20k   | 20k a 500k       | 2M a 50M        |

| Consumo            | Alimentação/Fontes   | 1 a 5k      | 20k a 2M         | 2M a 20M        |

| Equipamentos       | Alimentação/Fontes   | 50 a 2k     | 20k a 2M         | 2M a 20M        |

| Medicina e         | Alimentação/Fontes   | 10 a 1k     | 20k a 2M         | 2M a 20M        |

| Biomedicina        |                      |             |                  |                 |

| Militar, Segurança | Alimentação/Radar    | 300 a 10k   | 50k a 500k       | 500k a 50M      |

| e Defesa           |                      |             |                  |                 |

| Aeronáutica e      | Alimentação/Satélite | 100 a 12k   | 100k a 20M       | 1M a 100M       |

| Aeroespacial       |                      |             |                  |                 |

<sup>\*</sup>Nota: Projeção para uso de tecnologias WBG com chaves SiC ou GaN em futuro próximo.

Fonte: Maltione (2020).

#### 1.1.2 Requisitos de Robustez

Conforme a área de aplicação, temos requisitos específicos com relação às condições de robustez que são necessárias para certo equipamento. Os parâmetros normalmente impactados nos sistemas são a temperatura de operação, o tempo de vida esperado para o equipamento, os níveis de emissão/imunidade de RF (Compatibilidade Eletromagnética - EMC) e descargas eletrostáticas (ESD) suportadas pelo mesmo conforme os mercados de aplicação. Estes requisitos por sua vez impactam nos limites dos parâmetros dos dispositivos de potência usados nestes produtos.

A Tabela 1.2 apresenta resumidamente estes requisitos conforme estas aplicações.

Mercado/Setor Temperatura de Tempo de **EMC** ESD de Aplicação operação vida Consumo 0 a 70°C 5 anos FCC Part 15 Class A +/- 1kV Industrial -40 a 85°C IEC 61.000-4-15 +/- 2kV 5 anos -40 a 150°C Automotivo 10 anos ISO 11452-4/-7 +/- 8kV -25 a 60°C Renovável FCC Part 15 Class B +/- 4kV 5 a 25 anos -55 a 125°C Militar 20 anos MIL STD 461 G +/- 15kV

Tabela 1.2 – Requisitos comuns de robustez conforme mercado de aplicações

Fonte: Maltione (2020).

Conforme podemos verificar na Tabela 1.2, dispositivos utilizados em setores de robustez tais como aplicações automotivas e militares estão sujeitos a especificações mais rígidas com relação à temperatura, EMC e ESD. Outro exemplo são as aplicações para o setor de energia renovável, que exige para alguns produtos, expectativa de tempo de vida superior a 25 anos (que é o tempo de vida esperado para os módulos fotovoltaicos).

#### 1.2 Compatibilidade Eletromagnética

A Compatibilidade Eletromagnética (EMC - Electromagnetic Compatibility) trata-se da capacidade de um equipamento operar em um mesmo ambiente com outros equipamentos, sem causar interferência de RF ou ser disturbado pelos mesmos. O modelo mais empregado para esta situação é o Agressor-Vítima, onde o agressor é a fonte de RF que causa a interferência e a vítima o equipamento que sofre a interferência, como ilustrado na Figura 1.5.

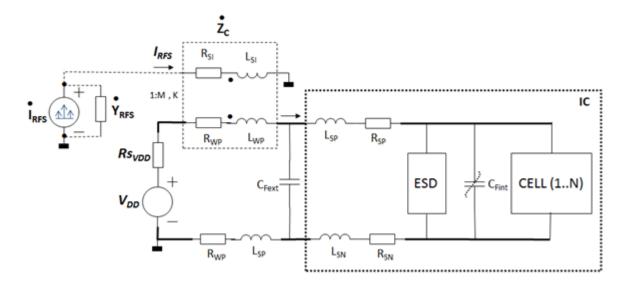

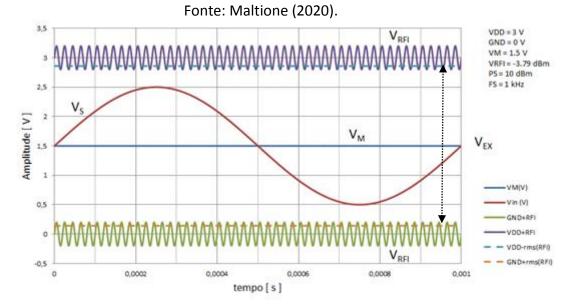

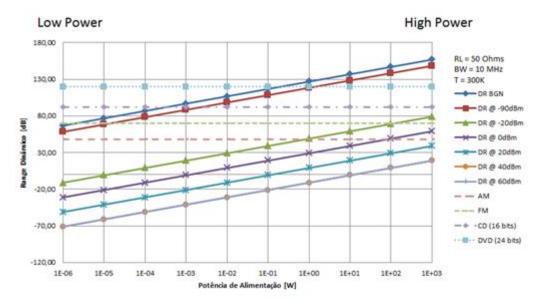

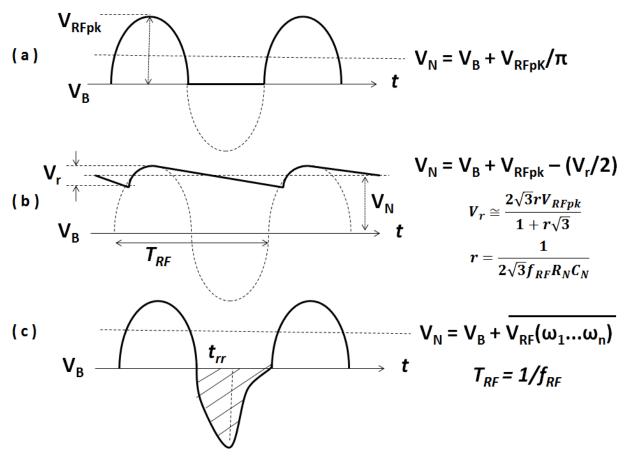

Do ponto de vista da compatibilidade, são definidos conceitos relativos a este modelo de interferência, definindo-se áreas de estudo, no que se refere a quem transmite (emissão) ou quem a recebe (susceptibilidade), tais como ilustrados na Figura 1.6.

Figura 1.5 – Modelo clássico de interferência agressor - vítima. Fonte: Maltione (2020).

RF incidente EMC RF irradiado

Interferência de RF

EMI

(RFI)

Sistema de Conversão de Energia

Vin, lin

Pin

Pout = EFF x Pin

Pout

RF conduzido

Chaveamento em fs

RF conduzido

(EMS) IMUNIDADE

EMISSÃO (EME)

Figura 1.6 – Conceito de interferência de RF aplicado a um sistema de potência. Fonte: Maltione (2020).

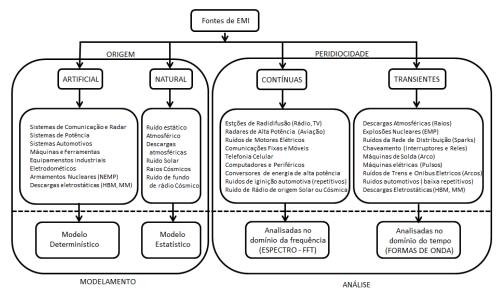

Assim em EMC, o termo EMI (*Electromagnetic Interference*) é usado para designar os fenômenos que tratam de sinais interferentes de uma forma geral (contínuos ou transitórios), sendo o termo (RFI) usado no mesmo contexto, mas aplicado mais a sinais de rádio (RF). Como descrito por Redouté e Steyaert (2010, p. 13), segundo definição da IEC, o termo EMS (*Electromagnetic Susceptibility*) é usado para designar a inabilidade (ou imunidade) do sistema em operar sem degradação com a interferência recebida (vítima), enquanto o termo EME (*Electromagnetic Emission*) é usado para designar os fenômenos de emissão interferentes de uma fonte (agressor).

Evidentemente na prática existem limites para os níveis de sinal em que estes eventos ocorrem, tendo sido ao longo do tempo, estabelecidos e padronizados, como normas de compatibilidade (*Standards*). Os tópicos a seguir discutem brevemente estas questões, desde os conceitos básicos, do surgimento do problema à normalização.

#### 1.2.1 Perspectiva histórica do problema de interferência de RF

A saga pelo desenvolvimento do eletromagnetismo, conforme ilustram alguns autores em suas retrospectivas históricas, desde os primórdios das comunicações sem fio, tais como descreve Redouté e Steyaert (2010, p. 1), começa desde os tempos dos gregos com as

propriedades magnéticas de certas pedras (magnetita), a descoberta da bússola pelos chineses, e ao âmbar amarelo, com propriedades eletrostáticas que ao ser atritado consegue atrair corpos leves. Estes fenômenos naturais, que pareciam eflúvios que emanavam destes materiais, eram fenômenos dissociados, tendo sido somente associados por Orsted em 1820, com a descoberta de que uma corrente elétrica podia defletir uma agulha de uma bússola, correlacionando-se assim os fenômenos elétricos e magnéticos. Muitos contribuíram para estes estudos entre eles Gauss, Ampere, Thomson, Volta e Faraday dentre outros, para descrição destes fenômenos, que acabaram sendo unificados de forma elegante e matemática por Maxwell, que unindo os trabalhos anteriores, compilou em seu tratado sobre eletromagnetismo, um conjunto de equações que descreviam os fenômenos, e que acabaram por ser o substrato para os trabalhos de Lorentz e Poincaré, culminando com a publicação da teoria da relatividade restrita de Einstein em 1905.

Entretanto um fato interessante, é que o trabalho de Maxwell era uma compilação, que apesar de brilhante, era teórica sobre o eletromagnetismo, sem a demonstração física de suas conclusões. Maxwell demonstra que as ondas eletromagnéticas, tem o mesmo comportamento da luz, assim como suas propriedades de difração e reflexão, tendo assim a mesma essência. Neste tempo devido ao forte embasamento da mecânica Newtoniana, era necessário imaginar um meio físico para a propagação dos sinais eletromagnéticos (éter), tendo sido descrito, nas próprias palavras de Maxwell como:

"If it should be found that the velocity of propagation of electromagnetic disturbances is the same as the velocity of light, and this not only in air, but in other transparent media, we shall have strong reasons for believing that light is an electromagnetic phenomenon, and the combination of the optical with the electrical evidence will produce a conviction of the reality of the medium similar to that which we obtain, in the case of other kinds of matter, from the combined evidence of the senses." (MAXWELL, 1873, Vol. 2, Chapter XX - Electromagnetic Theory of Light, p. 383).

. .

"Hence the ondulatory theory of light has met with much opposition, directed not against its failure to explain the phenomena, but against its assumption of the existence of a medium in which light is propagated." (MAXWELL, 1873, Vol. 2, Chapter XXIII - Theories of Action at a Distance, p. 437).

. . .

"Hence all these theories lead to the conception of a medium in which the propagation takes place, and if we admit this medium as an hypothesis, I think it ought to occupy a prominent place in our investigations, and that we ought to endeavour to construct a mental representation of all the details of its action, and this has been my constant aim in this treatise." (MAXWELL, 1873, Vol. 2, Chapter XXIII - Theories of Action at a Distance, p. 438).

Estes conceitos levaram a várias estimativas para medidas da velocidade da luz, como descritos em Maxwell (1873, Vol. 2, p. 387), onde a velocidade da luz é comparada com unidades elétricas. A questão da necessidade do éter para a propagação da luz, só foi quebrada no tempo de Einstein, com a conclusão que as ondas eletromagnéticas podiam se propagar no vácuo, sem necessidade de um meio físico, pela interação dos campos elétricos e magnéticos ortogonais similarmente ao comportamento da luz.

Do ponto de vista do contexto da tese, em relação às comunicações sem fio e aos fenômenos de interferência eletromagnéticos, convém ressaltar que a sua base está na verdade relacionada ao trabalho de Heinrich Hertz.

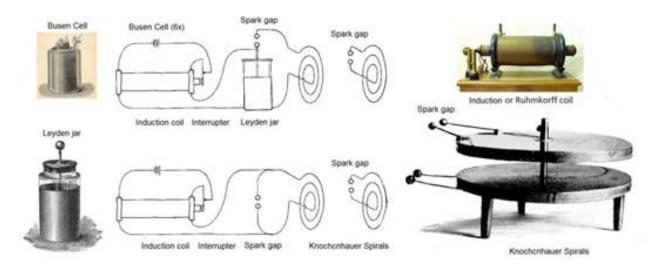

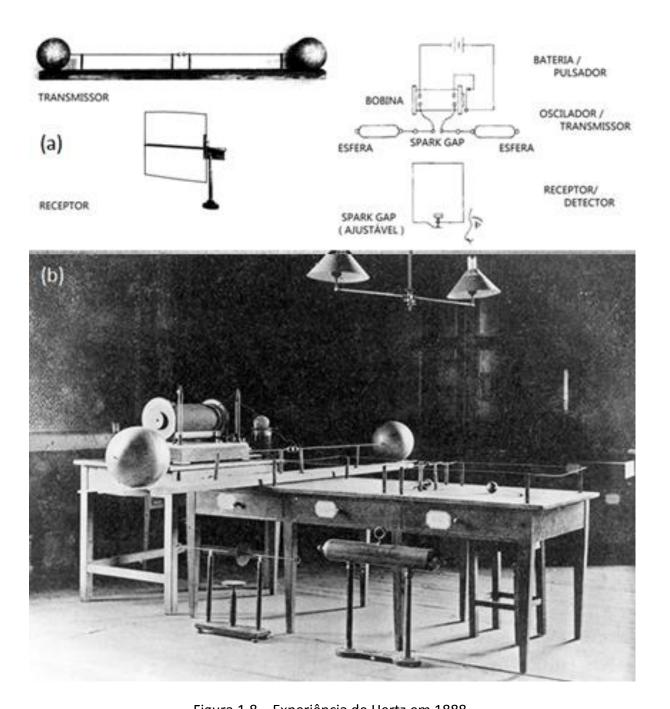

Hertz, conhecendo as previsões de Maxwell de 1864, que previu que as ondas eletromagnéticas podiam se propagar no espaço livre na velocidade da luz, desejava fazer experimentos com ondas dentro das dimensões de um laboratório, para verificar propriedades tais como: velocidade de propagação nos materiais, polarização, reflexão e difração. Na época, eram conhecidos os experimentos, para gerar ondas oscilatórias que podiam ser induzidas através de um circuito ressonante, composto de uma bobina de indução (*Ruhmkorff coil*), um capacitor (*Leyden jar*) acopladas às espirais Knochcnhauer (espécie de bobinas planas, com acoplamento a ar), as quais tinham os circuitos fechados por centelhadores (*spark gaps*). A alimentação do circuito era feita por pilhas zinco-carbono ancestrais conectadas em série (*Busen cells*).

Estes aparatos eram chaveados por interruptores (muitas vezes usando mercúrio, para evitar rebotes), produzindo um largo di/dt no primário da bobina que gerava uma alta tensão transitória oscilante no secundário da bobina. Isto, por sua vez gerava um arco no centelhador do primário, fechando assim o circuito e induzindo então uma tensão na espiral secundária que por sua vez fechava o circuito, gerando um arco no centelhador do secundário. Esta experiência demonstrava que as ondas oscilantes se propagavam através do ar e geravam uma tensão na espiral secundária, distante da outra. Entretanto Hertz estimou que se os comprimentos destas ondas fossem da ordem de 30m, estes tamanhos seriam incompatíveis com as dimensões para estudo em laboratório (APPLEYARD, 1930). Assim substituiu a garrafa de *Layden* por um centelhador de modo a ter uma menor capacitância e, portanto, maior frequência de oscilação e consequentemente menor comprimento de onda (Figura 1.7).

Figura 1.7 – Geração de ondas oscilatórias usando espirais de Knochcnhauer.

Fonte: Composição realizada pelo autor a partir de Appleyard (1930, p. 116 e 118)

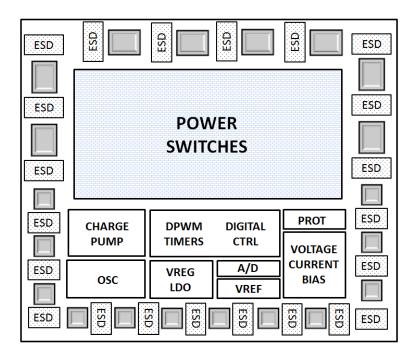

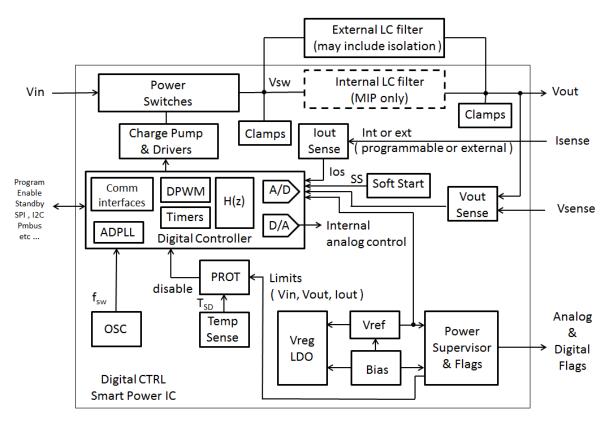

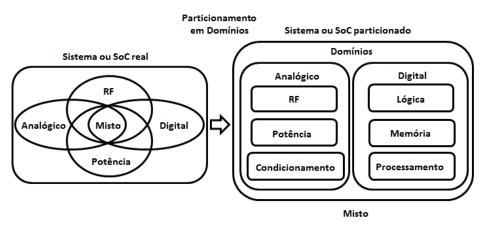

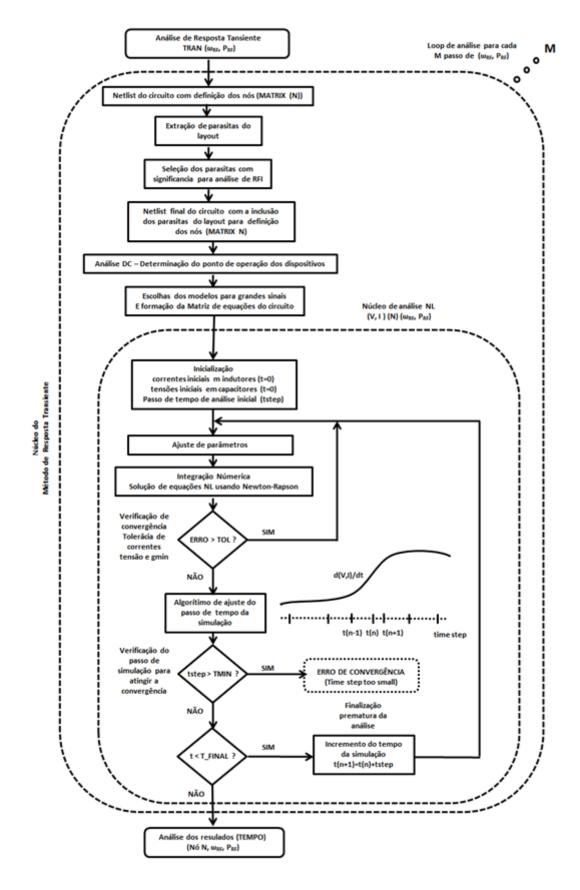

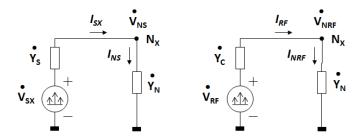

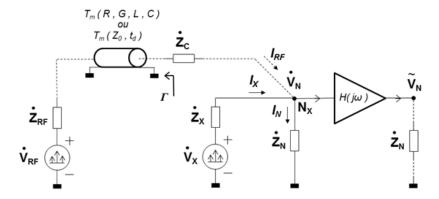

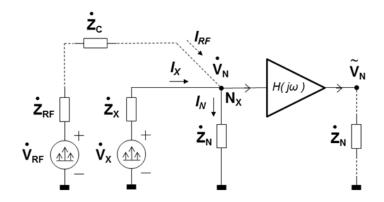

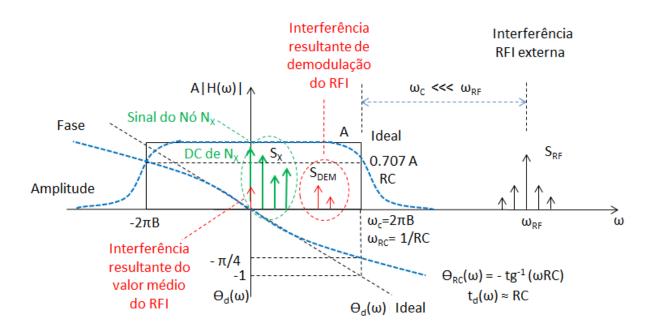

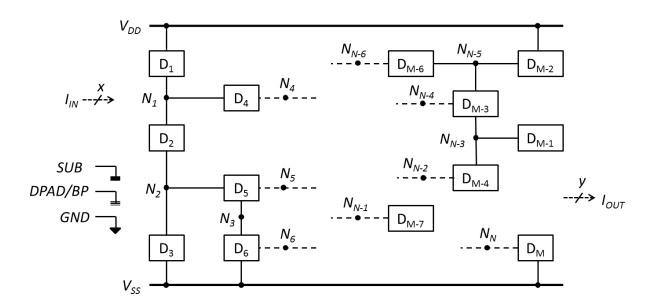

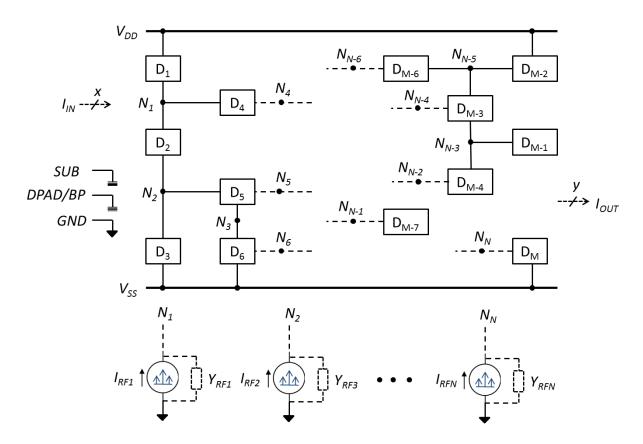

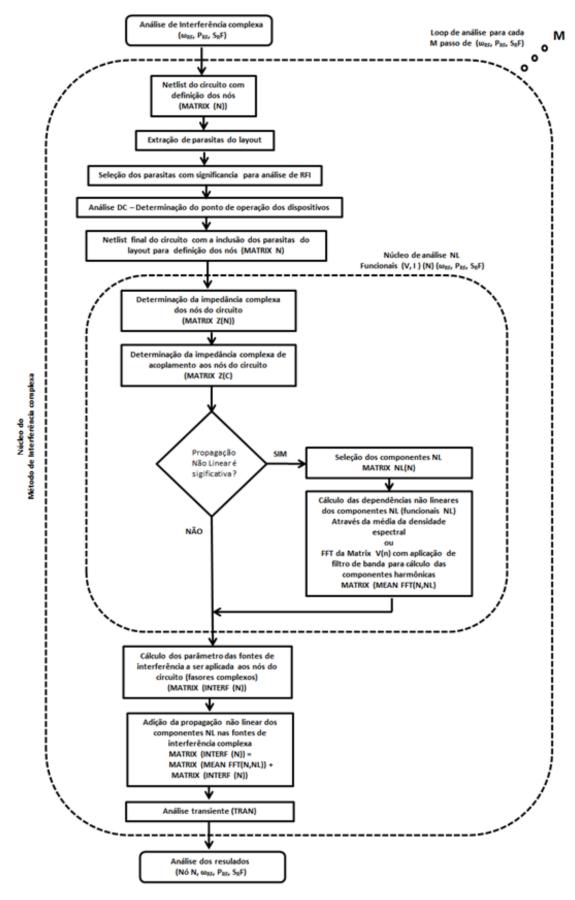

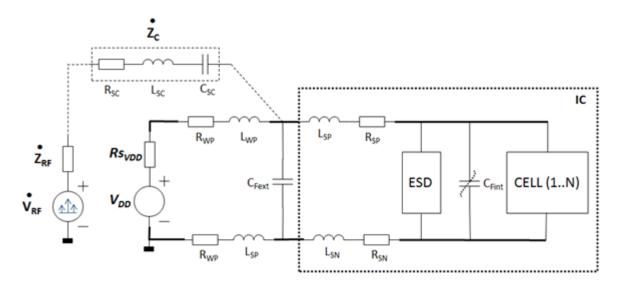

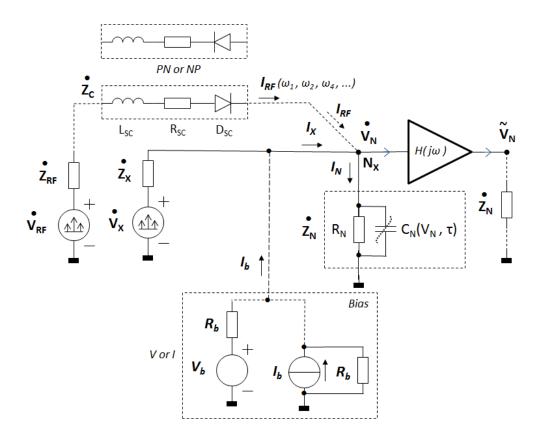

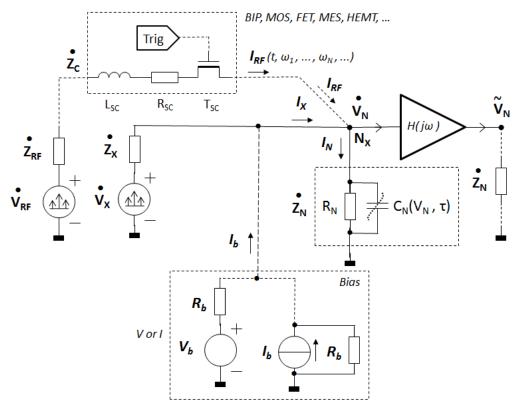

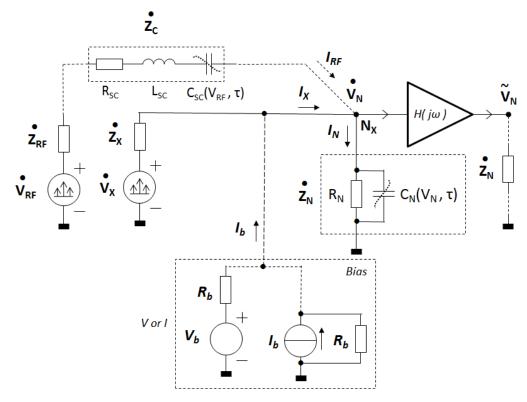

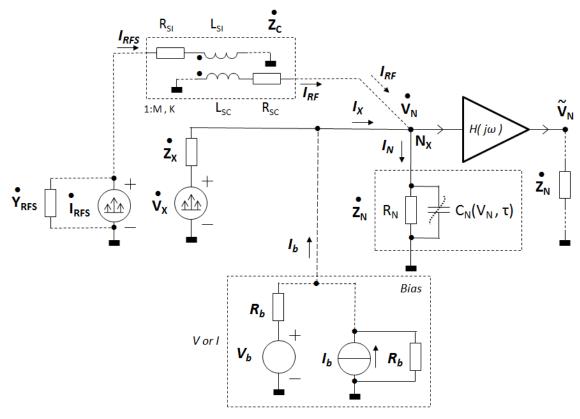

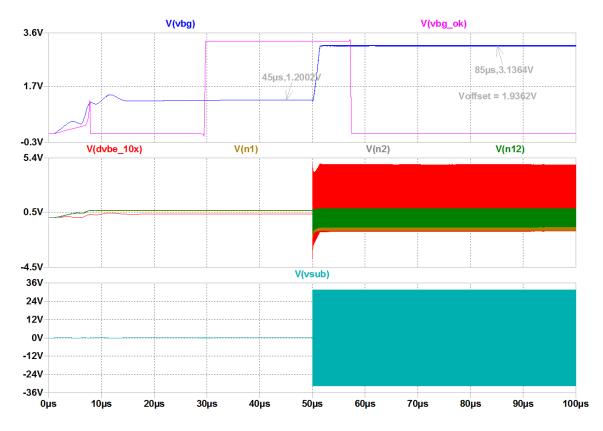

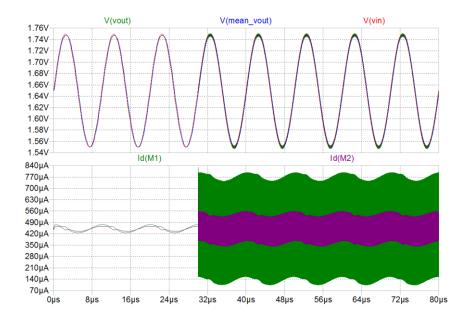

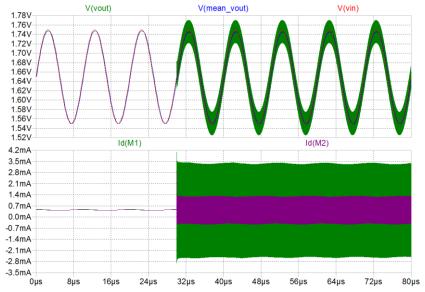

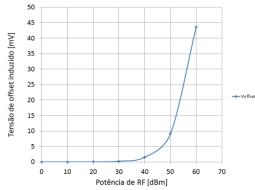

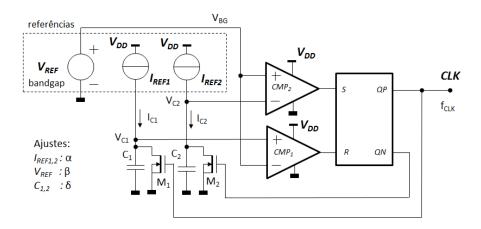

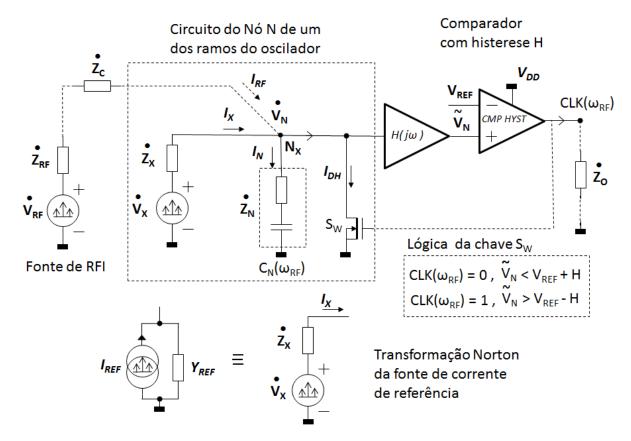

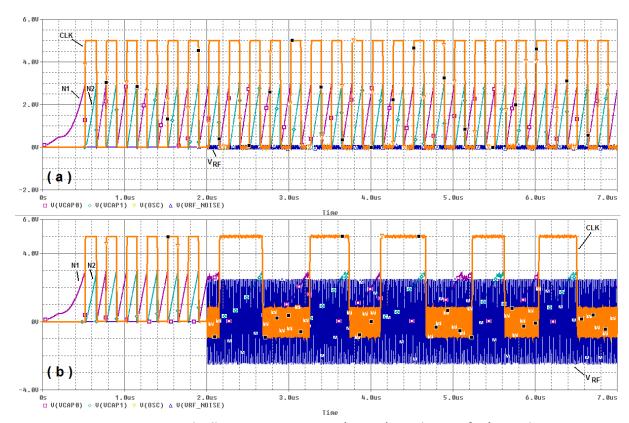

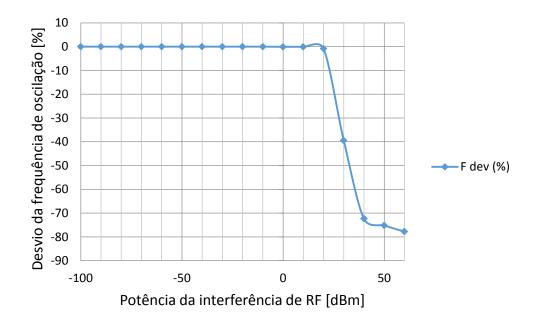

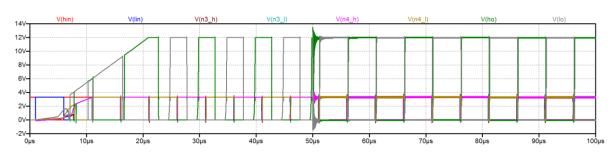

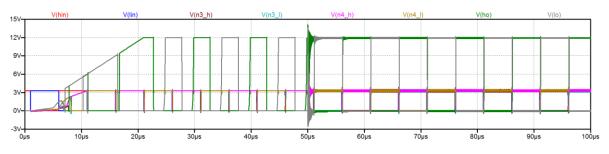

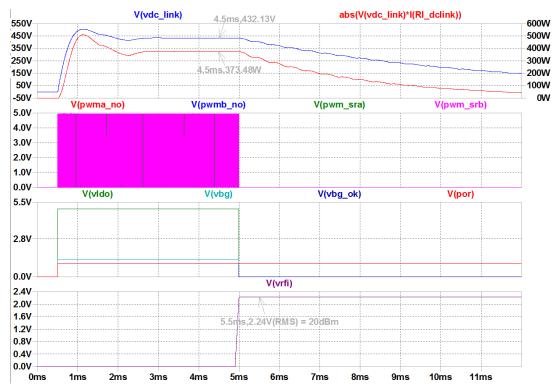

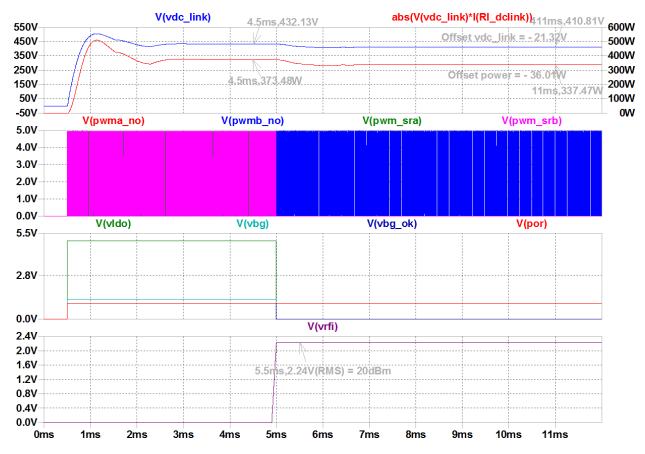

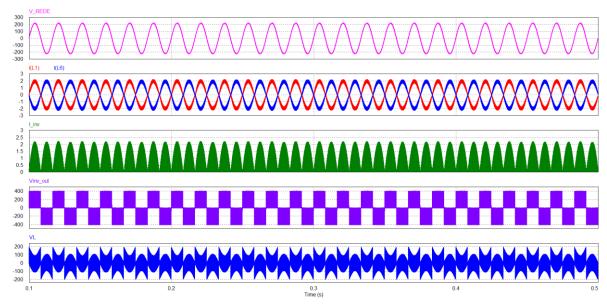

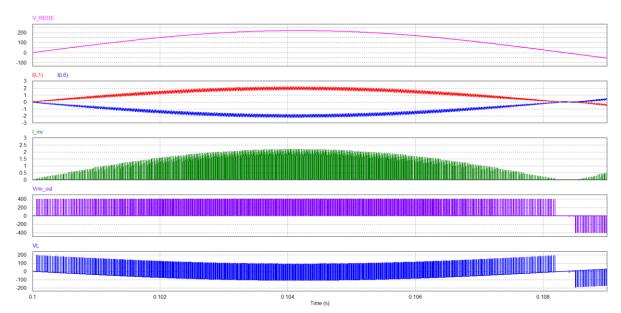

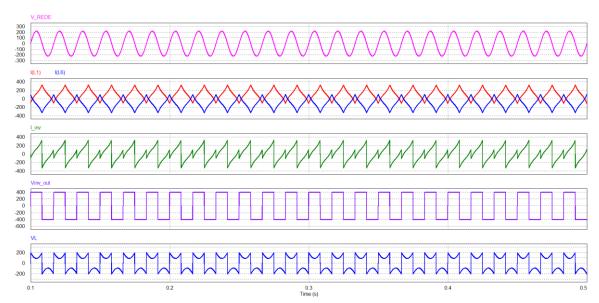

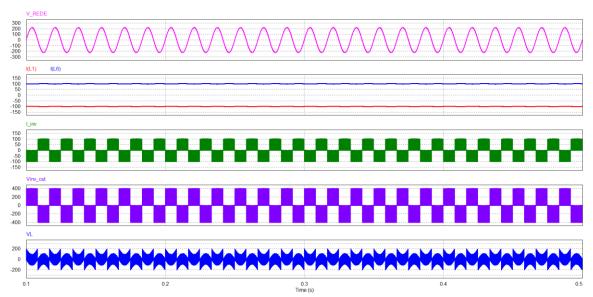

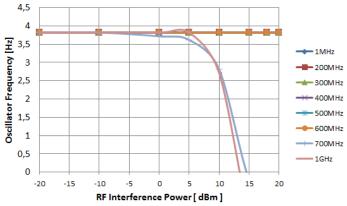

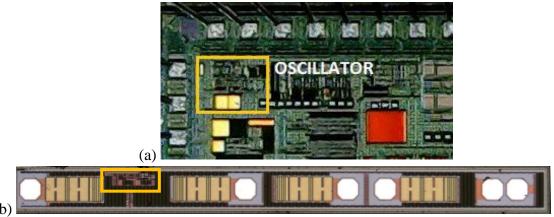

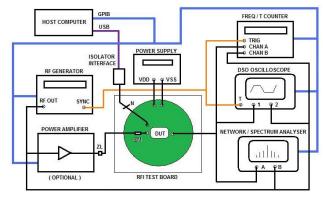

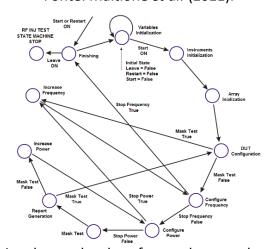

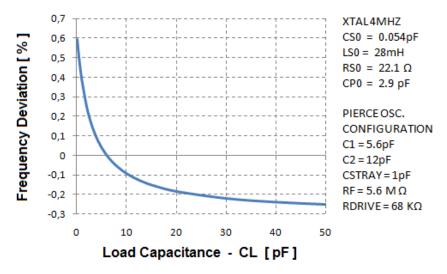

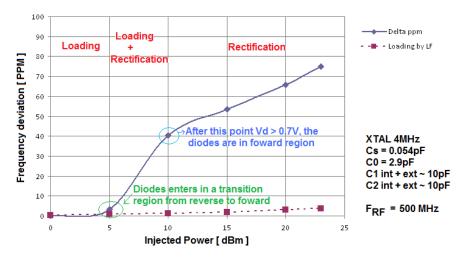

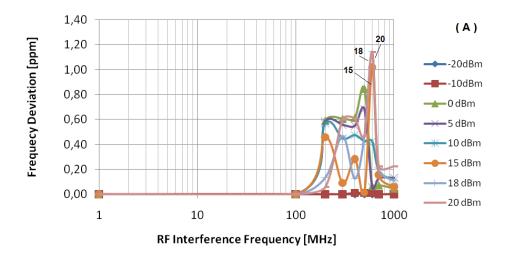

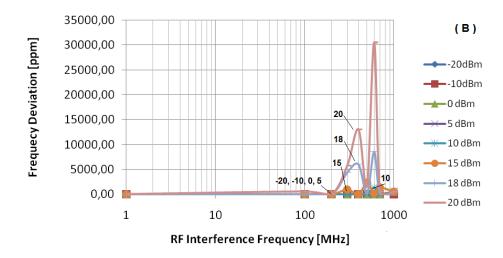

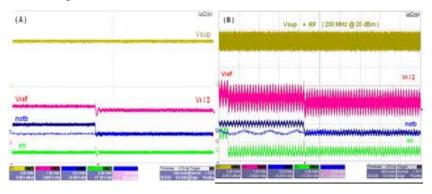

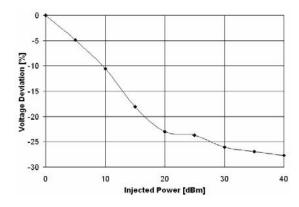

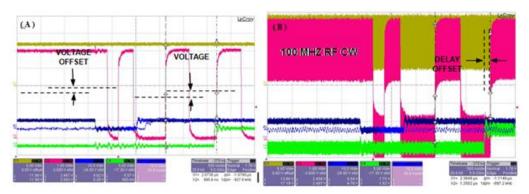

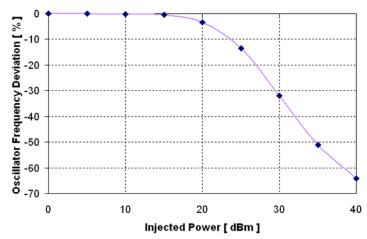

com fotos da Wikipédia (Busen Cell, Leyden jar e Ruhmkorff coil).