#### UNIVERSIDADE ESTADUAL DE CAMPINAS INSTITUTO DE MATÉMATICA, ESTATISTICA E CIÉNCIA DA COMPUTAÇÃO DEPARTAMENTO DE CIÊNCIA DA COMPUTAÇÃO

# TÉCNICAS DE OTIMIZAÇÃO DE CÓDIGO PARA ARQUITETURAS RISC

por

Galileu Batista de Sousa<sup>1</sup>

29 de junho de 1992

UNICAMP WELIOTECA CENTRAL

ae-mail: galileu@dcc.unicamp.br

### Técnicas de Otimização de Código para Arquiteturas RISC

Este exemplar corresponde a redação final da tese devidamente corrigida pelo Sr. Galileu Batista de Sousa e aprovada pela Comissão Julgadora.

Campinas, 29 de junho de 1992.

Prof. Dr.

Tamarz Kowaltowski

Dissertação apresentada ao Instituto de Matemática, Estatística e Ciência da Computação, UNICAMP, como requisito parcial para a obtenção do Título de MESTRE em Ciência da Computação.

## Técnicas de Otimização de Código para Arquiteturas RISC

Galileu Batista de Sousa

Dissertação apresentada em 29 de Junho de 1992.

#### Banca Examinadora:

Dr. Tomasz Kowaltowski – UNICAMP – Orientador

Dr. Roberto da Silva Bigonha - UFMG

Dr. Ricardo de Oliveira Anido - UNICAMP

"Se um dia, já homem feito e realizado, sentires que a terra cede aos teus pés, que tuas obras se desmoronaram, que não há ninguém à tua volta, para te estender a mão, esquece a tua maturidade, passa pela tua mocidade, volta à tua infância e balbucia entre lágrimas e esperanças as últimas palavras que sempre te restarão na alma: minha mãe, meu pai."

também dedico ao TD, Jr., Ciamel e, em especial, ao nosso pequeno Tiago; sem quaisquer restrições quanto à reorganização.

## Agradecimentos

"O homem põe limites às trevas e explora até o extremo as grutas mais sombrias ... traz à luz o que está escondido. A sabedoría, porém, de onde é tirada? onde está a jazida da inteligência? só Deus a conhece ... mas ele disse ao homem: 'A sabedoría consiste em temer ao Senhor, e a inteligência está em afastar-se do mal'"

J6 - 28

Esta dissertação não é só minha. Ela é resultado do apoio técnico, financeiro e, sobretudo, emocional de várias pessoas ou instituições, pois 'muitos temores nascem do cansaço e da solidão'. Eu gostaria de lembrar especialmente algumas.

O Tomasz pelo apoio e paciência em alguns momentos críticos do tempo que trabalhamos juntos. Sua orientação e visão de computação foi, para mím, importante em inúmeros aspectos. A capacidade de contornar os meus problemas de comunicação também contribuiu para um resultado a contento.

Meus amigos de casa: Herbert Hebão Baier, Alfredo Cacão Jackson, Zé Guimarães e Mestre Léo foram parte importante para superar dificuldades e prover incentivos. Meu obrigado também por aturarem o meu mau humor, nem sempre condizente com o ótimo relacionamento que mantemos.

Com mais alguns amigos da graduação ainda compartilho vários sonhos e a esperança de um dia podermos realizá-los. Em especial estão José Leite Jr., Mário Sérgio Pinto e Ricardo Sobral; este cuídou com esmero dos meus interesses em Fortaleza enquanto estive por aqui.

O pessoal da FUNCEME sempre foi amigo e esteve pronto a ajudar; em particular, Francisco Lopes Viana e Manuel Pereira da Costa deram seu apoio em várias frentes, normalmente sem exigir coisa alguma em troca. A eles a minha profunda gratidão, que espero transformar em trabalho muito em breve.

Norma Suelly propôs o desafio de um mestrado. Meus agradecimentos não poderiam excluí-la. Minha família sempre foi fonte constante de apoio. Minha Mãe é indescritível; é Mãe. Ela nunca compreendeu o porquê desta separação, porém sempre esteve pronta a ouvir meus argumentos. Meus irmãos sempre foram amigos e companheiros. Os primos: Johnson e Otacílio Cabec também são como irmãos. Tio Dema e Vô têm procurado ser, nos últimos oito anos, o pai que perdi, mas que está presente em todas as minhas reflexões. Aos demais familiares também agradeço a força.

Ciamel foi mais que eu esperava: sempre paciente e compreensiva, ela nunca criticou o meu desejo de recomeçar, mesmo quando já passara a hora de finalizar. Providenciar os momentos de diversão que me fizeram desligar dos problemas técnicos também ficou a seu cargo. Finalmente, sua dedicação a Tiago nestes últimos meses amenizou a saudade e fez com que eu pudesse confiá-la também o papel de Pai. Agora, espero retribuir em dobro o que ambos são e têm feito por mim.

Agradeço ao Conselho Nacional de Desenvolvimento Científico e Tecnológico - CNPq - que deu o suporte financeiro à execução do Programa de Mestrado e à Fundação de Amparo à Pesquisa do Estado de São Paulo - FAPESP - que viabilizou a parte final desta pesquisa.

### Abstract

Reduced Instruction Set Computers (RISCs) offer higher performance through their very simple instruction repertoire and its efficient hardware implementation. On the other hand, studies of object code generated by compilers for high level languages have shown that the most frequently executed instructions are exactly the simplest ones. The improvement in performance of a general purpose computer is thus result of an integrated approach to compiler construction and architecture. These ideas have influenced design concepts in both areas.

In this dissertation we try to characterize these new architectures and their relation to compiling techniques, especially code optimization. Several aspects related to RISCs, such as register allocation and pipelines optimization are discussed. Some of the ideas discussed or proposed were tried within a production compiling system on SPARC (Sun Microsystems) architecture.

### Sumário

Computadores com conjunto de instruções reduzido (RISC) buscam a maximização do desempenho oferecendo instruções muito primitivas e de implementação eficiente. Por outro lado, análises de código objeto gerado por tradutores de linguagens de alto nível mostram que as instruções mais freqüentemente executadas são também as mais elementares. O aumento do desempenho de um computador de uso geral é, portanto, resultante de uma abordagem integrada entre compiladores e arquitetura. Estes conceitos têm mudado parcialmente as métricas de projeto nas duas áreas.

Este trabalho consiste em caracterizar estas novas arquiteturas bem como seus relacionamentos com compiladores, ou mais precisamente, otimizadores de código. Aborda-se problemas fortemente identificados com o modelo RISC, tais como alocação de registradores e otimização de pipelines. Várias técnicas para tratar estes problemas são discutidas. Para validar as idéias descritas e/ou propostas, algumas das otimizações foram implementadas em um compilador de produção para a arquitetura SPARC.

## Conteúdo

| 1 | Int           | rodução 1                                        |

|---|---------------|--------------------------------------------------|

|   | 1.1           | Alocação de Registradores                        |

|   | 1.2           | Otimização de Pipelines                          |

|   | 1.3           | Investigações                                    |

|   | 1.4           | Terminologia                                     |

|   | 1.5           | Os Benchmarks                                    |

|   | 1.6           | Organização da Dissertação                       |

| 2 | $\mathbf{Ar}$ | quiteturas RISC 7                                |

|   | 2.1           | Introdução                                       |

|   | 2.2           | Evolução das Arquiteturas                        |

|   | 2.3           | As Origens de RISC                               |

|   | 2.4           | Princípios de Projeto em RISC                    |

|   |               | 2.4.1 Instruções de um ciclo de relógio          |

|   |               | 2.4.2 Poucas instruções e modos de endereçamento |

|   |               | 2.4.3 Arquitetura LOAD/STORE                     |

|   |               | 2.4.4 Grande conjunto de registradores           |

|   |               | 2.4.5 Pipelining em alta escala                  |

|   |               | 2.4.6 Eliminação do microcódigo                  |

|   |               | 2.4.7 Formato fixo de instruções                 |

|   | 2.5           | Interação Compiladores/Arquitetura               |

|   | 2.6           | RISC versus CISC                                 |

|   | 2.7           | Ponto Flutuante em RISC                          |

|   | 2.8           | Segunda Geração de RISC                          |

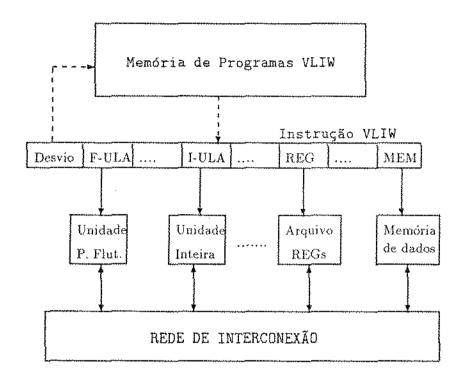

|   |               | 2.8.1 VLIW                                       |

|   |               | 2.8.2 Superescalares                             |

|   | 2.9           | Conclusões                                       |

| 3 | Ar            | quitetura SPARC 25                               |

|   | 3.1           | Introdução                                       |

|   | 3.2           | Visão Geral                                      |

|   | 3.3           | Interação entre hardware e software              |

|   |               | 3.3.1 Convenções de Software                     |

|   |               | 3.3.2 Gerenciamento de Janelas                   |

|   | 3.4           | Implementação da Arquitetura                     |

|   |     | 3.4.1 Custo e Latência das Instruções                                      | 2 |

|---|-----|----------------------------------------------------------------------------|---|

|   |     | 3.4.2 O cache                                                              | 2 |

|   |     | 3.4.3 A UPF 33                                                             | 3 |

|   | 3.5 | Reorganização de Código na SPARC                                           | 4 |

|   | 3.6 | Conclusões                                                                 | 5 |

| 4 | Alo | ocação Intraprocedimental de Registradores 37                              | ĩ |

|   | 4.1 | Introdução                                                                 | Ī |

|   | 4.2 | Alocação em Blocos Básicos                                                 | ) |

|   | 4.3 | Alocação em Malhas                                                         | ) |

|   | 4.4 | Alocação Global                                                            | ļ |

|   |     | 4.4.1 Alocação por Coloração de Grafos                                     | 3 |

|   |     | 4.4.2 Alocação por Coloração baseada em Prioridades                        | 6 |

|   |     | 4.4.3 Alocação por Coloração Hierárquica                                   | ) |

|   | 4.5 | Particularidades no Uso de Registradores                                   | ō |

|   | 4.6 | Conclusões                                                                 | 3 |

| 5 | Alc | ocação Interprocedimental de Registradores 66                              | ) |

|   | 5.1 | Introdução                                                                 | j |

|   | 5.2 | Esquemas de Alocação em Hardware                                           | 2 |

|   | 5.3 | Esquemas de Alocação em Software                                           | 2 |

|   |     | 5.3.1 Alocação em Tempo de Ligação                                         | 3 |

|   |     | 5.3.2 Alocação Interprocedimental Cooperativa                              | ĵ |

|   |     | 5.3.3 Alocação Interprocedimental em Um Passo                              | ğ |

|   |     | 5.3.4 Alocação Interprocedimental em Duas Fases                            | ) |

|   | 5.4 | Alocação em hardware ou software?                                          | 1 |

|   | 5.5 | Conclusões                                                                 |   |

| 6 | Re  | organização de Instruções 78                                               | 3 |

|   | 6.1 | Introdução                                                                 | 3 |

|   | 6.2 | Propriedades da Reorganização                                              |   |

|   | 6.3 | Reorganização em Blocos Básicos                                            |   |

|   |     | 6.3.1 Reorganização Ótima para Interlocks de Um ciclo                      |   |

|   |     | 6.3.2 Reorganização com Dependências Estruturais de Um Ciclo 8             |   |

|   |     | 6.3.3 Reorganização com Interlocks Arbitrários                             |   |

|   | 6.4 | Reorganização além de Blocos Básicos                                       | 0 |

|   |     | 6.4.1 Desmembramento de Malhas                                             | 0 |

|   |     | 6.4.2 Trace Scheduling                                                     | - |

|   |     | 6.4.3 Pipeline de Software                                                 | õ |

|   | 6.5 | Integração entre Alocação de Registradores e Reorganização de Instruções 9 | 8 |

|   |     | 6.5.1 Remapeamento em Hardware                                             | 9 |

|   |     | 6.5.2 Alocação com Custo de Reorganização                                  | 0 |

|   | 8.8 | Candusãos                                                                  |   |

| 7 | $\mathbf{E}\mathbf{x}$ | perimentos e Experiências 103                                   |

|---|------------------------|-----------------------------------------------------------------|

|   | 7.1                    | Introdução,                                                     |

|   | 7.2                    | GCC                                                             |

|   |                        | 7.2.1 Estrutura do Compilador                                   |

|   |                        | 7.2.2 Transporte de GCC e Estratégia de Geração de Código 104   |

|   |                        | 7.2.3 Otimização                                                |

|   | 7.3                    | Passagem de Parâmetros em Registradores de Ponto Flutuante      |

|   | 7.4                    | Otimização do Uso de Janelas na SPARC                           |

|   | 7.5                    | Alocação Interprocedimental de Registradores de Ponto Flutuante |

|   | 7.6                    | Reorganização de Instruções                                     |

|   |                        | 7.6.1 Detalhes da Implementação                                 |

|   |                        | 7.6.2 Avaliação                                                 |

|   |                        | 7.6.3 Investigações                                             |

|   |                        | 7.6.4 Comentários                                               |

|   | 7.7                    | 110                                                             |

| 8 | Co                     | nclusão 120                                                     |

| _ | 8.1                    | Contribuições                                                   |

|   | 8.2                    | Trabalhos Futuros                                               |

| A | Im                     | plementações RISC - Características 124                         |

## Lista de Figuras

| 1.1 | Execução de uma sequência de instruções no pipeline                                   |

|-----|---------------------------------------------------------------------------------------|

| 2.1 | Janelas de Registradores                                                              |

| 2.2 | Efeito da instrução de desvio na execução pipelined                                   |

| 2.3 | Diagrama de blocos de uma arquitetura VLIW genérica                                   |

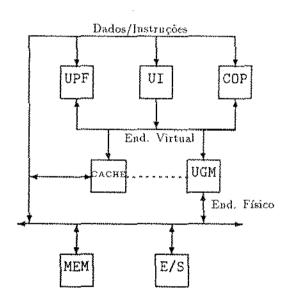

| 3.1 | Diagrama de blocos da SPARC                                                           |

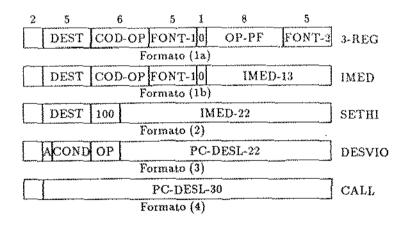

| 3.2 | Formatos de Instruções na SPARC                                                       |

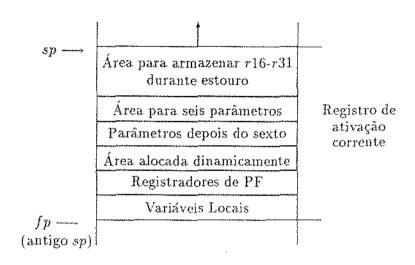

| 3.3 | Pilha de execução de um programa                                                      |

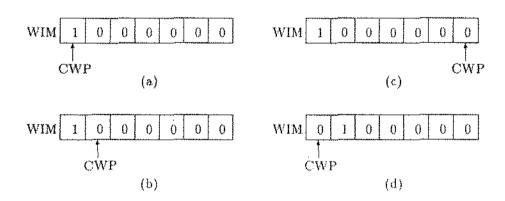

| 3.4 | Gerenciamento do mecanismo de janelas deslizantes                                     |

| 3.5 | Reorganização em construções repete-até                                               |

| 3.6 | Reorganização em construções se-então-senão                                           |

| 4.1 | Variáveis vivas em um trecho sequencial de programa                                   |

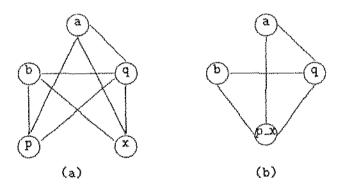

| 4.2 | (a) Uma função escrita em Linguagem C e (b) grafo de interferências dos candidatos    |

|     | a alocação de registradores (método convencional)                                     |

| 4.3 | O grafo de interferências referente ao código intermediário da Figura 4.2 de acordo   |

|     | com a sugestão de Chaitin: sem (a) e com subsumption (b)                              |

| 4.4 | Alocação por coloração de grafos                                                      |

| 4.5 | Alocação por coloração baseada em prioridades                                         |

| 4.6 | Divisão de trechos de vida de uma variável                                            |

| 4.7 | Divisão do grafo de controle de fluxo de um programa em tiles                         |

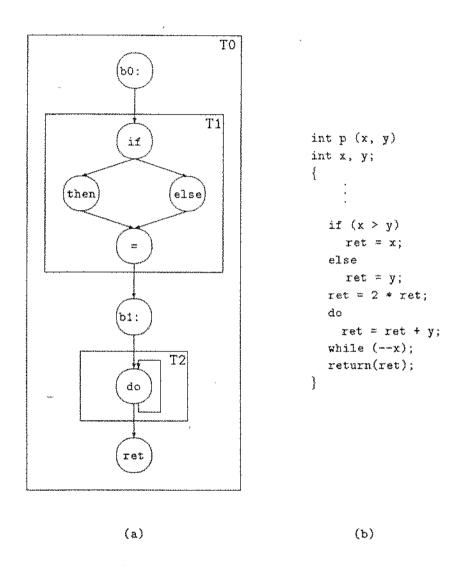

| 4.8 | (a) Um programa em C e sua possível representação intermediária (b) 57                |

| 4.9 | (a) O grafo de interferências referente ao código intermediário da Figura 4.8 e (b) o |

|     | código final após a associação de registradores                                       |

| 5.1 | Chamadas de procedimento em um programa simples                                       |

| 5.2 | Código anotado para alocação em tempo de ligação                                      |

| 5.3 | Variáveis e grupos para um programa simples                                           |

| 5.4 | Um grafo de chamadas recursivo e registradores usados                                 |

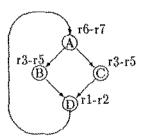

| 5.5 | Grafo com chamada indireta                                                            |

| 5.6 | Propagação de registradores                                                           |

| 5.7 | Tratamento de recursão: (a) Wall; (b) Steenkiste                                      |

| 5.8 | Distribuição de registradores em um programa                                          |

| 5.9 | Ambiente para alocação interprocedimental                                             |

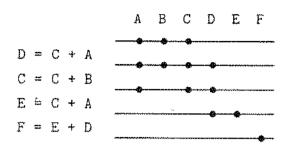

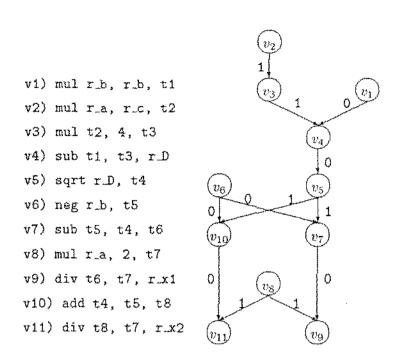

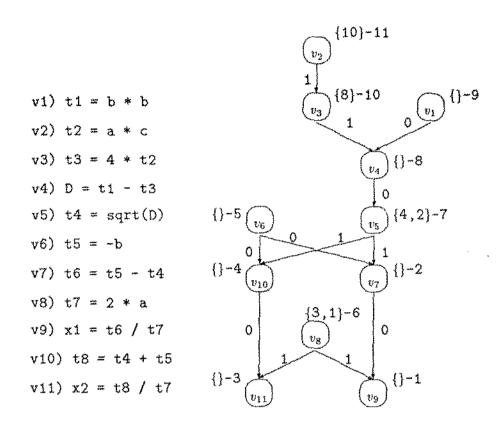

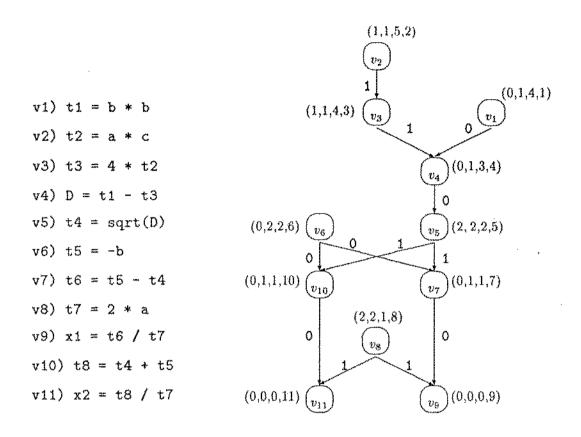

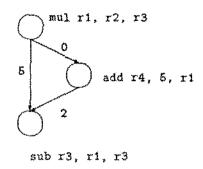

| 6.1  | Um grafo de dependência de dados para cálculo de raízes de equação de grau 2 81      |

|------|--------------------------------------------------------------------------------------|

| 6.2  | Serialização para dependências estruturais                                           |

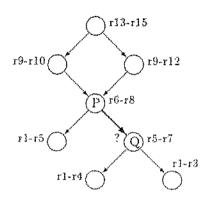

| 6.3  | Um exemplo da aplicação do algoritmo de Bernstein                                    |

| 6.4  | Um exemplo da aplicação do algoritmo de Gibbons e Muchnick                           |

| 6.5  | Uma malha escrita em C: (a) antes e (b) após aplicado o desmembramento 91            |

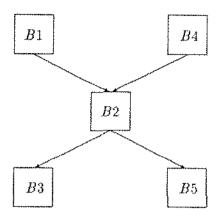

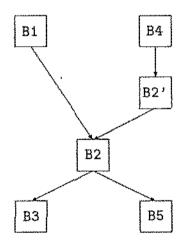

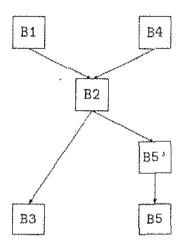

| 6.6  | Grafo de fluxo de controle "genérico"                                                |

| 6.7  | Eseitos da emissão de código de compensação em trace scheduling - parte 1 94         |

| 6.8  | Efeitos da emissão de código de compensação em trace scheduling - parte 2 95         |

| 6.9  | Um exemplo de pipeline de software                                                   |

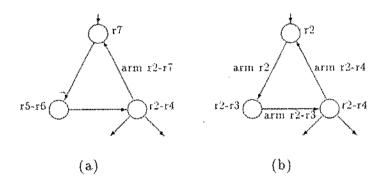

| 6.10 | Código SPARC para somar três variáveis: a) usa dois registradores e gasta 13 ciclos; |

|      | b) usa três registradores e gasta 11 ciclos                                          |

| 7.1  | Estrutura do Gnu C Compiler - GCC                                                    |

| 7.2  | Benefício de arestas transitivas no grafo de dependências                            |

|      |                                                                                      |

|      |                                                                                      |

## Lista de Tabelas

| 2.1 | Frequência percentual de construções em línguagens de alto nível                 | 9   |

|-----|----------------------------------------------------------------------------------|-----|

| 2.2 | Freqüência percentual de: (a) Termos por atribuição; (b) Parámetros passados por |     |

|     |                                                                                  | 9   |

| 2.3 | Freqüência e reorganização (sobre código otimizado) de desvios na SPARC          | 16  |

| 2.4 | Efeito de otimização sobre o número de desvios,,,,                               | 17  |

| 3.1 | Custo e Latência das instruções na UI                                            | 33  |

| 3.2 | Execução da instrução seguindo um desvio                                         | 34  |

| 4.1 | Número médio de registradores (de uso geral) necessários por procedimento        | 43  |

| 5.1 | Freqüência de overflow/underflow de janelas na SPARC                             | 76  |

| 6.1 | Critérios para movimentação de instruções entre blocos básicos da Figura 6.6     | 92  |

| 7.1 | Efeito da convenção de passagem de parâmetros na SPARC                           | 108 |

| 7.2 | Custos e Laténcias usadas na reorganização de instruções                         | 13  |

| 7.3 | Redução no tempo de execução após reorganização                                  | 15  |

| 7.4 | O Tamanho dos blocos básicos                                                     | 16  |

| 7.5 | Detalhamento do preenchimento de slots de desvios                                | 16  |

| 7.6 | Redução no número de ciclos (estáticos) após reorganização                       | 17  |

| 7.7 | Estimativa da otimização máxima devida a reorganização                           | 117 |

| 7.8 | Estimativa do renomeamento (perfeito) de registradores no tempo de execução      | 118 |

| 7.9 | Grau de paralelismo médio por bloco básico                                       | 118 |

| A.1 | Características gerais                                                           | 124 |

| A.2 | Conjuntos de registradores                                                       | 124 |

| A 3 | Modos de enderecamento                                                           | 125 |

### Capítulo 1

## Introdução

"However, if I had waited long enough I probably would never have written anything at all since there is a tendency when I really begin to learn something about a thing: not write about it ... every year I know there is more to learn, but I know some things which may be interesting now."

Ernest Hemingway

A avalanche de publicidade em torno de máquinas RISC – Reduced Instruction Set Computers – tem resultado em muita atividade científica e comercial em torno de projetos que integram fortemente arquitetura, compiladores e sistemas operacionais como meio de maximizar o desempenho de programas escritos em linguagens de alto nível.

Tecnicamente, a discussão concentra-se em determinar que métricas de arquitetura são mais adequadas para garantir maior desempenho de computadores de uso geral. A principal controvérsia está em torno da definição do conjunto de instruções oferecido pelo processador. RISCs se baseiam na capacidade dos compiladores gerarem código de boa qualidade para programas escritos em linguagem de alto nível, dado um pequeno conjunto de instruções que são executadas muito eficientemente. Em contrapartida, CISCs — Complex Instruction Set Computers — procuram deixar o conjunto de instruções mais próximo das linguagens de alto nível, facilitando, em tese, a conversão entre linguagens de alto e baixo nível.

RISC, entretanto, não é sinônimo apenas de conjunto de instruções reduzido. Instruções trabalhando unicamente sobre registradores (apenas LOAD/STORE acessam a memória), modos de endereçamento restritos e execução de instruções extremamente pipelined são outras características, igualmente importantes, encontradas no modelo.

A conseqüência da simplificação do hardware é uma série de questões a serem resolvidas pelo software. Operações sobre dados residentes em memória têm um alto custo (relativo) em máquinas LOAD/STORE, o que torna imperativa uma boa alocação de registradores, um problema reconhecidamente complexo no contexto de otimização de código. Similarmente, a execução de instruções em um pipeline pode gerar dependências de dados entre instruções, ou seja, uma instrução pode necessitar de dados que são calculados em instruções anteriores, mas que ainda não estão disponíveis. Existe também a possibilidade de operações triviais, do ponto de vista das linguagens, não estarem disponíveis no repertório, cabendo ao compilador (ou sistema operacional) sintetizá-las.

É exatamente a investigação do conjunto de problemas inerentes à compilação (ou precisamente otimização de código) para máquinas RISC o objetivo desta dissertação. Basicamente dois problemas são tratados em profundidade: alocação de registradores e otimização da execução pipelined. As próximas duas seções os introduzem em mais detalhes.

O primeiro problema que alguém imagina em um compilador que emite código para uma arquitetura com poucas instruções é a dificuldade de transformar a linguagem de alto nível em instruções muito primitivas. Curiosamente este não é o problema maior. A razão é que as linguagens intermediárias usadas pelos compiladores têm instruções também primitivas em pouco número. A emissão de uma instrução complexa resulta da combinação de várias das instruções intermediárias. Pode-se dizer, portanto, que o problema de escolher (selecionar) o código a emitir para uma máquina RISC é um caso particular da emissão de código para CISCs. Diante disto, o assunto não será tratado exaustivamente, embora uma das seções do capítulo 2 trate genericamente dos principais tópicos envolvidos com seleção de código.

#### 1.1 Alocação de Registradores

Alocar registradores consiste em escolher determinadas variáveis do programa, ou temporários gerados pelo compilador, para permanecerem em registradores. O custo do acesso à memória em máquinas de conjunto de instruções reduzido torna este requisito determinante da qualidade do código gerado.

O princípio básico a ser respeitado por um algoritmo de alocação de registradores é que se duas variáveis podem ter seus valores (supõe-se distintos) ainda necessários a partir de um instante qualquer da execução do programa, então devem receber registradores distintos.

Um problema equivalente à alocação de registradores é a coloração de um grafo. Neste, quaisquer dois vértices devem receber cores distintas quando estão ligados por uma aresta. Se existir um modo de prever (e existe) que duas variáveis podem ter seus valores necessários em determinado instante da execução, então um grafo pode ser construído considerando as variáveis como vértices e determinando arestas a partir das "previsões". Deste modo uma cor pode também ser vista como um registrador, tornando os problemas equivalentes.<sup>1</sup>

Existem vários métodos para colorir um grafo associado a alocação de registradores e boa parte deste trabalho trata do assunto.

#### 1.2 Otimização de Pipelines

Considere uma implementação RISC hipotética cujo *pipeline* tem três estágios: Busca (B), Execução (E) e acesso a operando em memória (M). Todas as operações aritméticas e lógicas terminam no segundo estágio, enquanto LOAD e STORE terminam no terceiro. Observe-se, então, os acontecimentos com a seqüência de instruções mostrada na Figura 1.1, quando executadas de forma *pipelined*.

No instante t4 ocorre um problema: o valor do registrador r2 é necessário, entretanto não se encontra disponível. Existe uma dependência de dados ou interlock entre instruções. Possíveis soluções para o problema são: introduzir uma instrução nop entre as instruções i2 e i3 com o

<sup>&</sup>lt;sup>1</sup>A equivalência não resulta unicamente desta construção, mas (também) do comportamento que programas podem ter com relação ao fluxo de controle.

| Rótulo | Instrução      |

|--------|----------------|

| i1     | add r1, r2, r3 |

| i2     | ld [r3], r2    |

| i3     | add r2, r3, r1 |

| i4     | and r4, r5, r6 |

| 11  | <i>t</i> 2 | <i>t</i> 3 | 14  | $t_5$ |

|-----|------------|------------|-----|-------|

| (B) | (E)        |            |     |       |

|     | (B)        | (E)        | (M) |       |

|     |            | <b>(B)</b> | (E) |       |

|     |            |            | (B) | (E)   |

Figura 1.1: Execução de uma sequência de instruções no pipeline.

objetivo de retardar a terceira instrução; um outro esquema mais "inteligente" poderia perceber que a ordem de execução das instruções i3 e i4 é irrelevante no resultado final e, permutando essas instruções, a necessidade de nop deixa de existir. Essa última abordagem é chamada reorganização ou escalonamento de instruções, e as técnicas usadas para mínimizar o número de nops também são abordadas em detalhes nesta dissertação.

#### 1.3 Investigações

A interação entre arquitetura e compiladores freqüentemente dá margem a diferentes interpretações sobre a melhor forma de gerar código eficiente. A fim de comprovar alguns dos princípios que têm guiado o projeto de máquinas RISC, algumas investigações foram feitas usando o suporte do Gnu C Compiler - GCC [Sta89] para a SPARC [Sun87].

Em alguns casos, as experiências garantiram margem significativa de otimização sobre o código gerado pelo compilador, em outros confirmaram experimentos outrora executados em outros contextos e, por último, permitiram conjecturar sobre algumas das tendências de evolução das arquiteturas.

O GCC foi escolhido pela facilidade de acesso ao seu código fonte e por oferecer o suporte necessário à implementação de algumas otimizações. A versão 1.35 foi utilizada porque no momento que as investigações foram iniciadas, era a única ao alcance. Depois de conduzidos alguns experimentos, optou-se por continuar a utilizá-la, mesmo na existência de versões mais atualizadas. No contexto explorado, as versões mais recentes parecem ter pouco impacto sobre os resultados das experiências desenvolvidas, muito embora alguns bugs da versão utilizada tenham limitado os horizontes de experimentação. Uma nova versão (2.0), somente liberada na fase final de elaboração da dissertação, parece incorporar algumas dessas experiências.

#### 1.4 Terminologia

A terminologia usada nesta dissertação geralmente coincide com a encontrada na literatura; termos em inglês são usados sempre que a tradução portuguesa não esteja padronizada. Nesta seção é introduzida a terminologia básica; quando necessário, esta terminologia é complementada no início de cada capítulo.

O termo programa denota um conjunto de procedimentos possivelmente compilados separadamente. Procedimento genericamente qualifica procedimentos, funções ou subrotinas de uma linguagem de programação particular.

Um bloco básico é uma seqüência de instruções sempre executada na totalidade e com, no máximo, uma instrução de desvio no final.

Adota-se genericamente o termo variável para caracterizar qualquer elemento alocável a um registrador, o que inclui variáveis escalares definidas pelo programador e temporários criados pelo compilador na geração de código para avaliação de expressões.

Uma variável ou é global ao programa ou pertence a algum procedimento, neste caso dita local. Os conceitos de local e global são, entretanto, bastante dependentes do contexto onde aplicados. Por exemplo, no capítulo 4, uma variável é considerada local se referenciada dentro de um único bloco básico e global, caso contrário; no capítulo 5 uma variável é tida como global se referenciada dentro de mais de um procedimento e local caso contrário. O contexto que precede o emprego de um ou outro termo é, em geral, suficiente para tornar claro o significado.

O percentual de otimização sobre um programa, normalmente expresso em termos de tempo, representa a fatia do tempo de execução original que foi eliminada em função do emprego de uma otimização. Define-se similarmente otimização sobre o tamanho do código e número de instruções, entre outras.

Em vários pontos do texto são apresentados exemplos de programas e suas respectivas representações intermediárias, ou mesmo o código de montagem final. Via de regra. a linguagem em que os trechos de programa são escritos é C [KR88]. Não serão precisamente definidas nem uma linguagem intermediária, nem uma linguagem de montagem, sendo o contexto suficiente para esclarecer o significado das (pequenas) porções de código; a única ressalva é que instruções sempre têm no último operando o destinatário da computação executada pela instrução.

Na literatura usa-se o termo arquitetura de uma máquina para expressar a visão que o programador (ou compilador) tem da máquina, ou seja, os seus aspectos externos: registradores, instruções, modos de endereçamento. Em alguns casos, esta visão é insuficiente para emissão de código de boa qualidade. No contexto estudado, arquitetura compreende os aspectos da organização da máquina que podem aumentar (ou diminuir) o seu desempenho, dependendo da forma de programação, por exemplo, acesso aos caches e organização de pipclines.

#### 1.5 Os Benchmarks

Várias seções deste trabalho tratam com o comportamento estatístico de programas executados sobre uma arquitetura particular: a SPARC. Uma breve explicação sobre cada um dos programas e sobre suas respectivas origens é dada a seguir:

- 001.gcc-1.35: gcc-1.35 é o Gnu C Compiler versão 1.35 distribuído pela Free Software Foundation. A execução do programa consiste em converter 19 de seus próprios arquivos fontes em código de montagem otimizado para a Sun-3. GCC testa cache, entrada e saída e UCP. GCC é parte do SPEC benchmark suite.

- 008.espresso: espresso é uma ferramenta para geração e otimização de Programmable Logic Arrays (PLAs). O tempo total de execução se refere a quatro modelos de entrada suportados pelo programa. O programa usa muita memória, testando assim o cache de dados. É parte do SPEC benchmark suite.

- 022.li: li é um interpretador Lisp. A execução determina o tempo gasto pelo programa para resolver o problema das nove rainhas. li testa a UCP e o alto número de chamadas de

- procedimento é um desafio para máquinas com registradores organizados em forma de janelas. É parte do SPEC benchmark suite.

- 023.eqntott: equtott transforma uma representação lógica de uma expressão booleana para uma tabela verdade. Exercita o cache de dados e a UCP. Também faz parte do SPEC benchmark suite.

- stanford: stanford é composto por um conjunto de pequenos procedimentos que avaliam a UCP. Inclui torres de hanói, nove rainhas, transformada de Fourrier e quick sort. Foi obtido junto a John Hennessy da Universidade de Stanford;

- navega: navega é um utilitário que faz mudança de projeção em imagens de satélites geoestacionários. Ele usa o posicionamento do satélite para localizar coordenadas geográficas em uma imagem matricial e, vice-versa. O programa faz uso de muitas operações de ponto flutuante. A sua execução consiste em encontrar a localização matricial de 10.000 coordenadas terrestres e, a seguir, fazer a operação contrária. Este programa é oriundo da Fundação Cearense de Meteorología e Recursos Hídricos FUNCEME;

- reorg: reorg é um reorganizador de código de montagem para a arquitetura SPARC. Ele faz alguma entrada e saída, mas o seu tempo de execução é limitado pela UCP. Foi desenvolvido durante a elaboração deste trabalho. Seu tempo de execução corresponde a dez reorganizações do código de montagem referente a ele mesmo.

Todos os programas são escritos em linguagem C e as estatísticas foram obtidas utilizando o compilador GCC, versão 1.35.

Onde tempos de execução são considerados, eles se referem à melhor de quatro execuções em uma SPARC1+ com apenas uma shell executando. A unidade de tempo é o segundo e compresende o tempo gasto no código do processo e no código do sistema operacional referente às chamadas de sistema feitas pelo processo. O utilitário time do sistema UNIX foi usado nas medidas.

#### 1.6 Organização da Dissertação

A primeira parte desta dissertação discute arquiteturas RISC. O capítulo 2 oferece uma visão do modelo, partindo das motivações que culminaram com a ruptura do modelo CISC e explorando as ramificações que surgiram das propostas iniciais do padrão RISC. Este capítulo também oferece os conceitos básicos que são usados nas demais partes do trabalho. Capítulo 3 é um estudo de caso de uma arquitetura RISC, a SPARC. Além de apresentar a visão prática do modelo RISC, vários aspectos de interação entre hardware e software são apresentados, alguns deles explorados no capítulo 7.

A segunda parte trata de alocação de registradores. Várias técnicas, a maioría não aplicável exclusivamente a arquiteturas RISC, são estudadas. O capítulo 4 trata daquelas que alocam os registradores tendo a visão de apenas um procedimento por vez, as mais comumente usadas na prática. O capítulo seguinte mostra alguns contextos onde a alocação de registradores a um programa inteiro é importante e como ela pode ser feita. Algumas estratégias de alocação de registradores executadas pelo hardware são apresentadas também no mesmo capítulo.

A terceira parte discute reorganização de instruções. Inicialmente no contexto de otimização de pipelines, depois no sentido de encontrar paralelismo de granularidade fina, a fim de "alimentar"

máquinas RISC com mais de uma unidade funcional que operam paralelamente entre si. O capítulo 6 é dedicado a estes problemas e suas respectivas soluções.

A quarta e última parte relata experiências com o estudo e a implementação de algumas técnicas, discutidas nos capítulos precedentes, em um compilador de produção para a SPARC. De certa forma as informações oriundas das implementações estão distribuídas em vários capítulos, mas é no capítulo 7 que os resultados são apresentados em detalhes. O capítulo 8 conclui a dissertação com uma discussão dos trabalhos futuros.

### Capítulo 2

## Arquiteturas RISC

"...e aquilo que neste momento se revelará aos povos, surpreenderá a todos não por ser exótico, mas pelo fato de poder ter estado oculto, quando terá sido o óbvio."

Caetano Veloso - Um indio

#### 2.1 Introdução

A qualidade de uma arquitetura pode ser medida pela sua adequação ao suporte das aplicações e pelo desempenho do hardware usado na sua implementação. Um computador de uso geral é normalmente programado em linguagem de alto nível. Esta, por sua vez, traduzida até o conjunto de instruções por um compilador e, o código objeto, executado usando a base de um sistema operacional. Portanto, o suporte às aplicações baseia-se primordialmente no trabalho conjunto entre arquitetura, compilador e sistema operacional. Por outro lado, a efetividade da implementação da arquitetura é resultado da velocidade do hardware em função do custo para obtê-la.

Diante destas métricas é importante escolher bem o conjunto de instruções a ser oferecido pela arquitetura, visto que ele permeia o trabalho de cada uma das fases entre a codificação da aplicação em uma linguagem de alto nível e a obtenção dos resultados desejados.

Arquiteturas RISC são o resultado de criteriosas análises sobre como o conjunto de instruções é usado no decorrer desse processo, considerando a freqüência de uso de instruções em programas compilados, bem como o custo de implementação de cada uma delas. A observação desses conceitos conduziu a arquiteturas "enxutas" não só em número de instruções, mas também em formatos e modos de endereçamento, viabilizando um maior desempenho de aplicações através do acoplamento entre compiladores e arquitetura.

O conteúdo deste capítulo é o seguinte: a seção 2.2 revê alguns aspectos históricos sobre projetos de máquinas nas duas últimas décadas; as suas influências para o surgimento de RISC estão na seção seguinte. As características do novo modelo são apresentadas na seção 2.4. O trabalho conjunto entre compiladores e arquiteturas é discutido na seção 2.5. O debate RISC versus CISC está na seção 2.6. A seção 2.7 é sobre processamento de ponto flutuante em RISCs e a 2.8 sobre a próxima geração de máquinas RISC.

#### 2.2 Evolução das Arquiteturas

As limitações tecnológicas fizeram os primeiros computadores muito simples. Por volta de 1965, com o lançamento do IBM/360, a IBM inaugurou uma nova era no projeto de computadores ao oferecer várias implementações da mesma arquitetura. A partir de um hardware básico, microcódigo foi maciçamente empregado para oferecer um conjunto de instruções bastante sofisticado. Com um poder de expressividade mais alto que o hardware [Pat85], o microcódigo acabara com os limites à potência dos conjuntos de instruções.

Não coincidentemente, nesse mesmo período, as linguagens de programação de alto nível já se firmavam. Reconhecidamente era impossível impedir a evolução das linguagens, uma vez que elas se mostravam como um horizonte à emergente crise do software. Os projetístas de computadores, reconheceram então, um gap semântico entre linguagens de alto e baixo nível [Tan90], tornando compiladores muito complexos e passíveis a erros.

A verdade é que o microcódigo tomou uma importância muito grande nos projetos de computadores, desde o seu surgimento (até hoje). O VAX 11/780, por exemplo, tem nada menos que 303 instruções, microcodificadas, com tamanho variando de 2 a 57 bytes [Pat85]. A tendência generalizada em torno de microcódigo e a criação de ferramentas para desenvolvê-lo levou projetistas de computadores ([CIEDJK85]) a:

- tornar novas arquiteturas compatíveis com modelos anteriores. Este compromisso gera uma forte pressão para aumentar conjuntos de instruções, formatos e modos de endereçamento;

- tentar reduzir o gap semântico através do suporte, em hardware, a construções presentes nas linguagens de alto nível. O efeito de implementar instruções complexas e a capacidade que os compiladores tinham de gerá-las foram freqüentemente ignorados;

- transferir funções de software para microcódigo. Sendo este (na época) dez vezes mais rápido que as memórias convencionais, se uma única instrução pudesse descrever várias operações executadas em hardware, então o acesso à memória e o tempo de execução seriam drasticamente reduzidos.

Em meados dos anos setenta existia um conjunto de princípios a ser seguido por qualquer nova arquitetura. Esses incluíam o uso de microcódigo em larga escala e a minimização do tamanho dos programas, não sendo raras as máquinas projetadas para suportar uma linguagem ou modelo que execução específico. Tanenbaum [Tan90] cita um pesquisador da época: "As máquinas do futuro terão instruções com até seis campos e nenhum registrador, reduzindo largamente o gap semântico".

#### 2.3 As Origens de RISC

Motivados pelo baixo aumento de desempenho proporcionado pelos avanços na tecnologia de hardware, pesquisadores começaram a fazer medidas para determinar como estavam sendo utilizadas as arquiteturas e linguagens de programação.

Do ponto de vista de linguagens uma grande variedade de programas foi analisada. Uma parte dos resultados ([Tan90]) é mostrada na Tabela 2.1. XPL e SAL são linguagens com estilo PL/I e Pascal, respectivamente. A média é aritmética e tem sentido apenas qualitativo, desde que diferentes conjuntos de programas foram analisados em cada caso. [Tan78] também examinou

| Construção  | SAL | XPL | FORTRAN | C  | Pascal | Média |

|-------------|-----|-----|---------|----|--------|-------|

| Atribuição  | 47  | 55  | 51      | 38 | 45     | 47    |

| Condicional | 17  | 17  | 10      | 43 | 29     | 23    |

| Chamada     | 25  | 17  | 5       | 12 | 15     | 15    |

| Repetição   | 6   | 5   | 9       | 3  | 5      | 6     |

| Desvio      | 0   | 1   | 9       | 3  | 0      | 3     |

| Outros      | 5   | 5   | 16      | 1  | 6      | 7     |

Tabela 2.1: Frequência percentual de construções em linguagens de alto nível.

outras três características do código fonte de um sistema operacional escrito em SAL. Os resultados estão na tabela 2.2.

|                 | 0  | 1  | 2  | 3  | 4 | ≥ 5 |

|-----------------|----|----|----|----|---|-----|

| (a) Termos      | -  | 80 | 15 | 3  | 2 | 0   |

| (b) Parâmetros  | 41 | 19 | 15 | 9  | 7 | 8   |

| (c) Var. Locais | 22 | 17 | 20 | 14 | 8 | 20  |

Tabela 2.2: Frequência percentual de: (a) Termos por atribuição; (b) Parâmetros passados por chamada de procedimento; (c) Variáveis locais por procedimento.

Do ponto de vista do conjunto de instruções, as medidas são igualmente expressivas. No IBM 370, dez instruções (as mais simples) são responsáveis por 67% das execuções [Muc90a]. No VAX, os quatro modos de endereçamento básicos são empregados em 92% dos casos [Wie82]. Números similares também foram posteriormente encontrados para outras arquiteturas, incluindo o IBM-PC [AZ89].

As conclusões desses estudos foram:

- Os programas podem ser muito complexos, mas normalmente possuem uma estrutura muito simples;

- Os compiladores não conseguem fazer o uso apropriado das instruções possantes oferecidas pela arquitetura. Na prática, dadas uma linguagem e uma arquitetura existem mais diferenças que semelhanças entre elas.

Os resultados das medidas sobre o comportamento dos programas, a freqüência de uso de instruções, o surgimento das memórias cache e o conhecimento do princípio de localidade de referências dentro dos programas determinaram mudanças nos padrões já estabelecidos. Argumentou-se que a tentativa de eliminar o gap semântico só serviu para introduzir um gap de desempenho. Tornou-se evidente que para fazer uma arquitetura de uso geral o mais eficiente possível era necessário:

- Priorizar a implementação eficiente das instruções mais executadas;

- Minimizar o tempo de ciclo de relógio do sistema. O que demanda reduzir e balancear os tempos das seguintes atividades:

- Decodificação de instruções;

- Acesso aos registradores;

- Acesso ao cache:

- Operação da Unidade de Aritmética e Lógica.

- Minimizar o número de ciclos para executar cada instrução; ou menos rigorosamente, o número de ciclos para que os resultados de uma instrução estejam disponíveis à seguinte.

Projetistas de arquiteturas RISC tornaram mais forte a última regra ao exigirem que "todas" as instruções executem em apenas um ciclo.

A principal vantagem de arquiteturas RISC sobre arquiteturas CISC convencionais é a eliminação do efeito da implementação de instruções complexas sobre instruções simples e primitivas. Em uma máquina com grande conjunto de instruções é muito mais difícil traduzir as regras acima em resultados práticos, a custo baixo. A razão disso é o grande número de variáveis envolvidas, por exemplo, múltiplos tipos de dados, necessidade de acessos simultâneos à memória, várias combinações de formatos e muitos modos de endereçamento.

#### 2.4 Princípios de Projeto em RISC

RISC baseia-se em extrair eficiência e funcionalidade da simplicidade. A evolução dos compiladores e a simplificação da arquitetura fizeram com que os resultados surgissem rapidamente. A rigor, o número de instruções é mais consequência do que causa. A razão principal da simplicidade do conjunto é a busca da eficiência. Entre as características do modelo estão:

- Instruções de um ciclo de relógio;

- Poucas instruções e modos de endereçamento;

- Arquitetura LOAD/STORE;

- Grande conjunto de registradores;

- Pipelining em alta escala;

- Eliminação do microcódigo;

- Formato fixo de instruções;

- Interdependência entre arquitetura e compiladores.

Note-se, entretanto, que estas características não são totalmente independentes.

#### 2.4.1 Instruções de um ciclo de relógio

O que realmente distingue uma máquina RISC de uma máquina CISC não é o número de instruções, mas a natureza das instruções presentes no repertório. Embora sendo verdade que o número de instruções RISC seja pequeno, o mais importante é que quase a totalidade delas executa em um ciclo.

Para minimizar o tempo de ciclo de relógio, Patterson [Pat85] sugere que nunca se deve colocar uma nova instrução no repertório básico se não há uma forte razão para fazê-lo. Aqui, uma forte razão é função da possível freqüência de uso e do custo de implementação da instrução em questão. Portanto vale a regra: se uma instrução aumenta o tempo de ciclo em 10%, sua inclusão deve proporcionar, no mínimo, uma redução equivalente no número de instruções executadas.

#### 2.4.2 Poucas instruções e modos de endereçamento

A ênfase em instruções de tempo de execução similar e implementação eficiente levou a majoria das implementações RISC a terem menos de 100 instruções e dois ou três modos de endereçamento.

Na prática, o pequeno e peculiar conjunto não é uma restrição muito forte, desde que as instruções presentes são as mais comumente executadas. Um exemplo é a ausência de instruções de multiplicação e divisão na maioria dos RISC. Embora primitivas, estas operações são muito caras quando comparadas às demais. Nestas situações é importante o poder de síntese dos compiladores. [Muc90b] relata que, em geral, essas operações têm, no mínimo, um operando constante, podendo ser implementadas eficientemente através de shifts, adições e subtrações [Muc90b]. Para a multiplicação, isto resulta um tempo médio de execução em "software" de apenas seis ciclos, comparados aos quase sessenta para o caso geral.<sup>1</sup>

Seguindo uma cadeia de vantagens, o reduzido número de instruções simplifica o projeto de uma unidade de execução pipelined [HB84] e diminui o custo do estágio de decodificação, além de liberar mais área na pastilha para implementação de um número maior de registradores ou caches internos.

#### 2.4.3 Arquitetura LOAD/STORE

Minimizar o tempo de ciclo e executar em um único ciclo instruções que fazem acesso à memória são objetivos incompatíveis. A razão é relativamente óbvia: para cada operando em memória, um ciclo é gasto no cálculo do endereço e pelo menos um outro no acesso à memória (ou cache). A solução normalmente adotada é permitir que apenas as instruções LOAD e STORE tenham operandos em memória, as demais operam unicamente sobre registradores ou operandos constantes imediatos. Esta restrição simplifica o problema, que pode agora ser resolvido com pequenas penalidades na implementação do pipeline, conforme detalhado nas próximas subseções.

¹ Novas versões das arquiteturas MIPS [Cho88] e SPARC [Sun87] oferecerão instruções de multiplicação e divisão em hardware. A ideia é ter uma espécie de execução em background da instrução e bloquear o acesso ao registrador alvo até que o resultado tenha sido, de fato, gerado. Um registrador especial, scoreboarding, contem um bit para cada registrador da arquitetura, indicando se o acesso a determinado registrador bloqueia ou não o processador.

<sup>&</sup>lt;sup>2</sup>Salvo menção em contrário, memória RAM e cache serão usadas de forma intercambiável.

#### 2.4.4 Grande conjunto de registradores

Se programas executando em um modelo LOAD/STORE (registrador-registrador) são submetidos a um alocador de registradores, o tráfego de (para) a memória pode ser grandemente reduzido, desde que o bom uso de registradores permite a reusabilidade de operandos. No entanto, o número de registradores na arquitetura deve ser suficiente para permitir uma boa alocação. O número típico de registradores encontrado é 32 (vide apêndice A).

Um dos primeiros RISCs, RISC I [PS82], do qual a SPARC é descendente, adotou uma solução elegante para evitar salvar e restaurar o contexto dos registradores durante chamadas de procedimento. O arquivo de registradores é dividido em conjuntos de tamanho fixo, com apenas um deles ativo em qualquer instante, representando os registradores conhecidos no momento. Quando uma chamada de procedimento ocorre, um novo conjunto (janela) é ativado e a janela anterior mantida intacta. No retorno, a janela original passa a ser a ativa. Na SPARC os deslizamentos são feitos usando instruções específicas, normalmente executadas no início c fim de cada procedimento. Detalhes no próximo capítulo.

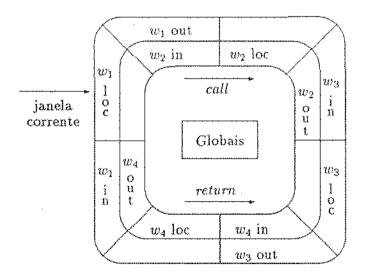

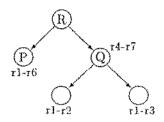

Para permitir passagem de parâmetros em registradores, os conjuntos são organizados em uma fila circular e vizinhos têm alguns registradores em comum onde o chamador pode armazenar valores para uso do chamado. Alguns registradores globais são normalmente disponíveis. A Figura 2.1 ilustra um conjunto dividido em quatro janelas;  $w_i$  loc refere-se aos registradores disponíveis para variáveis locais na i-ésima janela. Similarmente os registradores em  $w_i$  in e  $w_i$  out são destinados à alocação de parâmetros formais e efetivos, respectivamente.

Eventualmente, após um conjunto de chamadas, nenhuma janela está livre. Se uma nova chamada acontece, então os registradores da janela menos recentemente utilizada são armazenados na memória, tornando-a disponível para uso pelo procedimento chamado. A restauração dos registradores pertencentes a uma janela é feita sob demanda [TS83].

Figura 2.1: Janelas de Registradores.

#### 2.4.5 Pipelining em alta escala

Execução em um ciclo não implica necessariamente que cada instrução permanece na UCP por apenas um ciclo. Rigorosamente, a execução total de qualquer instrução toma mais de um ciclo. Como já discutido, o acesso à memória gasta um ciclo e toda instrução antes de ser submetida para execução deve ser buscada na memória. Em geral, o processamento de uma instrução, numa máquina RISC, é composto de quatro estágios: busca, decodificação, execução e armazenamento de resultados. Execução em um ciclo refere-se ao tempo gasto no terceiro estágio do processamento da instrução.

Desde os primeiros projetos de computadores, pipeline tem sido uma das principais técnicas para melhorar o desempenho. A profundidade (número de estágios) do pipeline dá o aumento potencial da taxa de processamento. Mas um pipeline só é efetivo se ele pode ser mantido cheio e livre de inconsistências a maior parte do tempo. Neste sentido a profundidade atua apenas como um multiplicador ideal, não real, para o aumento do desempenho que pode conceitualmente ser obtido com a sobreposição temporal do processamento das instruções.

Vários fatores contribuem para limitar o desempenho de um pipeline, entre eles dependência de dados, instruções que alteram o fluxo seqüencial do programa e, também, o próprio custo de gerenciamento do pipeline em cada estágio [Hen84]. Dependência de dados é o termo para caracterizar a situação onde o processamento simultâneo de instruções no pipeline gera inconsistências em relação à execução de uma instrução por vez. Instruções que alteram o fluxo de controle criam a necessidade de recarregar estágios do pipeline que pressupõem execução estritamente seqüencial. O gerenciamento de buffers entre estágios e a prevenção e tratamento de dependências e desvios aumentam o tempo básico de cada estágio e por conseguinte diminuem o desempenho ideal do pipeline.

Nos exemplos a seguir, considere o pipeline simples, ainda assim realista, de três estágios:

Busca (B): uma nova instrução é buscada da memória;

Execução (E): a instrução buscada no ciclo anterior é decodificada e executada (no caso de LOAD/STORE o endereço é calculado);

Memória (M): se algum acesso à memória de dados é necessário, ele acontece neste estágio.

Apenas as instruções LOAD e STORE usam o terceiro estágio, as demais terminam um cíclo após serem buscadas.

#### Dependência de dados

Podem acontecer três tipos de dependências de dados no processo de execução pipelined. O primeiro e mais comum ocorre quando uma instrução requer um resultado calculado por uma outra instrução anterior, mas o resultado ainda não está disponível. Esta dependência é denominada leitura-após-escrita (RAW), ou dependência de fluxo.

O segundo, chamado escrita-após-leitura (WAR), ou anti-dependência, acontece quando um operando é atualizado antes que todas as instruções que necessitam de seu valor anterior o tenham lido.

Finalmente, uma depedência escrita-após-escrita (WAW) ou de saída pode resultar de uma alteração na ordem de atualização de operandos.

Observe que apenas o primeiro caso de dependência é verdadeiro, os dois últimos são, em princípio, consequência de reutilização de recursos. Obviamente, não existem dependências em função de múltiplas leituras. Para resolver dependências de RAW existem várias estratégias. Aborda-se, abaixo, duas por software e duas por hardware; uma combinação adequada delas sempre resolve o problema:

- 1. Curto-Circuito Os resultados intermediários de qualquer computação em andamento são encaminhados aos demais estágios, se as instruções subseqüentes necessitam deles;

- 2. Interlock Se o hardware deteta dependência de dados, alguns estágios do pipelíne são congelados até que a dependência deixe de existir:

- 3. No-op É o interlock por software; consiste em colocar instruções nulas (nop) entre instruções sempre que dependências RAW possam acontecer. Este esquema pode aumentar o tamanho estático do programa objeto e a complexidade do compilador, mas reduz a complexidade do hardware, aumentando a eficiência;

- 4. Escalonamento de instruções É uma generalização da abordagem anterior, nesse caso o compilador se encarrega de reconhecer dependências estaticamente e mudar a ordem das instruções para eliminá-las.<sup>3</sup> A reorganização, entretanto, deve manter a ordem relativa entre algumas instruções de modo a deixar o resultado final das computações inalterado. Para executar essa tarefa o compilador deve conhecer o pipelíne da máquina alvo. No capítulo 6 o assunto é discutido em detalhes.

Note-se que a ausência de *interlocks* em *hardware* obriga o uso de uma estratégia em *software*. A arquitetura SPARC, por exemplo, implementa parcialmente ambas as estratégias de *hardware* (1 e 2), ficando a cargo do compilador resolver algumas exceções e aumentar a eficiência do código (vide capítulo 3) através de escalonamento. A arquitetura MIPS não possui *interlock* e por isso, em conjunto com os compiladores, usa uma estratégia que abrange 1, 3 e 4.

Existe um conjunto de técnicas para projetar pipelines com número reduzido de dependências, mas o desempenho da arquitetura pode ser muito afetado [Nav90]. Em RISCs é possível simplificar o processo: para o caso de dependências WAR, uma solução simples é forçar que todos os dados necessários à execução de uma instrução sejam obtidos em uma fase de pipelining anterior a qualquer daquelas que atualizam dados. Para dependência WAW é suficiente exigir que todas as operações terminem em um único estágio. Curto-circuito é em geral muito efetivo no tratamento de dependências RAW quando o pipeline tem poucos estágios.

#### Instruções de acesso à memória

Se existem caches separados para dados e instruções e é possível fazer acessos simultâneos aos dois, então como resultado de iniciar uma instrução LOAD (STORE) no ciclo c, tem-se no ciclo c+2 a busca (armazenamento) do operando. Neste intervalo, uma nova instrução está sendo executada e outra buscada para execução. No ciclo c+2 duas instruções terminam. Portanto, muda-se parcialmente os objetivos, em vez de executar uma instrução a cada ciclo, inicia-se uma nova instrução a cada novo ciclo. Numa visão "macro" os resultados são equivalentes. Essa estrutura

<sup>&</sup>lt;sup>3</sup>Pelo menos uma arquitetura, o CDC 6600, adotou esta estratégia em hardware.

de pipeline foi usada em uma máquina experimental da Hewllet-Packard [GM86]. Observe que o esquema cria algumas dependências de dados.

Por outro lado, se o cache não permite acesso concorrente a dados e instruções, então o pipeline é congelado por um ciclo para que o acesso à memória seja efetuado. Feito o acesso o fluxo continua normalmente. Grosseiramente este é o caso da arquitetura SPARC.

Estas duas abordagens dão origem a duas definições importantes que serão utilizadas nos capítulos 3, 6 e 7: custo de execução e latência de instruções. Define-se latência como o número de ciclos necessários para que os resultados de uma instrução estejam disponíveis à seguinte. O custo da instrução corresponde ao número de ciclos que a instrução ocupa com exclusividade o(s) estágio(s) de execução do pipeline, ou impede outras instruções de utilizá-lo(s).

Por exemplo, na primeira situação considerada para resolver o problema de LOADs (e STO-REs), o fluxo de execução no pipeline continua inalterado, com uma instrução sendo executada em cada ciclo, assim o custo do LOAD é um ciclo, mas sua latência é também um ciclo, dado que seu resultado não pode ser utilizado imediatamente por uma instrução subseqüente. A segunda estratégia por outro lado, retarda o início da execução da instrução seguindo o LOAD em um ciclo, aumentando, por conseguinte, o seu custo também em um ciclo; não existe, porém, latência neste caso.

Como já notado, máquinas RISC têm, para a maioria da instruções, custo de execução de um ciclo e latência nula. Instruções LOAD e STORE aumentam uma das duas grandezas em função do acesso ao cache. Como será apresentado posteriormente, instruções de ponto flutuante são outra fonte de latências e custos acima de um ciclo.

#### Instruções de desvio

A outra fonte de problemas com *pipeline* diz respeito a instruções que alteram o contador de programa, doravante chamadas instruções de desvio.

Considere o trecho de programa na Figura 2.2 sendo executado no pipeline anteriormente apresentado. A fase de busca de instruções (B) baseia-se na ausência de desvios, por isto no momento que a instrução i28 está no estágio de execução (E) a instrução i32 já está sendo buscada. Após a fase de execução de i28, o contador de programa vale i40, mas i32 já foi buscada. Neste momento, o trivial seria anular a instrução i32; não é o que a maioria das arquiteturas RISC faz.

| Rótulo | instrução |

|--------|-----------|

| i24    | add       |

| i28    | jmp i40   |

| i32    | or        |

| 136    | and       |

| 140    | XOI       |

| $t_i$ | $t_{i+1}$ | $t_{i+2}$ | ti+3 |

|-------|-----------|-----------|------|

| (B)   | (E)       |           |      |

|       | (B)       | (E)       |      |

|       |           | (B)       | (E)  |

|       |           |           |      |

| -     |           | 1         | (B)  |

Figura 2.2: Efeito da instrução de desvio na execução pipelined.

Sendo a freqüência de instruções de desvio alta, descartar a instrução seguindo o desvio pode reduzir consideravelmente o desempenho, a menos que alguma técnica de previsão de desvios seja considerada. Enquanto a previsão do alvo de um desvio pode, na grande maioria dos casos, ser feita com sucesso [LS84], ela não é suficiente quando atrasos no pipeline são indesejados. É necessário

algum mecanismo de îniciar a busca das instruções, que de acordo com a previsão sucedem o desvio, antes da execução (precisamente decodificação) deste. Ou seja, alguma espécie de look-ahcad para verificar a presença de desvios deve ser executado; instruções de tamanho variável contribuem para complicar ainda mais a lógica de busca.

Um esquema alternativo e largamente difundido em máquinas LOAD/STORE é desvio com efeito retardado (ou delayed-branch). Neste caso um certo número de instruções (slots) seguindo o desvio será sempre executado. Cabe ao compilador encontrar instruções independentes da de desvio e deslocá-las para depóis desta. Um simples otimizador peephole pode tratar eficientemente desvios incondicionais. O tratamento de desvios condicionais é um caso de escalonamento de instruções. Uma estratégia alternativa é implementada pela SPARC: a execução da instrução que segue o desvio pode ou não ser executada, baseada na resolução do desvio. Se a instrução não é executada, o ciclo é desperdiçado.

A alta frequência de desvios é o maior obstáculo ao desempenho ideal do pipeline. Estatísticas [Rad82, Cho88] mostram que o número de desvios varia de acordo com o conjunto de instruções. No VAX 11/780, uma de cada quatro instruções executadas é um desvio tomado [Wie82]. Em arquiteturas LOAD/STORE o número de instruções de desvio (tomados ou não) é da ordem de 20%.

Usando um reorganizador para a arquitetura SPARC desenvolvido no decorrer deste trabalho (e apresentado no capítulo 7) coletou-se medidas estáticas para alguns programas com o fim de verificar o comportamento de desvios atrasados em uma arquitetuta particular. Os resultados estão na Tabela 2.3. Trabalhando com outros programas e um outro RISC, Hennessy [Hen84] também observou ser possível encontrar uma instrução adequada para preencher um slot em 80% dos casos, em média. Conclui-se que com a estratégia de delayed-branch adotada em RISCs, o efeito de desvios é comparável às melhores estratégias de prognosticar o fluxo de controle [LS84], a um custo de implementação muito baixo.

| PROGRAMA     | % de desvios | % de slots preenchidos |

|--------------|--------------|------------------------|

| 001.gcc-1.35 | 23,7 %       | 85,0 %                 |

| 008.espresso | 21,4 %       | 88,9 %                 |

| 022.li       | 27,0 %       | 88,0 %                 |

| 023.eqntott  | 23,2 %       | 85,7 %                 |

| navega       | 7,6 %        | 93,8 %                 |

| reorg        | 18,7 %       | 71,0 %                 |

| stanford     | 14,6 %       | 81,1 %                 |

Tabela 2.3: Freqüência e reorganização (sobre código otimizado) de desvios na SPARC.

Virtualmente, tornar o pipeline muito profundo pode gerar um melhor desempenho, e portanto mascarar o efeito das instruções complexas sobre as simples. Na realidade o tempo de cada estágio do pipe é determinado pelo tempo gasto no maior estágio. Assim a lógica de decodificação para grandes conjuntos de instruções pode determinar o tempo dos demais estágios. Aumentar o número de estágios faz também aumentar o número de potenciais dependências de dados. Em CISCs este problema é até mais sério porque a maior expressividade das instruções torna a cadeia definição-uso [TS85] mais curta e densa.

Sumarizando: o relacionamento entre alteração do fluxo de controle e granularidade das ins-

truções mostra que pipelines profundos não necessariamente aumentam o desempenho de arquiteturas CISC. Isto é porque o número de operações (não instruções) por bloco básico é dependente da

linguagem e da natureza da aplicação, mas independente do conjunto de instruções. O maior poder

de expressão das instruções CISC leva o compilador (em alguns casos) a gerar menos instruções

para mapear as operações. A situação é agravada porque, em geral, os otimizadores eliminam

muitas das operações dentro dos blocos básicos, mas não reduzem proporcionalmente o número de

desvios. A Tabela 2.4 mostra o número de instruções de desvios antes e após aplicar otimização

(os números são relativos a medidas estáticas). Logo, um pipeline profundo pode ser pouco efetivo,

mesmo porque quanto menor número de instruções entre desvios menores são os possíveis ganhos

com reorganização de instruções.

| PROGRAMA     | SEM OTIMIZAÇÃO |         |      | COM OTIMIZAÇÃO |         |       |

|--------------|----------------|---------|------|----------------|---------|-------|

|              | Desvios        | Total   | %    | Desvios        | Total   | %     |

| 001.gcc-1.35 | 35.685         | 179.916 | 19,8 | 29.361         | 123.848 | 23,7  |

| 008.espresso | 7.759          | 43.969  | 17,6 | 6.682          | 31.255  | 21,4  |

| 022.li       | 2,911          | 22.882  | 12,7 | 2.723          | 10.079  | 27,0  |

| 023.eqntott  | 1.296          | 6.421   | 20,2 | 1.051          | 4.532   | 23, 2 |

| navega       | 197            | 2.893   | 6,8  | 162            | 2.122   | 7,6   |

| reorg        | 1.001          | 7.499   | 13,3 | 864            | 4.618   | 18,7  |

| stanford     | 422            | 3.588   | 11,8 | 328            | 2.253   | 14,6  |

Tabela 2.4: Efeito de otimização sobre o número de desvios.

#### 2.4.6 Eliminação do microcódigo

Além da tentantiva de diminuir o gap semântico, as métricas de arquitetura anteriores a RISC também objetivavam facilitar a programação de aplicações usando linguagem de máquina. Um conjunto de instruções de muito baixo nível poderia se tornar um grande obstáculo à programação de grandes sistemas, usando linguagem de montagem. Por outro lado, microcódigo é conveniente para implementar grandes conjuntos de instruções usando poucas primítivas, com as vantagens que uma abordagem hierárquica de múltiplos níveis propicia.

Do ponto de vista de desempenho, entretanto, estas idéias correspondem a deslocar tarefas de software para o hardware, sem necessariamente implicar em aumento da taxa de processamento. Para evitar o custo de interpretação de microcódigo, RISCs o eliminaram totalmente, ou seja, qualquer instrução é convertida diretamente em sinais de hardware. É possível seguir a mesma filosofia para máquinas com grandes conjuntos de instruções, mas os requerimentos em termos de área no chip e de tempo de projeto são muito maiores e os resultados, apenas, se equiparariam àqueles dos RISCs.

#### 2.4.7 Formato fixo de instruções

Tecnologias VLSI permitem que um grande número de portas lógicas seja colocadas em uma pastilha de silício, mas a velocidade de propagação de sinais é baixa, favorecendo atividades paralelas. No caso de RISC, a simplicidade da arquitetura conduz à simplicidade da implementação. A pouca

variedade de formatos permite decodificação paralela a baixo custo e reduz a probabilidade deste estágio ser o gargalo do pipeline.

Instruções de tamanho fixo (32 bits) e poucos formatos, enquanto favorecem projetistas de compiladores [Wul81], eliminam decodificações seriais encontradas em CISCs e fazem que o suporte a memória virtual seja bastante simplificado. Durante a busca de uma instrução, apenas um cache miss ou page fault pode ocorrer. Somente no caso de LOAD/STORE o mesmo pode acontecer durante a execução.

#### 2.5 Interação Compiladores/Arquitetura

Há divergências sobre a dificuldade de construir compiladores para máquinas com conjunto de instruções reduzido. [Tan90] considera o compilador RISC mais complexo, enquanto [Cha82a] relata que teve seu trabalho simplificado quando construiu um compilador para uma arquitetura padrão RISC. A postura adotada aqui é que compilar para RISC tem seus próprios desafios e facilidades.

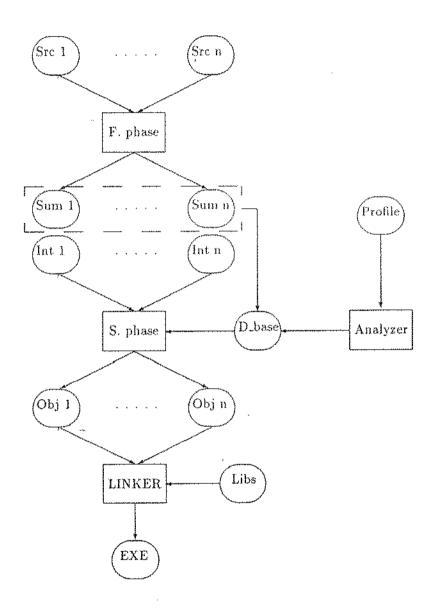

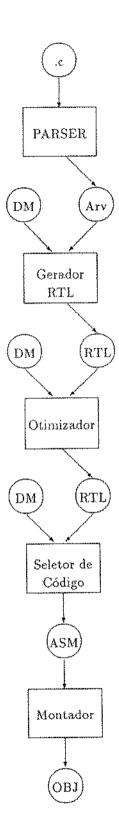

Algumas questões importantes surgem quando um compilador está gerando código para uma arquitetura RISC. Um compilador otimizador é normalmente dividido em duas partes: o front-end e o back-end. O primeiro converte o código fonte em uma linguagem intermediária de muito baixo nível que é processada (otimizada) pelo segundo; ao final, o código intermediário é mapeado para instruções de máquina (seleção de código).

O processo de seleção de código pode ser complicado. Se cada instrução da máquina alvo expressa mais de uma operação da linguagem intermediária (a determinado custo), o problema consiste em cobrir o grafo representando o programa, utilizando subgrafos que representam instruções. Em geral, existem várias seqüências de instruções que geram resultados corretos para o programa. A minimização do custo das instruções emitidas passa a ser função do tempo gasto pelo seletor de código. A interação entre o seletor e o otimizador é igualmente complexa porque uma otimização na linguagem intermediária pode provocar a emissão de instruções de maior custo, mesmo se o número de operações no formato intermediário é reduzido.

Em arquiteturas RISC, a interação entre otimizador e seletor é simplificada porque as instruções de máquina são mais próximas da linguagem intermediária, determinando poucas interseções entre operações executadas por instruções diferentes. Otimizações ambíciosas tendem a ser mais efetivas em máquinas RISC, pois toda transformação aplicada no código intermediário tem efeitos positivos no código objeto final.<sup>4</sup>

A natureza do conjunto de instruções também pode influenciar a qualidade do código gerado e a complexidade do seletor. Irregularidades na semântica das instruções, exigências de registradores específicos em certas instruções e endereçamento relativo a registradores fixos, só como exemplos, exigem análises adicionais para serem detetadas e implicam na emissão de código extra para atender as restrições (ou supostas facilidades). Sobre estes aspectos Wirth [Wir87] escreveu: "A complexidade do compilador não diz respeito ao número de instruções, mas à regularidade do conjunto," sugerindo inclusive que RISC signifique REGULAR Instruction Set Computers. Semelhantes opiniões podem ser encontradas em [Wul81, Den78].

Em segundo lugar está a exposição de detalhes de implementação, como estrutura de pipelines ao compilador. Isto caracteriza a sintonia entre hardware e software e tende a deixar este mais

<sup>\*</sup>Isto não impede que algumas otimizações interfiram entre si.

complicado, contudo garante a maximização da eficiência de aplicações sobre a arquitetura. Para controlar a complexidade do otimizador, bem como aumentar a qualidade do código emitido, é necessário que o conjunto de instruções seja pequeno, mas que toda a informação envolvida na execução de instruções seja conhecida em tempo de compilação [Hen84].

A natureza LOAD/STORE destas arquiteturas exige boas técnicas de alocação de registradores a fim de diminuir o tráfego memória/processador na busca de operandos. Indiretamente estas técnicas têm o efeito de diminuir, também, o número de instruções buscadas e executadas.

Finalmente é importante ressaltar que o pequeno número de instruções pode exigir trabalho do compilador para sintetizar operações, aínda que primitivas. Esta abordagem pode também trazer vantagens considerando-se que, em alguns casos, os dados sob operação são parcialmente conhecidos em tempo de compilação (ver exemplos em [Rad82]). Observe, portanto, que é melhor ter instruções de mais baixo nível que de mais alto. Os compiladores da HP [CHK86], por exemplo, emitem código como se todas as operações do formato intermediário existissem como instruções. Um passo seguinte as converte para o código apropriado, otimizando o que for possível. Esta idéia, denominada millicode, mostrou-se muito eficiente na geração de código para a aritmética do COBOL, usando umas poucas instruções básicas da arquitetura.

Vários experimentos nas universidades de Berkeley e Stanford [Hen84] ratificaram as idéias descritas acima. Compiladores geram código de melhor qualidade para arquiteturas RISC. A qualidade do código é medida em função do que ele pode ser melhorado se cuidadosamente escrito a mão. Como nas experiências o mesmo compilador foi utilizado, mudando apenas a descrição da máquina alvo, conclui-se que é mais difícil conseguir bom código em máquinas de grandes conjuntos de instruções, principalmente quando estes são irregulares.

#### 2.6 RISC versus CISC

Uma arquitetura RISC que executa instruções muito eficientemente só é atrativa se o número destas instruções não for excessivo em relação ao número de instruções CISC para executar a mesma tarefa.

Números apresentados em [Rad82] indicam que o número de instruções RISC é até 50% maior que o equivalente CISC para executar a mesma tarefa. Medidas estáticas mais recentes apontam um limite de apenas 20% [Muc90a]. Em qualquer caso, o reduzido número de ciclos por instrução é suficiente para sobrepor o mais alto número de instruções, em relação a CISCs [BC91].

A desvantagem potencial de um grande número de instruções executadas à taxa de uma a cada ciclo de relógio é a alta banda de passagem<sup>5</sup> de memória necessária. Todavia, desde que caches de instruções são apenas lidos, seu projeto é mais simples. O trabalho de Davidson [DV87] mostra que para acesso a instruções, um cache de 64 Kb tem a mesma taxa de acerto em RISCs e CISCs. Do ponto de vista de operandos, as arquiteturas LOAD/STORE têm menos requerimentos de memória quando os programas passaram por um alocador de registradores. Isto é importante porque o acesso a dados é menos previsível do que o acesso a instruções, diminuindo a eficiência do cache.

A grandeza mais difícil de remover quando comparando uma máquina RISC e uma CISC é a tecnologia usada na implementação. O que é mais razoável nestes casos é tornar comparáveis máquinas que possuem preços semelhantes.

Sem desejar apresentar conclusões definitivas tenta-se, a seguir, quantificar o desempenho de duas arquiteturas: O MC68020 (CISC) e a SPARC (RISC). O MC68020 gasta, em média, 7 ciclos

<sup>5</sup>do inglês: bandwidth

de relógio para executar uma instrução. Em um RISC típico, esse valor está em torno de 1,5. O primitivismo das instruções faz com que o número de instruções RISC para executar uma tarefa seja até 20% major que o equivalente em CISC [Muc90a]. Independente do benchmark vale a relação:

$$T_e = \frac{N_i \times T_c}{C}$$

, onde:

- T<sub>e</sub> Tempo de execução de um programa;

- N<sub>i</sub> Número de instruções executadas;

- T<sub>c</sub> Tempo médio de cíclo de instrução (em ciclos de relógio);

- C A freqüência do relógio da máquina.

Na ausência de informações específicas sobre um programa, essa relação e os dados acima, mostram que um processador RISC pode ser quatro vezes mais rápido que um CISC de mesma freqüência de relógio. Note-se que os resultados variam em função do mix de instruções no benchmark e ignoram atrasos devido ao cache. Considere-se também que o tempo de execução de um programa não depende exclusivamente da velocidade do processador.

#### 2.7 Ponto Flutuante em RISC

Desde muito cedo ficou claro que introduzir operações de ponto flutuante em arquiteturas RISC era uma tarefa complexa. Por natureza, operações sobre números reais podem ter custo algumas vezes maior que sobre inteiros. Aumentar o número de estágios do pipeline ou o tempo de ciclo básico foi ignorado porque:

- Grande parte das aplicações não têm operações de ponto flutuante;

- O desempenho de aplicações de ponto flutuante é fortemente dependente de operações sobre inteiros (acesso à memória, cálculos de endereços). O programa navega, por exemplo, tem pouco mais 25% de suas instruções operando sobre números reais (medidas estaticamente).