# UNIVERSIDADE ESTADUAL DE CAMPINAS Instituto de Computação

#### RAFAEL AULER

OPENISA, A HYBRID ISA

OPENISA, UM CONJUNTO DE INSTRUÇÕES HÍBRIDO

#### Rafael Auler

#### OpenISA, a hybrid ISA

#### OpenISA, um conjunto de instruções híbrido

Dissertation presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Doctor in Computer Science.

Tese apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Doutor em Ciência da Computação.

Supervisor/Orientador: Prof. Dr. Edson Borin

Este exemplar corresponde à versão final da Tese defendida por Rafael Auler e orientada pelo Prof. Dr. Edson Borin.

#### Agência(s) de fomento e nº(s) de processo(s): FAPESP, 2011/09630-1

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Auler, Rafael, 1986-

Au510 OpenISA, a hybrid ISA / Rafael Auler. – Campinas, SP: [s.n.], 2016.

Orientador: Edson Borin.

Tese (doutorado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Máquinas virtuais. 2. Interpretadores (Programas de computador). 3. Computadores com conjunto de instruções reduzido. 4. Microprocessadores - Projetos e construção. 5. Compiladores (Programas de computador). I. Borin, Edson,1979-. II. Universidade Estadual de Campinas. Instituto de Computação. III. Título.

#### Informações para Biblioteca Digital

Título em outro idioma: OpenISA, um conjunto de instruções híbrido

Palavras-chave em inglês:

Virtual machines

Interpreters (Computer programs)

Reduced instruction set computers

Microprocessors - Design and construction

Compilers (Computer programs)

**Área de concentração:** Ciência da Computação **Titulação:** Doutor em Ciência da Computação

Banca examinadora: Edson Borin [Orientador]

Philippe Olivier Alexandre Navaux Fernando Magno Quintão Pereira

Rodolfo Jardim de Azevedo

Sandro Rigo

**Data de defesa:** 23-09-2016

Programa de Pós-Graduação: Ciência da Computação

#### UNIVERSIDADE ESTADUAL DE CAMPINAS Instituto de Computação

#### Rafael Auler

#### OpenISA, a hybrid ISA

#### OpenISA, um conjunto de instruções híbrido

#### Banca Examinadora:

- Prof. Dr. Edson Borin IC UNICAMP

- Prof. Dr. Philippe Olivier Alexandre Navaux INF - UFRGS

- Prof. Dr. Fernando Magno Quintão Pereira DCC UFMG

- Prof. Dr. Rodolfo Jardim de Azevedo IC UNICAMP

- Prof. Dr. Sandro Rigo IC UNICAMP

A ata da defesa com as respectivas assinaturas dos membros da banca encontra-se no processo de vida acadêmica do aluno.

Campinas, 23 de setembro de 2016

# Acknowledgements

I would like to thank my invaluable colleagues during the development of this PhD thesis: Bruno Cardoso, with whom I shared the happiness of publishing the first book in English about LLVM; Raoni Fassina, for the many interesting discussions and podcasts recommendations; Tiago Falcao, for being a friend since my first year at UNICAMP when I was an undergrad; Maxiwell, for the insightful discussions about spirituality, chess, entrepeneurship and music; Joao Moreira, for everything we shared, including a house in the summer of 2013 in Seattle; Leonardo Piga, for showing me that hard work, endurance and persistence pays off; Thiago Abdnur, for the excellent reading recommendations; Daniel Nicacio, for always being in touch with us despite living far away in the Scandinavian Peninsula; Leonardo Ecco, for your companionship during the early years; Alexandro Baldassin, for presenting me to grad school; and Gabriel Ferreira, for showing me the importance of curiosity, diligence and the taste for writing.

I thank Microsoft Research for the fellowship and internship in 2013 and the people there that helped me develop a good project, including Peli de Halleux, Michal Moskal and Nikolai Tillmann. I thank Sony Computing Entertainment America for the internship in 2014, in special Alex Rosenberg, Rafael Espindola and Sean Silva. I thank Facebook for the internship in late 2015, in special Guilherme Ottoni, Maxim Panchenko and Surupa Biswas.

Above all, I thank my partner Raysa for the love and patience that was essential to make my life during the PhD such a great time I will remember dearly.

Finally, I thank my advisor, Edson, for all the support, guidance, meetings and conversations that lead to this thesis.

### Resumo

OpenISA é concebido como a interface de processadores que pretendem ser altamente flexíveis. Isto é conseguido por meio de três estratégias: em primeiro lugar, o ISA é empiricamente escolhido para ser facilmente traduzido para outros, possibilitando flexibilidade do software no caso de um processador OpenISA físico não estar disponível. Neste caso, não há nenhuma necessidade de aplicar um processador virtual OpenISA em software. O ISA está preparado para ser estaticamente traduzido para outros ISAs. Segundo, o ISA não é um ISA concreto nem um ISA virtual, mas um híbrido com a capacidade de admitir modificações nos opcodes sem afetar a compatibilidade retroativa. Este mecanismo permite que as futuras versões do ISA possam sofrer modificações em vez de extensões simples das versões anteriores, um problema comum com ISA concretos, como o x86. Em terceiro lugar, a utilização de uma licença permissiva permite o ISA ser usado livremente por qualquer parte interessada no projeto. Nesta tese de doutorado, concentramo-nos nas instruções de nível de usuário do OpenISA. A tese discute (1) alternativas para ISAs, alternativas para distribuição de programas e o impacto de cada opção, (2) características importantes de OpenISA para atingir seus objetivos e (3) fornece uma completa avaliação do ISA escolhido com respeito a emulação de desempenho em duas CPUs populares, uma projetada pela Intel e outra pela ARM. Concluímos que a versão do OpenISA apresentada aqui pode preservar desempenho próximo do nativo quando traduzida para outros hospedeiros, funcionando como um modelo promissor para ISAs flexíveis da próxima geração que podem ser facilmente estendidos preservando a compatibilidade. Ainda, também mostramos como isso pode ser usado como um formato de distribuição de programas no nível de usuário.

# Abstract

OpenISA is designed as the interface of processors that aim to be highly flexible. This is achieved by means of three strategies: first, the ISA is empirically chosen to be easily translated to others, providing software flexibility in case a physical OpenISA processor is not available. Second, the ISA is not a concrete ISA nor a virtual ISA, but a hybrid one with the capability of admitting modifications to opcodes without impacting backwards compatibility. This mechanism allows future versions of the ISA to have real changes instead of simple extensions of previous versions, a common problem with concrete ISAs such as the x86. Third, the use of a permissive license allows the ISA to be freely used by any party interested in the project. In this PhD. thesis, we focus on the user-level instructions of OpenISA. The thesis discusses (1) ISA alternatives, program distribution alternatives and the impact of each choice, (2) important features of OpenISA to achieve its goals and (3) provides a thorough evaluation of the chosen ISA with respect to emulation performance on two popular host CPUs, one from Intel and another from ARM. We conclude that the version of OpenISA presented here can preserve close-to-native performance when translated to other hosts, working as a promising model for next-generation, flexible ISAs that can be easily extended while preserving backwards compatibility. Furthermore, we show how this can also be a program distribution format at user-level.

# List of Figures

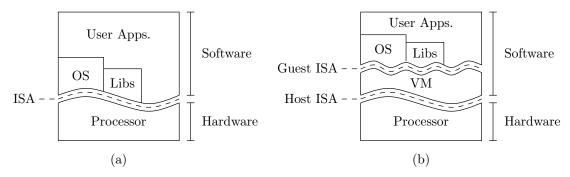

| 2.1                                    | Virtual machine stack comparison diagram                                                                                                                                                                                              | 22                               |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

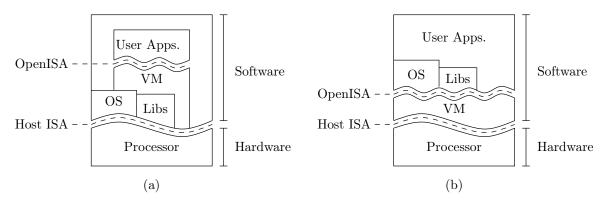

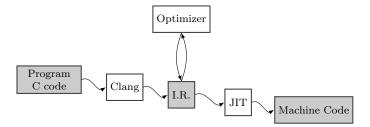

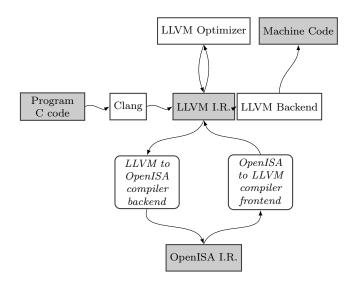

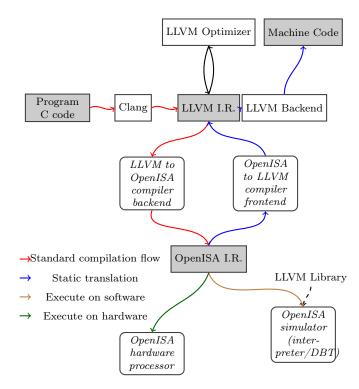

| 3.1<br>3.2<br>3.3<br>3.4               | OpenISA process virtual machine versus system virtual machine Diagram showing the usage of LLVM as the starting point for OpenISA Diagram showing the relationship of OpenISA and LLVM Diagram showing the complete OpenISA framework | 36<br>37<br>38<br>39             |

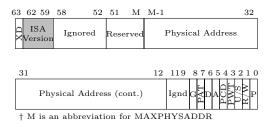

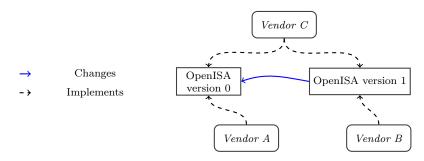

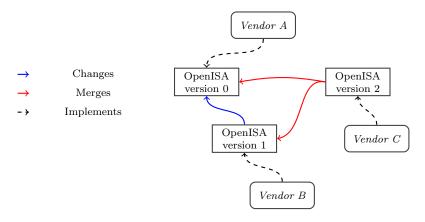

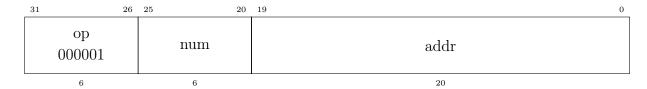

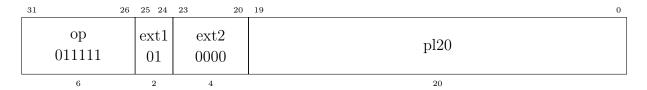

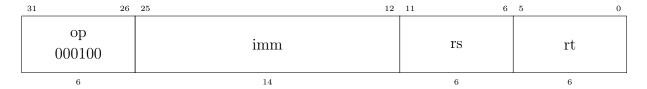

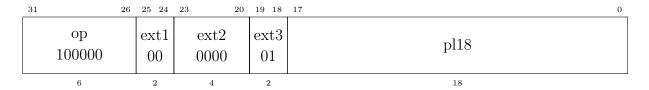

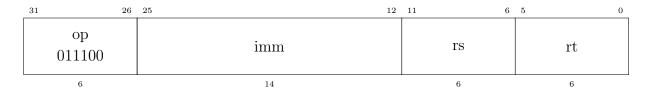

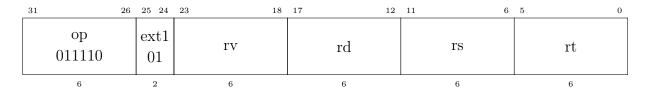

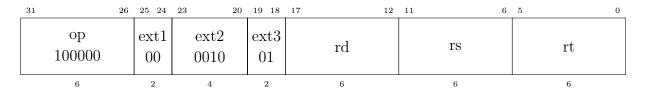

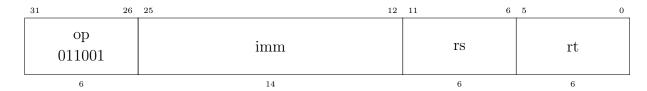

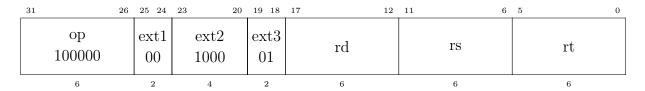

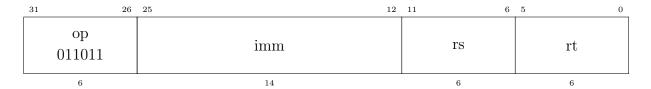

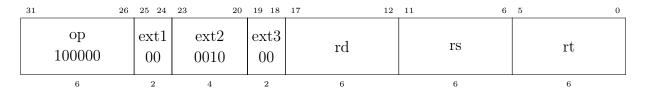

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Load instruction encoding diagram                                                                                                                                                                                                     | 43<br>44<br>46<br>47<br>48<br>49 |

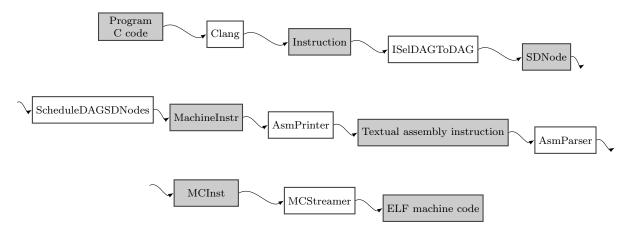

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | The life cycle of the minimal program particle, an instruction, traversing the LLVM backend                                                                                                                                           | 52<br>52<br>54<br>55<br>56<br>60 |

| 6.1<br>6.2<br>6.3<br>6.4               | Pseudo-code that determines whether a single ARM instruction should proceed to the execution stage                                                                                                                                    | 64<br>75<br>76<br>78             |

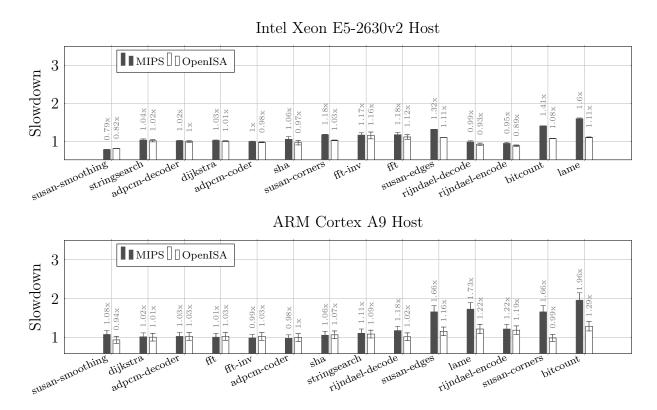

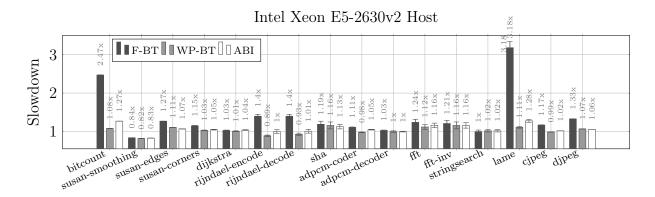

| 7.1 7.2 7.3 7.4 7.5 7.6 7.7            | Ordered slowdows for OpenISA to x86 and ARM translations, relative to native performance - Shootout Programs (simple kernels)                                                                                                         | 81<br>84<br>86<br>87<br>88<br>89 |

|                                        | Programs (Complex programs)                                                                                                                                                                                                           | 92                               |

| 7.8 | Ordered slowdows for OpenISA to x86 translation, relative to native per- |    |

|-----|--------------------------------------------------------------------------|----|

|     | formance - SPEC CPU2006                                                  | 93 |

# List of Tables

| 2.1 | Comparison table with the performance of different translation systems                                                                                                                                                 | 28       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1 | OpenISA opcode space utilization by payload size                                                                                                                                                                       | 44       |

| 5.1 | Description of the selected benchmark programs                                                                                                                                                                         | 59       |

|     | Mibench results for different ISAs simulations with ArchC Simulation performance comparison table extracted from the OVP website                                                                                       | 64<br>65 |

| 7.2 | Comparison of native and translated versions of the matrix benchmark Comparison of native and translated versions of the ackermann benchmark Comparison of native and translated versions of the SUSAN-edges benchmark | 85       |

| 7.4 | Comparison of native and translated versions of the riindael benchmark                                                                                                                                                 | 90       |

# Contents

| 1 | Intr | roduction                                           | 17         |

|---|------|-----------------------------------------------------|------------|

|   | 1.1  | Challenges in the design of classic ISAs            | 17         |

|   | 1.2  | Virtual machines to ease software deployment        |            |

|   | 1.3  | Introducing the hybrid ISA solution                 |            |

|   | 1.4  | Contributions and thesis organization               |            |

|   |      |                                                     |            |

| 2 | Rel  | ated work                                           | <b>2</b> 2 |

|   | 2.1  | Basic concepts                                      | 22         |

|   | 2.2  | Well-known virtual machines                         | 23         |

|   |      | 2.2.1 Low-level ISA vs bytecode guest architecture  | 24         |

|   |      | 2.2.2 Comparison with recently developed ISAs       | 25         |

|   | 2.3  | The ISA level                                       | 26         |

|   | 2.4  | ISA translation                                     | 27         |

|   | 2.5  | Performance supported by current technologies       | 28         |

|   |      | 2.5.1 Interpreted performance                       | 29         |

|   |      | 2.5.2 Compiled simulation                           | 29         |

|   |      | 2.5.3 Retargetable dynamic binary translation (DBT) | 29         |

|   |      | 2.5.4 High-performing retargetable DBTs             | 30         |

|   |      | 2.5.5 Other approaches                              | 30         |

|   |      | 2.5.6 Specialized DBTs                              | 31         |

|   | 2.6  | Dynamic binary instrumentation                      | 31         |

|   | 2.7  | Summary                                             | 31         |

| _ |      |                                                     |            |

| 3 | -    | enISA overview                                      | 33         |

|   | 3.1  | OpenISA objectives                                  |            |

|   | 3.2  | Design trade-offs                                   |            |

|   |      | 3.2.1 Explicit functions                            |            |

|   |      | 3.2.2 Explicit stack                                | 35         |

|   |      | 3.2.3 Abstract memory locations                     |            |

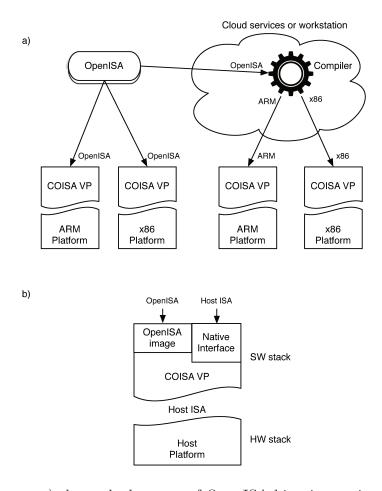

|   | 3.3  | OpenISA virtual machine                             |            |

|   |      | 3.3.1 Using the LLVM I.R. as the starting point     |            |

|   |      | 3.3.2 Using LLVM indirectly                         | 38         |

|   |      | 3.3.3 The Complete Framework                        | 38         |

|   | 3.4  | Summary                                             | 39         |

| 4 | 0    | on IC A consisting and manualing manual arrivant    | 11         |

| 4 | -    | enISA encoding and recycling mechanism              | 41         |

|   | 4.1  | Word size and endianness                            | 41         |

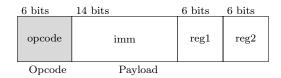

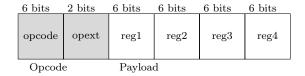

|   | 4.2  | Encoding                                            | 42<br>42   |

|   |      | 4 Z. L. HISLTHCHOH SIZES                            | 4/         |

|   |     | 4.2.2 Instruction formats                                   | 43        |

|---|-----|-------------------------------------------------------------|-----------|

|   |     | 4.2.3 Opcode space utilization                              | 44        |

|   | 4.3 | The recycling mechanism                                     | 45        |

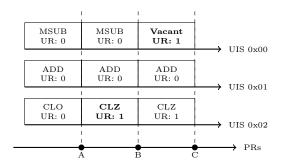

|   |     | 4.3.1 Overview                                              | 45        |

|   |     | 4.3.2 Mechanism description                                 | 46        |

|   |     | 4.3.3 OpenISA formats philosophy                            | 47        |

|   |     | 4.3.4 OpenISA versioning scenarios                          | 48        |

|   | 4.4 | Summary                                                     | 49        |

| 5 | Exp | perimental framework                                        | 50        |

|   | 5.1 | Opening remarks                                             | 50        |

|   | -   | 5.1.1 A byproduct of the experimental framework             | 51        |

|   | 5.2 | LLVM to OpenISA compiler backend                            | 51        |

|   | 5.3 | OpenISA ArchC-based simulator                               | 53        |

|   | 5.4 | OpenISA static binary translator                            | 54        |

|   | 5.5 | Runtime library                                             | 58        |

|   | 5.6 | OpenISA toolchain                                           | 58        |

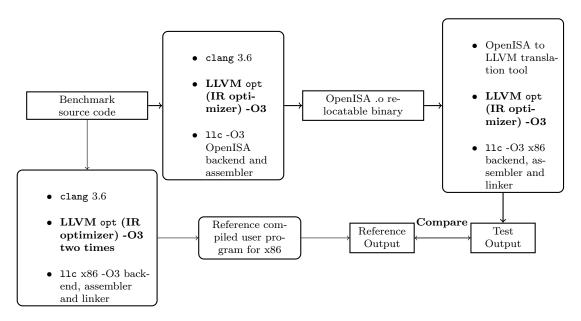

|   | 5.7 | OpenISA evaluation workflow                                 | 59        |

|   | 5.8 | Summary                                                     | 61        |

|   | 0.0 | Summary                                                     | OI        |

| 6 | Ope | enISA design for easy emulation                             | <b>62</b> |

|   | 6.1 | ISAs with faster emulation                                  | 62        |

|   | 6.2 | OpenISA design choices in favor of emulation                | 66        |

|   |     | 6.2.1 Primary design choices                                | 66        |

|   |     | 6.2.2 Rejected design choice                                | 71        |

|   |     | 6.2.3 Secondary design choices                              | 72        |

|   |     | 6.2.4 Metadata design                                       | 73        |

|   | 6.3 | Register mapping techniques                                 | 74        |

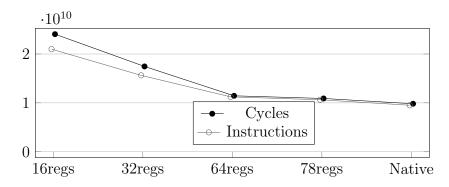

|   |     | 6.3.1 Whole program binary translation                      | 75        |

|   | 6.4 | A practical application of the static translation prototype | 77        |

|   | 6.5 | Summary                                                     | 79        |

| 7 | Exp | perimental Results                                          | 80        |

|   | 7.1 | Host Platform                                               | 80        |

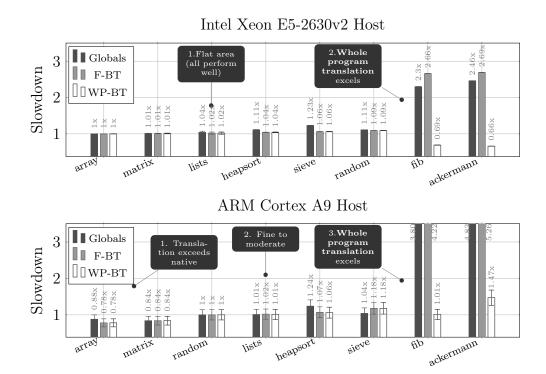

|   | 7.2 | Simple benchmarks                                           | 80        |

|   |     | 7.2.1 The Fibonacci Case                                    | 82        |

|   |     | 7.2.2 Whole program translation beating native performance  | 83        |

|   |     | 7.2.3 The Matrix Case                                       | 84        |

|   |     | 7.2.4 The Ackermann Case                                    | 85        |

|   |     | 7.2.5 The Sieve Case                                        | 85        |

|   |     | 7.2.6 The Array Case                                        | 86        |

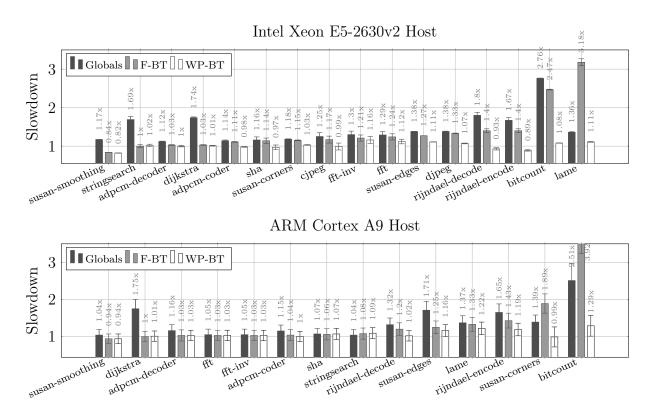

|   | 7.3 | Complex Benchmarks                                          | 87        |

|   | ,   | 7.3.1 The SUSAN Case                                        | 89        |

|   |     | 7.3.2 The Rijndael Case                                     | 90        |

|   |     | 7.3.3 The LAME Case                                         | 91        |

|   | 7.4 | A closer look on WP-BT                                      | 91        |

|   | 7.5 | SPEC CPU2006 programs                                       | 92        |

|   | 7.6 | Summary                                                     | 93        |

|   | 1.0 | Summary                                                     | 55        |

| 8            | Oth<br>8.1<br>8.2<br>8.3 | ter exploratory work and contributions  The C language level      | . 96  |

|--------------|--------------------------|-------------------------------------------------------------------|-------|

| 9            | Con                      | nclusion                                                          | 100   |

| Bi           | bliog                    | graphy                                                            | 102   |

| $\mathbf{A}$ |                          | enISA instruction set reference                                   | 112   |

|              | A.1                      | abs.d                                                             |       |

|              | A.2                      | abs.s                                                             |       |

|              | A.3                      |                                                                   |       |

|              | A.4                      | add.d                                                             |       |

|              | A.5                      | add.s                                                             |       |

|              | A.6                      | addi                                                              |       |

|              | A.7                      | andi                                                              | _     |

|              | A.8                      | and                                                               |       |

|              | A.9                      | asr                                                               |       |

|              |                          | ) asrr                                                            |       |

|              |                          | $1 \; \mathrm{bc1f} \; \ldots \ldots \ldots \ldots \ldots \ldots$ |       |

|              |                          | 2 bc1fl                                                           |       |

|              | _                        | B bc1t                                                            |       |

|              |                          | 4 bc1t                                                            |       |

|              | A.15                     | break                                                             | . 127 |

|              |                          | 5 c.eq.d                                                          |       |

|              | A.17                     | 7 c.eq.s                                                          | . 129 |

|              | A.18                     | B c.ole.d                                                         | . 130 |

|              | A.19                     | heta c.ole.s                                                      | . 131 |

|              | A.20                     | $0 \mathrm{\ c.olt.d}$                                            | . 132 |

|              | A.21                     | l c.olt.s                                                         | . 133 |

|              | A.22                     | 2 c.ueq.d                                                         | . 134 |

|              | A.23                     | 8 c.ueq.s                                                         | . 135 |

|              | A.24                     | 4 c.ule.d                                                         | . 136 |

|              | A.25                     | ó c.ule.s                                                         | . 137 |

|              | A.26                     | 5 c.ult.d                                                         | . 138 |

|              | A.27                     | 7 c.ult.s                                                         | . 139 |

|              | A.28                     | 8 c.un.d                                                          | . 140 |

|              | A.29                     | 9 c.un.s                                                          |       |

|              |                          |                                                                   |       |

|              |                          |                                                                   |       |

|              | _                        | 2 ceil.w.d                                                        |       |

|              |                          | B ceil.w.s                                                        |       |

|              | A.34                     |                                                                   |       |

|              |                          | m 6cvt.d.s                                                        |       |

|              |                          | $6 \operatorname{cvt.d.w}$                                        |       |

|              |                          | $7~\mathrm{cvt.s.d}$                                              |       |

|              |                          | 8 cvt.s.w                                                         |       |

|              |                          | 9 div.d                                                           |       |

|              | 41.09                    | / Ш.ү.Ч                                                           | . тот |

| A.40 div.s     | 152 |

|----------------|-----|

| A.41 div       |     |

|                |     |

| A.42 divu      |     |

| A.43 ext       |     |

| A.44 floor.w.d | 156 |

| A.45 floor.w.s | 157 |

| A.46 ijmphi    | 158 |

| A.47 ijmp      |     |

| A.48 jeq       |     |

| V I            |     |

| A.49 jgez      |     |

| A.50 jgtz      |     |

| A.51 jlez      | 163 |

| A.52 jltz      | 164 |

| A.53 jne       | 165 |

| A.54 jump      |     |

| A.55 jumpr     |     |

| <i>y</i> 1     |     |

| A.56 ldbu      |     |

| A.57 ldb       |     |

| A.58 ldc1      | 170 |

| A.59 ldh       | 171 |

| A.60 ldhu      | 172 |

| A.61 ldi       |     |

| A.62 ldihi     |     |

|                |     |

| A.63 ldwl      |     |

| A.64 ldwr      |     |

| A.65 ldw       | 177 |

| A.66 ldxc1     | 178 |

| A.67 ll        | 179 |

| A.68 lwc1      |     |

| A.69 lwxc1     |     |

|                |     |

| A.70 madd.d    |     |

| A.71 madd.s    | 183 |

| A.72 mfc1      | 184 |

| A.73 mfhc1     | 185 |

| A.74 mflc1     | 186 |

| A.75 mov.d     |     |

| A.76 mov.s     |     |

|                |     |

| A.77 movf      |     |

| A.78 movf.d    | 190 |

| A.79 movf.s    | 191 |

| A.80 movn.d    | 192 |

| A.81 movn.s    | 193 |

| A.82 movn      |     |

|                | -   |

| A.83 movt      | 195 |

| A.84 movt.d    |     |

| A.85 movt.s    | 197 |

| A.86 movz.d    | 198 |

| A.87 movz.s    | 199 |

| A.89 msub.d       201         A.90 msub.s       202         A.91 mtc1       203         A.92 mthc1       204         A.93 mtlc1       205         A.94 mul.d       206         A.95 mul.s       207         A.96 mulu       208         A.97 mul       209         A.98 neg.d       210         A.99 neg.s       211         A.100 nor       212         A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 ror       216         A.105 ro       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdc2       222         A.111 scb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shr       233         A.112 seh       234         A.113 shl       236         A.125 stu       233         A.125 stw       233     <                             | A.88 movz       | . 200 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|

| A.90 msub.s       202         A.91 mtcl       203         A.92 mtlcl       205         A.93 mtlcl       205         A.94 mul.d       206         A.95 mul.s       207         A.96 mulu       208         A.97 mul       209         A.98 neg.d       210         A.99 neg.s       211         A.100 nor       212         A.101 or       213         A.102 roi       214         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.wd       218         A.107 round.ws       219         A.108 sc       220         A.110 sdxcl       221         A.110 sdxcl       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shr       228         A.117 stit       229         A.118 stb       230         A.119 stitu       231         A.120 stu       232         A.121 sqrt.d       233                             | A.89 msub.d     | . 201 |

| A.91 mtcl       203         A.92 mtbcl       204         A.93 mtlcl       205         A.94 mul.d       206         A.95 mul.s       207         A.96 mulu       208         A.97 mul       209         A.98 neg.d       210         A.99 neg.s       211         A.100 nor       212         A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 ror       216         A.105 ror       217         A.106 round.wd       218         A.107 round.ws       219         A.108 sc       220         A.109 sdcl       221         A.110 sdxcl       222         A.111 seb       223         A.112 seh       224         A.113 shir       225         A.114 shl       226         A.115 shr       227         A.116 shr       228         A.117 slti       23         A.120 sltu       231         A.121 sth       236         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236     <                             |                 |       |

| A.92 mthc1       204         A.93 mtlc1       205         A.94 mul.d       206         A.95 mul.s       207         A.96 mulu       208         A.97 mul       209         A.98 ngd       210         A.99 negs       211         A.100 nor       212         A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 scb       223         A.112 sch       224         A.113 shir       225         A.114 shi       226         A.115 shr       227         A.116 shrr       228         A.117 slti       230         A.119 sltiu       231         A.120 sltu       232         A.112 spt.d       233         A.122 spt.s       234         A.123 stb       235         A.124 sth       236                              |                 |       |

| A.93 mtlc1       205         A.94 mtl.d       206         A.95 mtls       207         A.96 mtlu       208         A.97 mtl       209         A.98 neg.d       210         A.99 neg.s       211         A.100 nor       212         A.102 ori       213         A.102 reall       215         A.103 reall       215         A.104 rorr       216         A.105 ro       217         A.106 round.wd       218         A.107 round.ws       219         A.108 se       220         A.109 sdcl       221         A.110 sdxcl       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shlr       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 stwl       234         A.123 stb       235         A.125 stw       237 <td></td> <td></td>        |                 |       |

| A.94 mul.d       206         A.95 muls       207         A.96 mulu       208         A.97 mul       209         A.98 neg.d       210         A.99 neg.s       211         A.100 nor       212         A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 ror       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdcl       221         A.110 sdxcl       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shr       228         A.117 sti       229         A.118 st       230         A.129 stu       23         A.121 sqrt.d       23         A.122 sqrt.s       23         A.123 stb       23         A.125 stw       236         A.125 stw       236         A.125 stw       237                                       |                 |       |

| A.95 mul.s       207         A.96 mulu       208         A.97 mul       209         A.98 neg.d       210         A.99 neg.s       211         A.100 nor       212         A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.109 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       222         A.113 shlr       225         A.114 shl       225         A.115 shr       227         A.116 shrr       228         A.117 slti       228         A.117 slti       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       234         A.125 stw       237         A.125 stw       237         A.125 stw       234         A.125 stw       234 <td></td> <td></td>       |                 |       |

| A.96 mulu       208         A.97 mul       209         A.98 neg.d       210         A.99 negs       211         A.100 nor       212         A.102 vi       214         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shr       228         A.117 slti       228         A.119 sltu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       236         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.133 swcl       242 <td></td> <td></td>       |                 |       |

| A.97 mul       209         A.98 neg.d       210         A.99 neg.s       211         A.100 nor       212         A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.109 sdcl       220         A.109 sdcl       221         A.110 sdxcl       222         A.111 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 sti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.133 swcl       24                        |                 |       |

| A.98 neg.d       210         A.99 neg.s       211         A.100 nor       212         A.102 ori       213         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdcl       221         A.110 sdxcl       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       236         A.127 stwr       239 </td <td></td> <td></td> |                 |       |

| A.99 neg.s       211         A.100 nor       212         A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdcl       221         A.110 sdxcl       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 strb       234         A.123 stb       234         A.125 stw       237         A.126 stwl       236         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 syscl       24                        |                 |       |

| A.100 nor       212         A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       223         A.112 seh       224         A.113 shlr       226         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 stit       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       234         A.125 stw       237         A.126 stwl       238         A.127 stwr       238         A.127 stwr       238         A.129 sub.s       241         A.130 sub       242         A.131 sywcl       244         A.133 sync       2                        |                 |       |

| A.101 or       213         A.102 ori       214         A.103 reall       215         A.104 rorr       216         A.105 ro       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shr       227         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       232         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       238         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swcl       243         A.133 sync       245                        |                 |       |

| A.102 ori       214         A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       224         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sttb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       236         A.127 stwr       238         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.133 sync       244         A.134 syscall       246                                               |                 |       |

| A.103 reall       215         A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       225         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       232         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.130 sub       242         A.131 swcl       243         A.132 succl       244         A.133 sync       245         A.134 syscall       246                                             |                 |       |

| A.104 rorr       216         A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdcl       221         A.110 sdxcl       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swcl       243         A.132 swcl       244         A.133 sync       245         A.134 syscall       246                                              |                 |       |

| A.105 ror       217         A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       223         A.112 sch       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swcl       243         A.132 swccl       244         A.133 sync       245         A.134 syscall       246                                                                          |                 | _     |

| A.106 round.w.d       218         A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                    |                 |       |

| A.107 round.w.s       219         A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       234         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                        | A.105 ror       | . 217 |

| A.108 sc       220         A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                          | A.106 round.w.d | . 218 |

| A.109 sdc1       221         A.110 sdxc1       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                     | A.107 round.w.s | . 219 |

| A.110 sdxc1       222         A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       238         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.134 syscall       245         A.134 syscall       246                                                                                                                                                                                                                               | A.108 sc        | . 220 |

| A.111 seb       223         A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                | A.109 sdc1      | . 221 |

| A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                            | A.110 sdxc1     | . 222 |

| A.112 seh       224         A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                            | A.111 seb       | . 223 |

| A.113 shlr       225         A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swcl       243         A.132 swxcl       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                        |                 |       |

| A.114 shl       226         A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swcl       243         A.132 swxcl       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                     |                 |       |

| A.115 shr       227         A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                 |                 |       |

| A.116 shrr       228         A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                             |                 |       |

| A.117 slti       229         A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |       |

| A.118 slt       230         A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |       |

| A.119 sltiu       231         A.120 sltu       232         A.121 sqrt.d       233         A.122 sqrt.s       234         A.123 stb       235         A.124 sth       236         A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |       |

| A.120 sltu232A.121 sqrt.d233A.122 sqrt.s234A.123 stb235A.124 sth236A.125 stw237A.126 stwl238A.127 stwr239A.128 sub.d240A.129 sub.s241A.130 sub242A.131 swc1243A.132 swxc1244A.133 sync245A.134 syscall246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |       |

| A.121 sqrt.d233A.122 sqrt.s234A.123 stb235A.124 sth236A.125 stw237A.126 stwl238A.127 stwr239A.128 sub.d240A.129 sub.s241A.130 sub242A.131 swc1243A.132 swxc1244A.133 sync245A.134 syscall246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |       |

| A.122 sqrt.s234A.123 stb235A.124 sth236A.125 stw237A.126 stwl238A.127 stwr239A.128 sub.d240A.129 sub.s241A.130 sub242A.131 swc1243A.132 swxc1244A.133 sync245A.134 syscall246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 | _     |

| A.123 stb235A.124 sth236A.125 stw237A.126 stwl238A.127 stwr239A.128 sub.d240A.129 sub.s241A.130 sub242A.131 swc1243A.132 swxc1244A.133 sync245A.134 syscall246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -               |       |

| A.124 sth236A.125 stw237A.126 stwl238A.127 stwr239A.128 sub.d240A.129 sub.s241A.130 sub242A.131 swc1243A.132 swxc1244A.133 sync245A.134 syscall246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •               |       |

| A.125 stw       237         A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |       |

| A.126 stwl       238         A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |       |

| A.127 stwr       239         A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |       |

| A.128 sub.d       240         A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |       |

| A.129 sub.s       241         A.130 sub       242         A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |       |

| A.130 sub                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A.128 sub.d     | . 240 |

| A.131 swc1       243         A.132 swxc1       244         A.133 sync       245         A.134 syscall       246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A.129 sub.s     | . 241 |

| A.132 swxc1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A.130 sub       | . 242 |

| A.133 sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A.131 swc1      | . 243 |

| A.134 syscall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A.132 swxc1     | . 244 |

| A.134 syscall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A.133 sync      | . 245 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | v               |       |

| 11.100 tog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A.135 teq       |       |

| A.136 trunc.w.d | 3 |

|-----------------|---|

| A.137 trunc.w.s | ) |

| A.138 xor       | ) |

| A.139 xori      | Ĺ |

# Chapter 1

## Introduction

The ISA, Instruction Set Architecture, is the interface that allows applications and the processor to be developed independently. It is a contract. As long as the application code and the processor microarchitecture comply with the ISA, the processor should be able to properly execute applications. There are currently several different ISAs that software can use to leverage a circuit to do useful work, ranging from complex general purpose instruction sets to simpler ones, dedicated to graphics processing.

This chapter discusses challenges brought by this classic ISA definition, then proceeds to present the solution virtual machines provide and concludes with the hybrid ISA approach championed by this thesis. This chapter also shows how this thesis is organized and summarizes its contributions.

#### 1.1 Challenges in the design of classic ISAs

Coping with the strict requirements of the ISA interface raises at least three big technical challenges:

- 1. Hardware challenge: Each ISA decision affects all future generations. In effect, changing features of an ISA that was already shipped to the market deems the previous generation incompatible. In practice, to keep backwards compatiblity, the hardware typically is limited to be only extended. This implies ISAs will always become larger, more cluttered and more inefficient as each new generation is introduced [92].

- 2. Software challenge: The software, once compiled to a specific ISA, demands a non-trivial effort to be ported to run on other ISAs.

- 3. Market challenge: Past ISAs accumulate a legacy of available software. Creating a brand new ISA is discouraged because of this significant amount of effort to port software. Since current ISAs are mostly proprietary, new processor manufacturers are not encouraged to exist in the market if they need to license the rights to reproduce the ISA from another company. This strengthens monopoly in the computer processors market.