#### Universidade Estadual de Campinas Instituto de Computação

### Jefferson Rodrigo Capovilla

Improving the Statistical Variability of Delay-based Physical Unclonable Functions

Otimização da Variabilidade Estatística em Circuitos Physical Unclonable Functions Baseados em Atraso

#### Jefferson Rodrigo Capovilla

# Improving the Statistical Variability of Delay-based Physical Unclonable Functions

# Otimização da Variabilidade Estatística em Circuitos Physical Unclonable Functions Baseados em Atraso

Dissertação apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação.

Thesis presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Master in Computer Science.

Supervisor/Orientador: Prof. Dr. Guido Costa Souza de Araújo Co-supervisor/Coorientador: Prof. Dr. Mario Lúcio Côrtes

Este exemplar corresponde à versão final da Dissertação defendida por Jefferson Rodrigo Capovilla e orientada pelo Prof. Dr. Guido Costa Souza de Araújo.

#### Agência(s) de fomento e nº(s) de processo(s): Não se aplica.

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Capovilla, Jefferson Rodrigo, 1984-

C173i

Improving the statistical variability of delay-based Physical Unclonable Functions / Jefferson Rodrigo Capovilla. – Campinas, SP: [s.n.], 2016.

Orientador: Guido Costa Souza de Araújo.

Coorientador: Mario Lúcio Côrtes.

Dissertação (mestrado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Funções físicas inclonáveis. 2. Variações do processo de fabricação. 3. Monte Carlo, Método de. 4. Circuitos integrados digitais. 5. Circuitos integrados - Integração em escala muito ampla. 6. Circuitos integrados - Integração em larga escala. 7. Criptografia de dados (Computação). I. Araújo, Guido Costa Souza de,1962-. II. Côrtes, Mario Lúcio,1950-. III. Universidade Estadual de Campinas. Instituto de Computação. IV. Título.

#### Informações para Biblioteca Digital

Título em outro idioma: Otimização da variabilidade estatística em circuitos Physical

Unclonable Functions baseados em atraso

#### Palavras-chave em inglês:

Physical unclonable functions

Manufacturing process variations

Monte Carlo method

Digital integrated circuits

Integrated circuits - Very large scale integration

Integrated circuits - Large scale integration

Data encryption (Computer science)

**Área de concentração:** Ciência da Computação **Titulação:** Mestre em Ciência da Computação

Banca examinadora:

Guido Costa Souza de Araújo [Orientador]

Carlos Alberto dos Reis Filho

Ricardo Pannain

Data de defesa: 18-03-2016

Programa de Pós-Graduação: Ciência da Computação

#### Universidade Estadual de Campinas Instituto de Computação

#### Jefferson Rodrigo Capovilla

# Improving the Statistical Variability of Delay-based Physical Unclonable Functions

# Otimização da Variabilidade Estatística em Circuitos Physical Unclonable Functions Baseados em Atraso

#### Banca Examinadora:

- Prof. Dr. Guido Costa Souza de Araújo (Orientador) Instituto de Computação - UNICAMP

- Prof. Dr. Carlos Alberto dos Reis Filho

Centro de Engenharia, Modelagem e Ciências Sociais Aplicadas UFABC

- Prof. Dr. Ricardo Pannain Instituto de Computação - UNICAMP

A ata da defesa com as respectivas assinaturas dos membros da banca encontra-se no processo de vida acadêmica do aluno.

Campinas, 18 de março de 2016

# Dedication

To my beloved family, Mario, Rose and Jessica. To my love, Daniela.

### Acknowledgements

I would like to first express my sincere gratitude to my research advisors, Prof. Guido Araújo and Prof. Mario Côrtes. This work would not be possible without their profound knowledge of VLSI design, sharp technical insights, and years after years of patient guidance. I also appreciate their effort in instructing me the techniques to write a scientific paper, and later in revising it. I can't thank Guido and Mario enough for always being supportive, making graduate school such a memorable adventure for me.

I'm also very grateful to Prof. Carlos Reis, Prof. Ricardo Pannain, Prof. Paulo Centoducatte and Prof. Frank Behrens for serving on my qualifying exam and dissertation committee. I am honoured to know that my work have been evaluated by reference professionals in the field of VLSI design, both in analog and digital perspective. Their sharp questions and critiques make me think deeper and in different perspectives about the challenges from the promising simulation result to real devices. In particular, Prof. Reis provided a deep analog analysis that should be considered when manufacturing the devices in silicon.

I would like also to thank the ones who helped me with the simulation infrastructure. Daniel Vidal, in setting up the simulation tools on external partition and performing some sanity tests; IT supporters of the Institute of Computing, who are always willing to help in my most peculiar difficulties. A special thank to LSC supporters, for working very hard in keeping all the necessary tools and remote access available.

The condition of doing the master's while working in a private company is a real challenge. So I would like to thank CPqD for encouraging me in keeping following the course, providing time for the weekly meetings, and being comprehensive on the moments I had to put extra effort on my research and during the dissertation.

Last, but not least, I would like to thank my loved ones, Mario, Rose, Jessica and Daniela, who have supported me throughout entire process, both by keeping me harmonious and helping me putting pieces together. I will be grateful forever for your love.

### Resumo

Physical Unclonable Functions (PUFs) são circuitos que exploram da variabilidade estatística do processo de fabricação para criar uma identidade única para os dispositivos. PUFs são usados na construção de primitivas criptográficas para aplicações tais como autenticação, geração de chaves e proteção de propriedade intelectual. Devido ao seu baixo custo e simplicidade de construção, Arbiter PUFs (APUFs) baseados em atraso são considerados um mecanismo criptográfico em potencial para a integração em dispositivos IoT de baixo custo (e.g. tags RFID). Embora APUFs já foram alvo de diversas pesquisas, pouco avanço foi feito em se avaliar como melhorar a imprevisibilidade destes circuitos utilizando técnicas de desenvolvimento de circuitos VLSI. Esta dissertação utiliza biblioteca AMS 350nm e simulação Monte-Carlo em SPICE para analisar como a seleção apropriada do elemento árbitro e o redimensionamento de células podem afetar a variabilidade de atraso de APUFs. Os resultados experimentais mostram que a combinação do árbitro apropriado e redimensionamento das células podem melhorar consideravelmente a distribuição do Peso de Hamming nas respostas do APUF, assim resultando em um projeto mais confiável e menos tendencioso.

### Abstract

Physical Unclonable Functions (PUFs) are circuits which exploit the statistical variability of the fabrication process to create a unique device identity. PUFs have been used in the design of cryptographic primitives for applications like device authentication, key generation and intellectual property protection. Due to its small cost and design simplicity, delay-based Arbiter PUFs (APUFs) have been considered a cryptographic engine candidate for the integration into low-cost IoT devices (e.g. RFID tags). Although APUFs have been extensively studied in the literature, not much work has been done in understanding how to improve its response variability using VLSI design techniques. This dissertation uses extensive AMS 350nm SPICE-based Monte-Carlo simulation to analyze how the proper selection of arbiter element and gate sizing can affect the delay variability of APUFs. Experimental results show that the combination of the appropriate arbiter and gate sizing configuration can considerably improve the Hamming Weight distribution of the APUF response, thus resulting in more reliable and less biased designs.

# List of Figures

| 2.1  | Generic delay PUF circuit                                                  | 18 |

|------|----------------------------------------------------------------------------|----|

| 2.2  | APUF mux circuit                                                           |    |

| 2.3  | Delay PUF circuit example (Chip 1)                                         | 19 |

| 2.4  | Delay PUF circuit example (Chip 2)                                         | 20 |

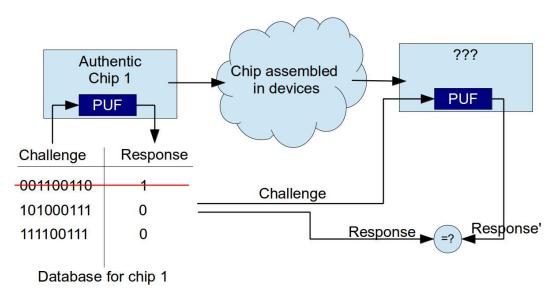

| 2.5  | PUF for authentication procedure                                           | 21 |

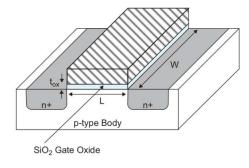

| 2.6  | Transistor geometry $[1]$                                                  | 22 |

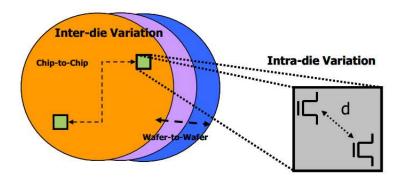

| 2.7  | Inter and Intra-die Variations [2]                                         | 23 |

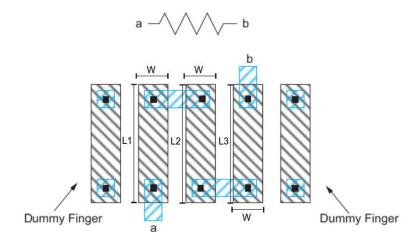

| 2.8  | Resistor geometry [1]                                                      | 25 |

| 2.9  | Transistor corner analysis [3]                                             | 26 |

| 2.10 | Monte-Carlo Analysis [3]                                                   | 27 |

| 2.11 | Hamming Weight table                                                       | 29 |

| 3.1  | APUF tri-state buffer circuit                                              | 30 |

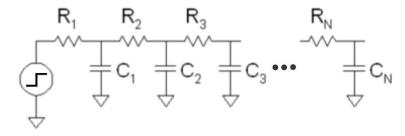

| 3.2  | RC circuit                                                                 |    |

| 3.3  | DFF internal architecture [1]                                              | 34 |

| 3.4  | (a) Unbalanced SR-Latch;(b) Balanced SR-Latch                              | 35 |

| 3.5  | NAND CMOS                                                                  | 35 |

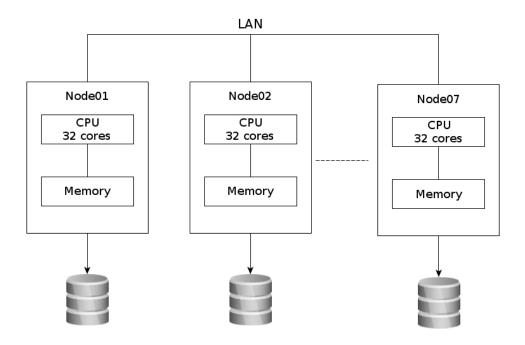

| 4.1  | Cluster de simulação dos experimentos                                      | 37 |

| 4.2  | Single cell characterization circuit                                       | 38 |

| 4.3  | Transient result of the simulation                                         | 38 |

| 4.4  | Standard deviation $(\sigma_g)$ as gate strength increases                 | 39 |

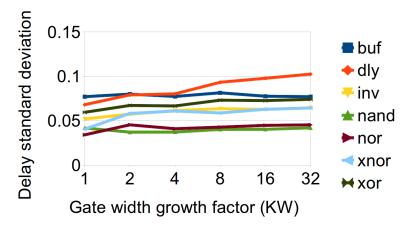

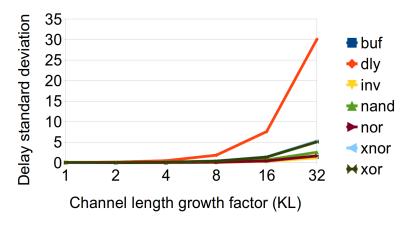

| 4.5  | Gate delay standard deviation $\sigma_g$ s a function of $K_W$ $(K_L = 1)$ | 40 |

| 4.6  | Gate delay standard deviation $\sigma_g$ s a function of $K_L$ $(K_W = 1)$ | 40 |

| 4.7  | Delay variability fast cell                                                | 40 |

| 4.8  | Delay variability slow cell                                                | 41 |

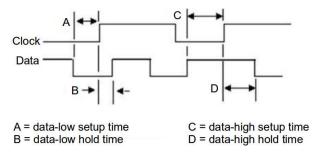

| 4.9  | Setup and Hold times specification for rising-edge-triggered flip-flop     | 42 |

| 4.10 | DFF characterization procedure [2]                                         | 43 |

|      | DFF arbiter characterization circuit                                       |    |

|      | Setup and Hold times specification for SR-Latch                            | 43 |

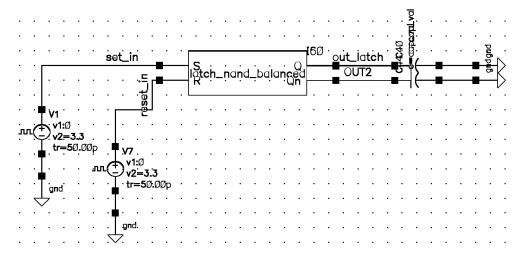

|      | SR-Latch arbiter characterization circuit                                  | 44 |

|      | SR-Latch arbiter characterization - setup time simulation                  |    |

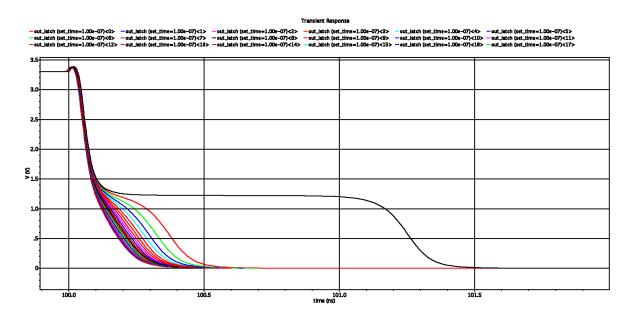

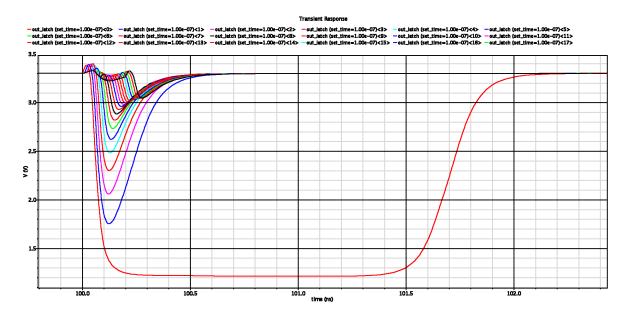

|      | SR-Latch arbiter characterization -hold time simulation                    | 45 |

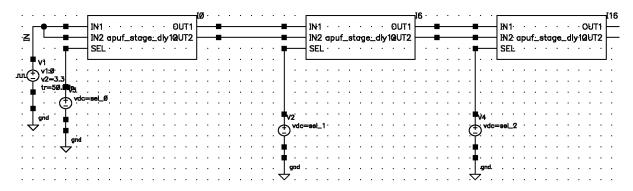

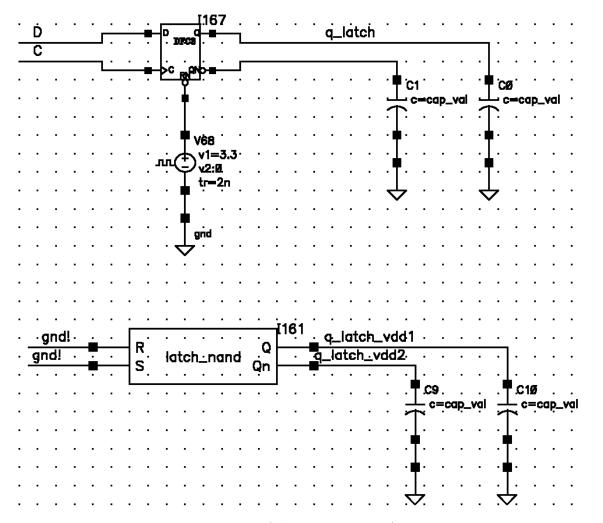

|      | Delay network circuit in ADE                                               | 47 |

|      | Arbiter circuit in ADE                                                     | 47 |

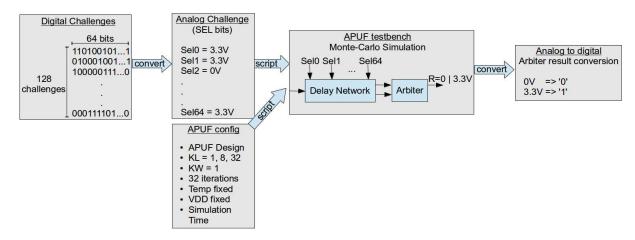

|      | Simulation Framework                                                       | 48 |

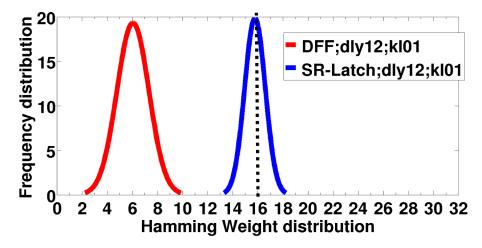

|      | HWD comparison when using DFF and SR-Latch as arbiters                     | 50 |

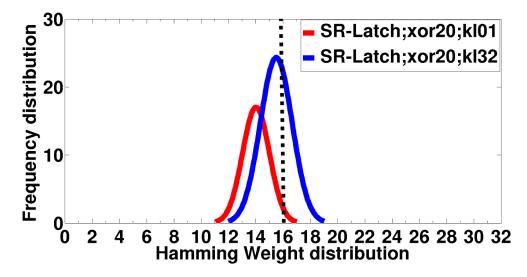

| 4.20 | HWD comparison when using SR-Latch with different drive strength in        |    |

|      | delay network                                                              | 50 |

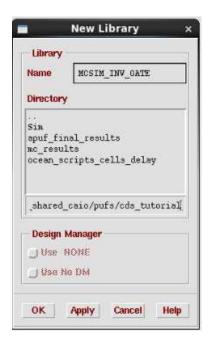

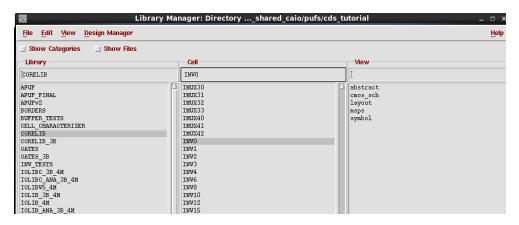

| A.1  | Adding new library                          |

|------|---------------------------------------------|

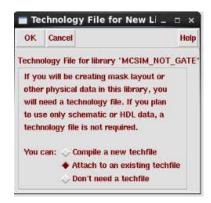

| A.2  | Technology file for new library             |

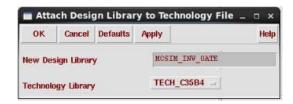

| A.3  | Attach design library to technology file    |

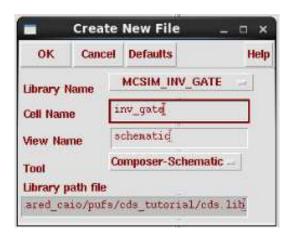

| A.4  | Create new cellview                         |

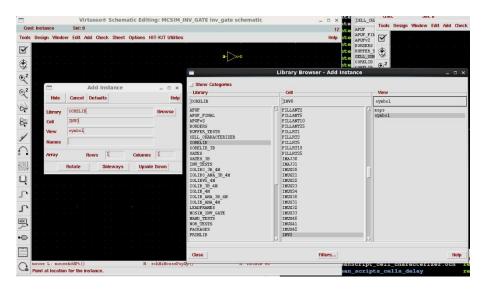

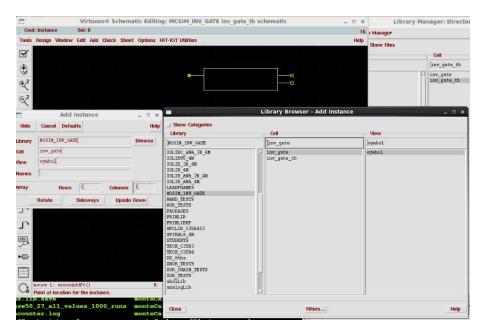

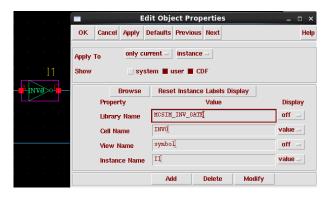

| A.5  | Adding a new instance of inverter gate      |

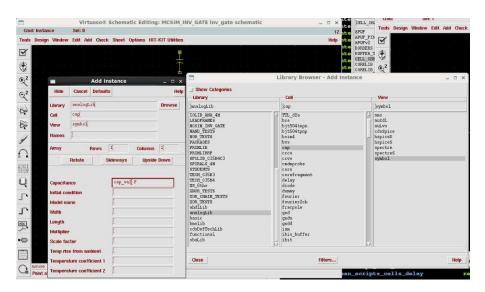

| A.6  | Adding a new instance of capacitor          |

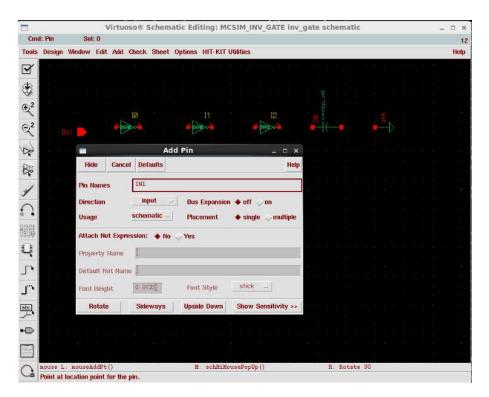

| A.7  | Add pin                                     |

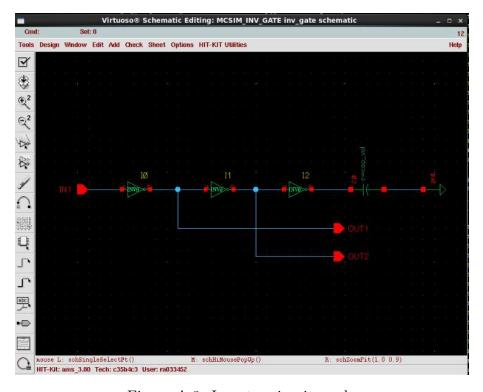

| A.8  | Inverter circuit ready                      |

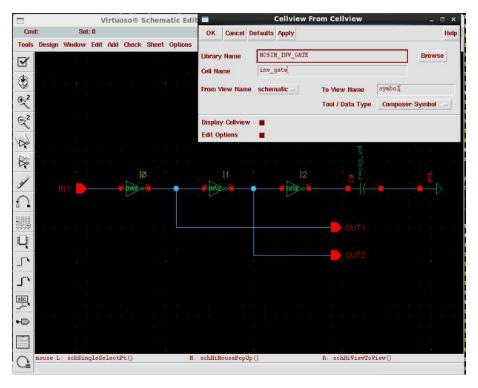

| A.9  | Create symbol from schematic                |

| A.10 | Add new instance of inverter circuit        |

| A.11 | Add vdd source                              |

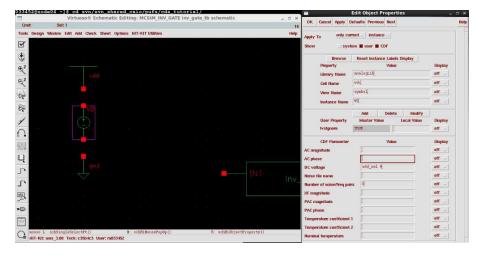

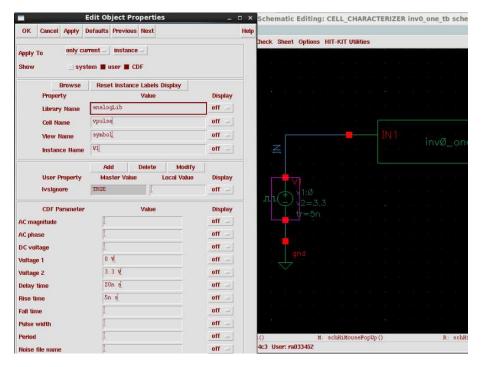

| A.12 | Add vpulse source                           |

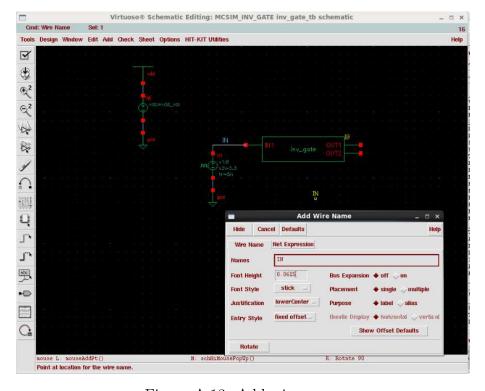

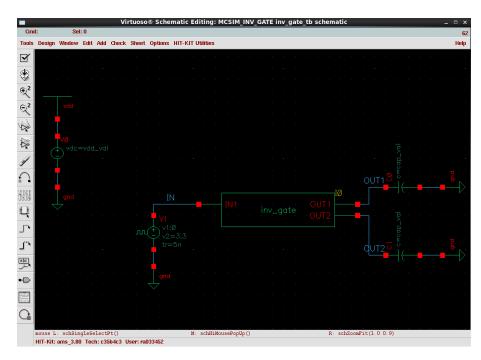

| A.13 | Add wire name                               |

| A.14 | Testbench circuit ready                     |

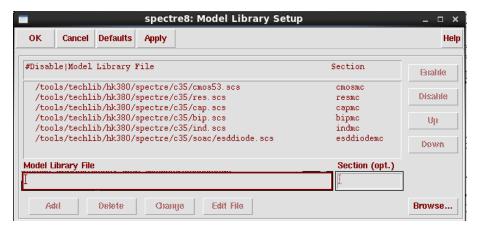

| A.15 | Setup model libraries                       |

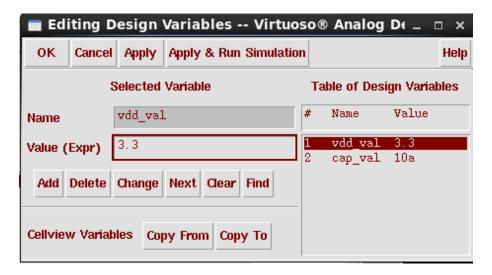

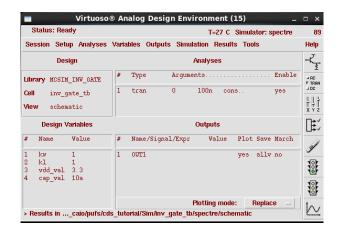

| A.16 | Set simulation variables                    |

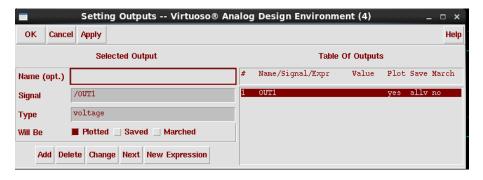

| A.17 | Configure plotted signals                   |

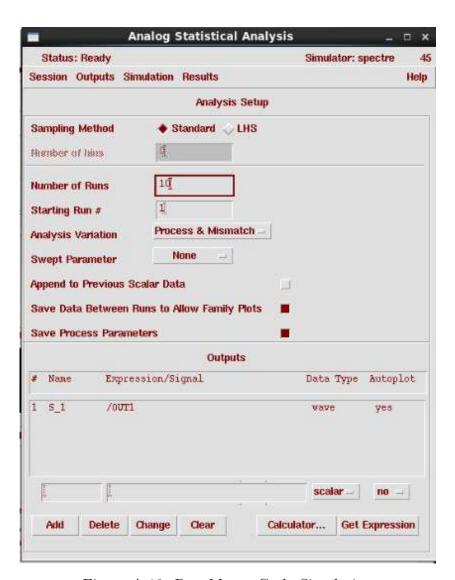

| A.18 | Run Monte-Carlo Simulation                  |

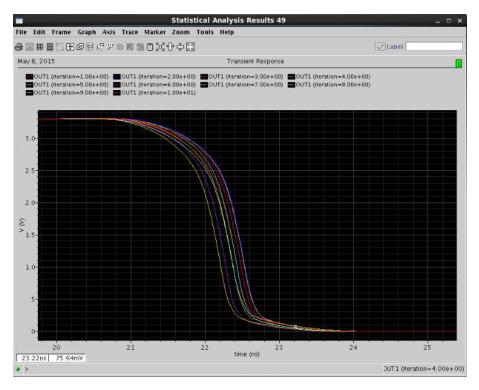

| A.19 | Monte-Carlo result                          |

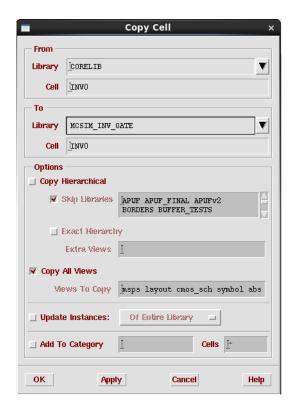

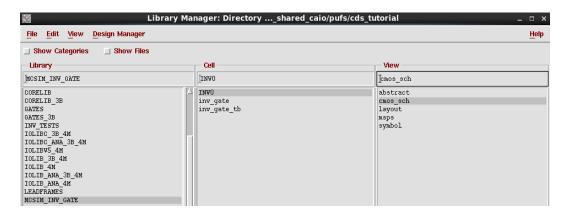

| A.20 | Copy inv cell                               |

| A.21 | Copy inv cell window                        |

| A.22 | Inv cell added to library                   |

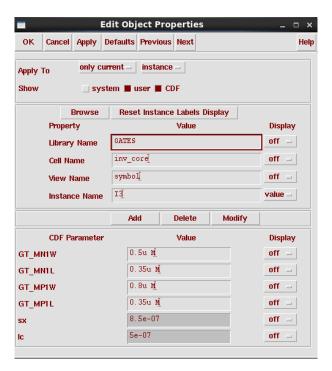

| A.23 | Original inv cell properties                |

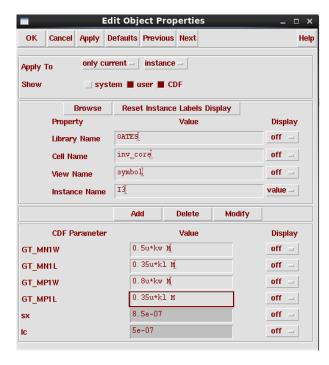

| A.24 | Inv cell properties with $K_L$ and $K_W$    |

| A.25 | Use the modified version of inv cell        |

| A.26 | Define $K_L$ , $K_W$ and run the simulation |

# List of Tables

| 2.1 | CMOS process variation                                                            | 25 |

|-----|-----------------------------------------------------------------------------------|----|

| 2.2 | Resistance according to process variation                                         | 26 |

| 2.3 | Threshold tension of transistors                                                  | 26 |

| 3.1 | Truth tables                                                                      | 34 |

| 4.1 | Average delay and standard deviation $(\sigma_g)$ for combinational library gates | 39 |

| 4.2 | Mean and standard deviation for modified combinational gates                      | 41 |

| 4.3 | Setup or Hold times for the DFF and SR-Latch                                      | 45 |

| 4.4 | Full circuit configurations                                                       | 46 |

| 4.5 |                                                                                   |    |

# Contents

| 1                         | Intr                     | roduction                                                                                                                                                                                        | 15                                                       |

|---------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2                         | Bas 2.1 2.2 2.3 2.4 2.5  | PUF definition 2.1.1 Delay PUF Challenges and responses PUF properties Transistor Geometry and Process Variation Process Variability Simulation 2.5.1 Corner Analysis 2.5.2 Monte-Carlo Analysis | 17 18 20 21 22 23 24 26 28                               |

| _                         |                          |                                                                                                                                                                                                  |                                                          |

| 3                         | 3.1<br>3.2               | Delay network design techniques                                                                                                                                                                  | 30<br>31<br>31<br>32<br>33<br>33                         |

| 4                         | Evr                      |                                                                                                                                                                                                  | 36                                                       |

| 4                         | 4.1<br>4.2<br>4.3<br>4.4 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                             | 36<br>37<br>37<br>38<br>38<br>41<br>42<br>45<br>46<br>49 |

|                           |                          | 4.4.3 Improving HWD using gate sizing                                                                                                                                                            | 50<br>51                                                 |

| 5                         | Con                      | aclusions and Future Work                                                                                                                                                                        | 52                                                       |

| $\mathbf{B}_{\mathbf{i}}$ | bliog                    | graphy                                                                                                                                                                                           | 54                                                       |

| $\mathbf{A}$ | Tute | orial: I | Monte-Carlo Simulation                                                                                      | <b>57</b> |

|--------------|------|----------|-------------------------------------------------------------------------------------------------------------|-----------|

|              | A.1  | Enviro   | nment Setup                                                                                                 | 57        |

|              | A.2  | Monte    | -Carlo Simulation of a 'Inverter' Gate                                                                      | 59        |

|              |      | A.2.1    | Creating new library and cellview                                                                           | 59        |

|              |      | A.2.2    | Circuit Design                                                                                              | 61        |

|              |      |          | Testbench Design                                                                                            |           |

|              |      | A.2.4    | Running the simulation                                                                                      | 64        |

|              | A.3  | Create   | and modify 'L' and 'W' of an inverter cell                                                                  | 70        |

|              | A.4  | Ocean    | $\operatorname{script} \ldots \ldots$ | 73        |

| В            | Tute | orial: I | Monte-Carlo Simulation Framework                                                                            | 77        |

# Chapter 1

### Introduction

Physical Unclonable Functions (PUFs) are circuits designed to exploit the statistical variations of its fabrication process to create a unique device identity. PUFs have been used in the design of cryptographic primitives for a variety of security applications like device authentication [4], key generation [5], remote enabling [6], among others.

Although they can be designed using physical parameters from different domains (optical, magnetic, acoustic, etc.) [7] silicon-based PUFs have become the technology of choice, given the maturity of its manufacturing process and the simplicity and low-cost of the resulting devices. Many silicon-based PUFs have been proposed, which exploit circuit parameter variations like: transistor threshold voltage  $(V_t)$  [8], voltage drop along power lines [9], capacitance layout variations [10], among others. Nevertheless, delay-based PUFs can still result in simple and small designs, the reason why they are the focus of this dissertation.

Delay-based PUFs were first introduced by Gassend et al. [6] and is based in a challenge and response behaviour. Challenge signals are applied to the input of the PUF, starting a race among different circuit paths in a *delay network*. As each path has a distinct delay, due to the statistical distribution of its resistances and capacitances, the response signals arrive at different moments at the end of the circuit paths, and are captured by an *arbiter*, which builds the PUF response output for the specific challenge. Circuit paths can be designed by using a combination of crossbars [6,11] and tri-state buffers [12]. Because of the existence of an Arbiter, we will refer such PUFs as APUFs.

From a security perspective, PUFs have been under strong scrutiny as they can be target of a number of security attacks like: reverse engineering, delay parameter modelling, emulation and statistical modelling, side-channel attacks and machine learning [13–16]. Although there are still concerns about the overall PUF security for some applications domains, like RFID authentication, its simplicity and low-cost are very attractive design features [17]. PUF security rests on the difficulty to extract and model its behaviour as it depends on the variability of the intrinsic physical parameters of the fabrication process. For example, consider two identical PUF circuits. Although they have the exact same circuit layout they can produce different *output* when the same *input* vector is applied. This is due to the fact that PUFs are designed to amplify the small differences in its electrical parameters (resistance, capacitance etc) which result from the statistical variation of its physical parameters during the fabrication process (e.g. diffusion depth,

dopant concentration, wire width, etc.) [18]. As a consequence, by only replicating its circuit layout, an attacker cannot clone a PUF. Moreover, notice also that the delay differences between two PUFs show up only when the circuit is stimulated. Hence any attack to a PUF aiming at capturing this difference will disturb its behavior and thus impact its response.

One of the most important features of a PUF circuit design is its ability to produce very distinct responses in different chips when the same challenge is applied to its input. The more distinct the responses are, the harder for an attacker to model its *challenge-response function* by monitoring its input/output. Hence, it is highly desirable to tailor the design of a PUF aiming at increasing its response variability. Nevertheless, although PUFs have been extensively studied in the literature, not much work has been done in understanding how gate sizing can be used to improve PUF responses. This dissertation uses extensive AMS 350 nm SPICE-based Monte-Carlo simulation to analyze the impact of gate sizing in the delay variability of Arbiter PUFs (APUF). It seeks to answer the following research questions: (1) Which design techniques can be used to increase the challenge-response variability of Arbiter PUFs? (2) And how these techniques can be used to produce well-balanced designs (in physical and statistical terms)?

To answer such questions, this dissertation gives the following contributions: (1) It proposes an approach which combines gate strength and channel length sizing to increase the delay variability of the APUF delay network; (2) It shows that the adoption of symmetric latch designs with reduced setup-time can improve the arbiter ability to detect small differences in the delay of the network paths.

The remainder of this dissertation is organized as follows. Section 2 discusses the APUF designs available in the literature and the workings of a typical APUF. Section 3 makes a thorough analysis on how the statistical delay distribution of APUFs varies as the size of its composing gates change. It also proposes an approach to use gate sizing to increase PUFs challenge-response variability. Section 4 discusses the experimental results that support the proposed approach. Section 5 concludes the work and describes future research.

# Chapter 2

### Basic concepts and related work

This section addresses the basic concepts required to fully understand the work described in this dissertation. It discusses PUF circuits (Section 2.1), challenge and response mechanisms (Section 2.2) and the required properties for a circuit to be considered a PUF (Section 2.3). It resumes the theory involving transistor design and lists the physical / electrical variations that occur during the manufacturing process (Section 2.4). Moreover it discusses the tools to simulate the designed circuits under the aforementioned variations (Section 2.5) and a method used to evaluate the results when comparing the proposed techniques (Section 2.6).

#### 2.1 PUF definition

According to [7], *Physical Unclonable Functions* (PUFs) are circuits that map challenges to responses by exploiting intrinsic characteristics resulting from the fabrication process. They are designed to exploit such intrinsic characteristics, so that the same circuit produces different and unique responses when manufactured in different chips. Circuit responses can be considered an individual chip signature, which can be used for device identification (*device ID*).

There exist two main types of PUFs [7]: electronic and non-electronic. The difference consists in the nature of the components that contributes to the randomness which makes each PUF unique. Electronic components are typically used for the PUF part that performs measurement, processing and storage of the results.

The PUF used during this work belongs to the electronic category. The circuit randomness is based on the propagation time of two signals throw a set of configurable balanced paths, which are affected by variations during the manufacturing process. The path configurations are defined by the challenge input bits, and for each input, one response output bit is generated. Thus, a unique bit response can be generated by applying different challenges and grouping the response bits. The response bits that each chip produces can be used to uniquely identify them, similar as the fingerprint in human beings.

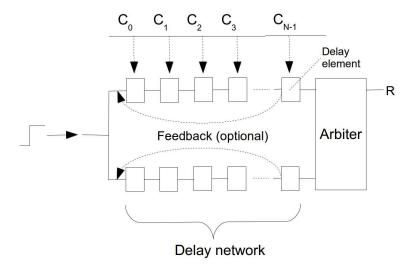

Figure 2.1: Generic delay PUF circuit

#### 2.1.1 Delay PUF

Figure 2.1 shows a general model of delay PUF circuits. The variability of the circuit is attributed to the *delay network*, which exploits the variability of the different circuit paths (defined by the challenge  $C_i$ , i = 0..n - 1) to create a signal race between the paths. In the case of ring oscillator PUFs [4], there exists also a presence of the *feedback* connection. The delay difference detection is performed by an *arbiter*, which uses storage elements (e.g. flip-flops, latches) to sample the output of the stage in order to produce the PUF response.

One of the fundamental requirements of an APUF design is to assure that all paths of the delay stage are exactly the same, i.e. every path from the stage input to its output is designed to have exactly the same nominal delay. Hence, the designer should work to guarantee that every path at each stage is a combination of gates and interconnects that produce the same nominal delay (in terms of static timing analysis). To achieve this goal the designer must have full control not only of the logic design process, but also of the placement and routing of the interconnects. This assures that any delay mismatch between two paths is created only by the variations in the manufacturing process and not by the design.

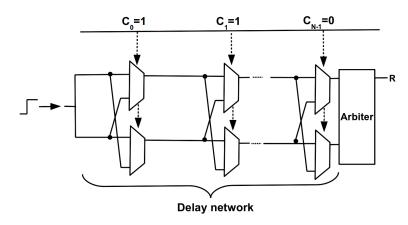

Figure 2.2: APUF mux circuit

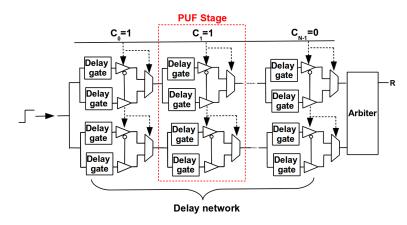

The first APUF design was proposed by Lim et al. (Figure 2.2) [19]. Each stage of the delay network contains a crossbar switch, designed using two multiplexers. Notice that for this circuit, it is difficult to satisfy the aforementioned condition of having the exactly same nominal delay in the delay network, as the cross-connections are always longer than the straight ones. On the other hand, the architecture proposed by Ozturk e.t. all [12] works similarly as the former, but instead of crossing the paths, each signal has an exclusive path, and uses the variation on the delay gates as the source of randomness. It is totally balanced, both in terms of gates and interconnections, as shown in Figures 2.3 and 2.4. For this reason, the following work used Ozturk's architecture for basis.

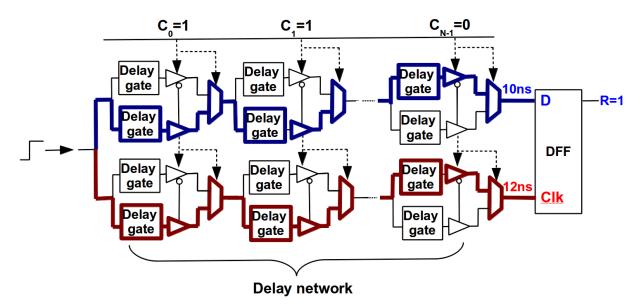

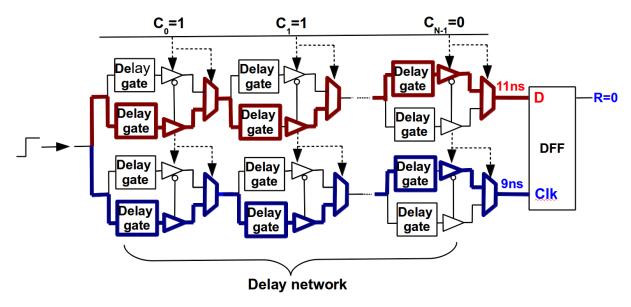

Ozturk's circuit works as follows: first, one has to set up the paths in which the input signal will flow through the top and bottom paths. These paths are selected according to the applied challenge bits (Section 2.2)  $(C_0, C_1, C_{N-1})$ . Next, a step signal is applied at the input, which starts the race between the paths. Given that the circuit is well-balanced, the delay mismatch between the paths is exclusively due to the variations in the manufacturing process (Section 2.5). Figure 2.3 presents the behavior of a *chip 1* instance, in which the top path is faster than the bottom path. In this example, the top signal arrives in port 'Data' of the flip-flop after 10ns while the bottom signal arrives in 'Clock' port after 12ns, causing the registered value, named response (R), to be '1'. In opposite, chip 2 (Figure 2.4) presents a different behavior for the same input challenge but this time with the signal arriving earlier in 'clock' port, causing the response to be '0'. The APUF's arbiter, in Figure 2.2, is a single flip-flop which captures the race between the two racing signals at inputs D and Clk. The order in which the signals arrive at D and Clk will define if the response (R) to the challenge is "0" or "1".

Figure 2.3: Delay PUF circuit example (Chip 1)

Figure 2.4: Delay PUF circuit example (Chip 2)

#### 2.2 Challenges and responses

Consider again the APUF of Figure 2.2. It receives an input challenge vector  $C_i$ , i = 0...N - 1 of N bits and generates a response bit R. Each stage of the APUF is a crossbar switch that selects which path the two racing signals will take at that stage. Crossbar switches can be designed using two multiplexers (MUXs) which take the challenge bit  $(C_i)$  as selectors. When  $C_i = 0$  ( $C_i = 1$ ) the crossbar operation is pass through (crossed). Remember that by construction the two crossbar paths should have the exact same static delay. The race starts at the first stage (i = 0) in which the two crossbar inputs are tied together and applied the same step signal. For example, in Figure 2.2 racing signals take the crossed path in the first and second stages ( $C_{0,1} = 1$ ) and the pass through path in the last stage ( $C_{N-1} = 0$ ).

The pair formed by an applied challenge and its respective response is named challengeresponse pair (CRP). By applying multiples challenges and gathering the responses of the same chip instance, one builds the CRP behaviour of the instance. The CRP behaviour is the information that can be used to uniquely authenticate each device. The length of a CRP depends on the number of instances one intends to authenticate [19] and the resistance to brute force (trial and error) attacks [20]. Figure 2.5 demonstrates the usage of CRP as device authentication. The procedure, performed when the chips are already manufactured and encapsulated, is divided in two phases: chip characterization and chip authentication. The former is performed in a controlled ambient under safety requirements measures in place. A defined amount of chips are stimulated with the same collection of challenge bits, and their respective responses are stored in a common database, creating the CRP of each chip. For instance, the CRP of chip 1 is called the Database for chip 1. The second phase occurs when the chip is assembled in an unsafe environment, being subject to various types of security attacks. The goal is to authenticate the device by comparing their current responses with the ones stored in its database, when the same challenges are applied. To avoid man-in-the-middle attacks [21], each CRP should be used only once, demanding for the database to have enough entries for the total number of authentication operations of each chip.

Figure 2.5: PUF for authentication procedure

#### 2.3 PUF properties

This section describes the most important properties for a device to be considered a PUF based on the formal definition published by Maes et al in [7]. For the properties, consider the notation  $\Pi:\chi\to\Upsilon:\Pi(x)=y$  as the representation of the challenge-response function of a determined PUF.  $\Pi$  represents the PUF function,  $\chi$  the challenge set,  $\Upsilon$  the response set, x a challenge instance from set  $\chi$  and y a response instance from set  $\Upsilon$ . The following PUF properties can then be defined based on this function. A PUF can be said to be:

- 1. "Evaluatable: given  $\Pi$  and x, it is easy to evaluate  $y = \Pi(x)$ ". By easy, it means that the evaluation can be performed in polynomial time and effort, inducing little overhead on the overall system.

- 2. "Unique:  $\Pi(x)$  contains some information about the identity of the physical entity embedding  $\Pi$ ." By exploring this property using a well-defined set or population of PUF instantiations, at every challenge applied, the population is partitioned according to the response. Consecutive responses allow for smaller and smaller partitions until, optimally, a partition with a single PUF instantiation remains. In this case, the considered set of *challenge-response pairs* (CRPs) is sufficient to uniquely identify the PUF in the population. According to the population size, the aforementioned procedure might or might not be possible.

- 3. Reproducible (or Robust): For every value  $y = \Pi(x)$ ,  $y = y_0$  is the central value in a Gaussian probability distribution, and  $y \neq y_0$  is a small variation around  $y_0$ . For this variation, error correction code algorithms (ECC) can be applied to recover

- $y_0$ . When this property is not present, it is possible that, for the same challenge, different results can be obtained. This property could be used to build true random number generators (TRNGs).

- 4. "Unclonable: given  $\Pi$ , it is hard to construct a procedure  $\Gamma \neq \Pi$  such that  $\forall x \in \chi : \Gamma(x) \approx \Pi(x)$  up to a small error." This is the core property of a PUF, which guarantees its usability as an identification device. For a PUF to be truly unclonable, it must be resistant to both the physical and mathematical approaches. Physical resistance is defined as the difficulty in creating a PUF  $\Gamma \neq \Pi$  (embedded in physically distinct entities) such that  $\forall x :_{\Gamma} (x) \approx \Pi(x)$ . Note that the hardness of producing a physical clone holds also for the manufacturer of the original PUF, reason why it is also classified as manufacturer resistance. The Mathematical resistance is applied if it is difficult to create an (abstract) mathematical procedure  $f_{\Gamma}(x)$  such that  $\forall x : f_{\Gamma}(x) \approx \Pi(x)$ .

- 5. "Unpredictable: given only a set  $Q = (xi, yi = \Pi(x_i)), i = 1...q$ , it is hard to predict  $y_c \approx \Pi(x_c)$  up to a small error, for  $x_c$  a random challenge, such that  $(x_c, .) \notin Q$ ." If one can correctly predict the response of a given PUF for a random challenge by analyzing its previous CRPs, then it is possible to build a mathematical function with the same behaviour, thus breaking the previous property of unclonability.

- 6. "One-way: given only y and  $\Pi$ , it is hard to find  $x \in \chi$  such that  $\Pi(x) = y$ ." This is the same property commonly found in cryptographic hash functions. By knowing function  $\Pi$  (e.g. analyzing circuit layout) and the generated response y, it is infeasible to generate the input challenge x.

- 7. "Tamper evident: altering the physical entity embedding  $\Pi$  transforms  $\Pi \to \Pi'$  such that with high probability  $\exists x \in \chi : \Pi(x) \neq \Pi'(x)$  not even up to a small error." This property guarantees that if an attacker has physical access to the device, any attempt to monitor the internal paths will change the PUF properties, and thus, its behaviour.

#### 2.4 Transistor Geometry and Process Variation

Figure 2.6: Transistor geometry [1]

Figure 2.6 shows a simplified model of a MOS (Metal-Oxide Semiconductor) geometry transistor [1] in which the source and drain are represented by the n-diffusion regions, and the gate is referenced by " $SIO_2$  Gate Oxide" arrow. The analog designer can have control in only two parameters related to the transistors geometry: channel length (L) and channel width (W). After a transistor is manufactured, its behaviour can vary at a function of different classes of process variations, as described in Boning, D.S and Nassif, S. [22]. From all the categories listed [22], the transistor is specially sensitive to Device Geometry Variations, which is divided in two sets:

**Film thickness variations:** Affects the gate oxide thickness. It is a critical variation but can be controlled within the same die. It has more impact between wafers, dies and lots.

Lateral dimension variations: Affects transistors lengths and widths. It is due to three main sources: photo-lithography proximity effect; mask, lens or photo system deviations; plasma etch dependencies.

#### 2.5 Process Variability Simulation

With the sharp degree in feature length, process variability of integrated circuits has become the target of several research projects. As the process geometry is continuously shrinking, the ability to control all the parameters are becoming more and more difficult, and its impact in the circuit behaviour increasing proportionally.

Process variability can be classified in two groups: *inter-die* and *intra-die* variation. The *inter-die* variation occurs in different dies, such that for the same circuit, there are small differences between the dies of the same wafer, from different wafers and from different wafer lots. In the case of *intra-die*, the variations occur between different gates on the same die, and are also named *local variations* (Figure 2.7).

Figure 2.7: Inter and Intra-die Variations [2]

In digital design, process variation delay effects are modelled using *static timing analy-sis* (STA), based on three conditions: *worst case*, *typical case* and *best case*. The drawback of using this approach comes from the adoption of deterministic values, in which no statistical variation is present. Although this model provides good performance estimates

for *inter-dies* variation, it cannot precisely model the statistical variations that occur for within the die.

For the design of delay based PUFs, it is mandatory that the used simulation tool can model as precise as possible the aforementioned variations. These variations need to be applied for each gate of the circuit layout, so that each of them presents a slightly different delay. The combination of the delay uncertainty at each gate is the source of entropy of the circuit. To simulate this scenario, two methods are commonly available: *Corner Analysis* and *Monte-Carlo Analysis*. The former, explained in Section 2.5.1, uses discrete conditions while the later, explained in Section 2.5.2, is based on statistical distributions.

Instead of performing the analysis using simulation tools, another option for this study would be the usage of FPGAs. We have discarded this possibility after our own analysis and previous works [23–25] enumerates several challenges to obtain a good performance under this environment: 1) regular cell placement to achieve symmetric PUF layout. 2) physical constraints on the FPGA fabric that forbids the designer to create complete symmetric routing paths. 3) limited number of gate types already manufactured on the FPGA, restricting the usage of geometry change technique in delay network (Section 3.1.2), and providing no guarantee if the arbiter circuit (SR-latch or DFF) is well-balanced (Section 3.2).

#### 2.5.1 Corner Analysis

Corner analysis simulation is based on the fact that for each controlled parameter, the value of the electrical parameter in real silicon must lie between a minimum (MIN) and a maximum (MAX) quantity. This means that if the simulation process cover the MIN and MAX values of each parameter and the circuit still meets the required specification, then one can assume that the manufactured silicon will meet the specification too. The model files can be classified as follow:

- Typical Mean (TM): Uses the typical value of each parameter.

- Worst Speed (WS): Uses the worst value of each parameter, making the circuit slow.

- Worst Power (WP): Uses the best value of each parameter, making the circuit fast, consequently power hungry.

- Worst Zero (WZ): Consider differences between NMOS and PMOS regions, making the circuit slow for 'zero' transitions and fast for 'one' transitions.

- Worst One (WZ): Consider differences between NMOS and PMOS regions, making the circuit slow for 'one' transitions and fast for 'zero' transitions.

For each process technology, the nominal value and variation range of each parameter is intensively monitored by the foundry, based on already manufactured samples. These data are provided to the designer via the so called technology library, in a format that can be loaded by the simulation tool.

As an example of corner analysis, consider the following example using a single resistor (Figure 2.8). The length L is the sum L = L1 + L2 + L3 and its nominal values described below:

- $W = 2\mu m$

- $L = 400 \mu m$

- $R = 267k\Omega$

Figure 2.8: Resistor geometry [1]

For the process technology, consider the parameters sheet resistance  $R_{sh}$  and effective width when nominal W is set to 0.8 ( $W_{eff|0.8}$ ). Range values for these parameters are shown in Table 2.1.

| Ī |               | Min | Тур | Max |               |

|---|---------------|-----|-----|-----|---------------|

|   | $R_{sh}$      | 1,0 | 1,2 | 1,4 | $k\Omega/Sq.$ |

| ľ | $W_{eff 0.8}$ | 0.5 | 0.6 | 0.7 | $\mu m$       |

Table 2.1: CMOS process variation

To calculate the impact of the process variation in the behaviour of each element, the technology library also contains equation models for the electrical characteristics of the components. To illustrate this procedure, consider the example of a resistor. Resistor's effective resistance ( $R_{eff}$ ) is based on Eq. 2.1, being  $R_{sh}$  the sheet resistance, l and  $\Delta l$  respectively the length and length variation, and w and  $\Delta w$  respectively the width and width variation.

$$R_{eff} = R_{SH} * \frac{l - \Delta l}{w - \Delta w} \tag{2.1}$$

Table 2.2 shows the computation of the resistance according to the variation parameters. From this example, one can see that by using the corner analysis, the effective resistance can vary from  $210k\Omega$  to  $329k\Omega$ .

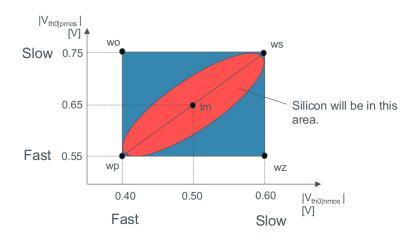

The same procedure described above is also applicable to transistor models. For the transistor characterization shown in Table 2.3, the corner based simulation is performed according to Figure 2.9. This analysis is often too pessimistic, because it does not consider the parameter correlations. The ellipse region in Figure 2.9 delimits the effectively

|    | $R_{sh}$          | $\Delta w$ | $\Delta l$ | $R_{\it eff}$ |

|----|-------------------|------------|------------|---------------|

| WP | $1,0k\Omega/Sq.$  | $0,1\mu m$ | $0,0\mu m$ | $210k\Omega$  |

| TM | $1, 2k\Omega/Sq.$ |            |            |               |

| WS | $1,4k\Omega/Sq.$  | $0,3\mu m$ | $0,0\mu m$ | $329k\Omega$  |

Table 2.2: Resistance according to process variation

manufactured silicon characteristics. Another drawback of this type of simulation is that it does not consider the variations that occurs in a single chip between gates of the same type. For them, the same equation, conditions and variation range are applied.

|                | Min   | Тур   | Max   |   |

|----------------|-------|-------|-------|---|

| $V_{th0 nmos}$ | 0,4   | 0,5   | 0,6   | V |

| $V_{th0 pmos}$ | -0,55 | -0,65 | -0,75 | V |

Table 2.3: Threshold tension of transistors

Figure 2.9: Transistor corner analysis [3]

#### 2.5.2 Monte-Carlo Analysis

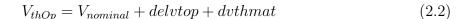

Researchers have shown that process variations cannot be avoided in silicon manufacturing process [26]. These variations are mostly related to statistical variations of the physical parameters of the materials (e.g. dopant density), equipment (e.g. lithography precision) and process (e.g. lateral diffusion depth) used in fabrication. As a result, the same transistor can show different performance due to variations in its final geometry (e.g.  $Channel\ Length\ (L)$ ) and electrical parameters (e.g.  $RC\ delay$ ). In order to capture the impact of process variation in performance, statistical simulation models are applied, which can be used by commercial SPICE simulators (e.g. Cadence SPECTRE) to perform Monte-Carlo simulation of delay variability.

When using Monte-Carlo simulation, for each run every parameter is calculated randomly according to the distribution model provided by the foundry. Commonly, lot-to-lot,

wafer-to-wafer and chip-to-chip variations are classified as "process variation", a single pseudo-random component from the perspective of individual chips, and modelled by an uniform distribution. Process variation is supposed to be similar for all transistors on the same chip. On the other hand, in-chip variations are decomposed into across-chip systematic and local random variations, which are modelled by independent Gaussian distributions.

As an example of Monte-Carlo analysis, consider a CMOS inverter circuit. For each transistor, the threshold voltage  $(V_{thOp})$  is calculated based on Eq. 2.2, that is composed of three components:  $V_{nominal}$  corresponds to the nominal threshold voltage of the transistor, delvtop represents the process variation parameters and Dvthmat corresponds to the mismatch variations. Figure 2.10 shows the region in which Monte-Carlo simulation estimates the parameters, and the density of probability of each region, known as Standard Deviation (or  $\sigma$  variation).

Figure 2.10: Monte-Carlo Analysis [3]

As a consequence of the variation in threshold and resistance, manufacturing processes affects the final delay of a designed cell. Ideally, the *delay network* circuit of Figure 2.1 should produce the same delay for any path created from the first to the last stage. As a consequence, the two racing paths should arrive at the same instant of time at ports D and Clk. However, due to the statistical variation of the fabrication process each of the gates that compose the paths have slightly different delays. The cumulative delay through all the stages will randomly change the arrival times of D and Clk, producing a desirable random response bit R. One possible drawback occurs when the arrival time of D and Clk do not respect the setup/hold time of the arbiter. In this case, metastability [1] can occur and the sample response R will be unpredictable. This is an undesirable feature, since the APUF should reproduce the same response when the same challenge in applied (Reproducible property - Section 2.3).

Given that the Monte-Carlo simulation offers a more realistic condition in terms of manufactured silicon chips, the rest of this work was performed using this kind of simulation.

#### 2.6 PUF evaluation methodology

To apply PUF circuits in security solutions, its responses need to be reliably reproducible (robust) and also, unpredictable. A PUF is classified as robust when it generates similar responses for the same challenge applied several times, even under different operating conditions (temperature, supply voltage, noise level). The robustness of PUFs can be measured by mean of its bit error rate (Eq. 2.3), when compares the current response bitstring versus the bitstring obtained during the characterization process. The *hamming distance* (HD) between two bitstrings, is the number of bits that are different between each of them, and  $|R_{ref}|$  is the length of the reference bitstring.

$$BER = \frac{HD(R_i, R_{ref})}{|R_{ref}|} \tag{2.3}$$

The unpredictability property is necessary to guarantee that an attacker cannot create a physical or mathematical module capable of correctly computing the response of an unknown challenge, from the knowledge of the previous responses of a given PUF. To evaluate if PUFs responses are biased, one would calculate the  $Hamming\ Weight\ Distribution\ (HWD)$  of its output and to verify the independence between PUFs instances, their  $Hamming\ Distance\ (HD)\ [16]$ .

In this work, the experiments are performed using Spice-based simulations with deterministic models, which restrict the number of PUF samples and challenges due to the long simulation time and the deterministic results. As the robustness and independence evaluations (using HD) requires several samples and CRPs, these analysis are part of future work, when the PUF ASIC samples will be available. The focus of this work is to reduce the biasing in PUF responses, i.e, for the same challenge applied in different chips, there should be a balance between response bits '0'and '1', and thus it uses the *Hamming Weight* to evaluate the results.

Being n number of individuals and m the bitstring length, Hamming Weight (HW) [16] of a bitstring  $X_i$ , i = 0...n - 1 is the number of non-zero bits of  $X_i$ , i.e.  $HW(X_i) = \sum_{j=0}^{j=m} b_{ij}$ , where  $b_{ij}$  is the value of bit j in the string  $X_i$ . The Hamming Weight Distribution (HWD) is an histogram which measures the frequency distribution of  $HW(X_i)$  for all strings  $X_i$ , i = 0...n - 1.

This measurement procedure is illustrated in the following example. In Figure 2.11(a), the table summarizes the responses obtained for each device (chip[1..5]) when different challenges (C[1..6]) are applied. The 'HW' row contains the sum of the responses obtained for each challenge, which is used to plot the HWD. Column 'C1' shows an example of biased '0' result, when every chip responded with '0'. Column 'C2' contains the behaviour when the result is biased towards '1'. Figure 2.11(b) shows the HWD of the particular example. Note that the graph contains a Gaussian distribution centered around '2'.

Ideally, the *HWD* of an APUF response should produce a Gaussian distribution [16] centered around half the number of chips driven by the same challenge ('2.5' in the above example). In such situation the APUF response is well balanced, i.e. the circuit efficiently exploits the process fabrication variability in such a way that the responses have no biasing towards '1's or '0's, which could eventually be exploited by an attacker. The more the

Histogram C1 C2 C3 C4 C5 C6 1.5 HWD example chip 1 0 1 0 1 0 0 Frequency 1 0 1 1 chip 2 0 1 0 0 1 0 1 0 1 chip 3 0 0.5 1 0 0 chip 4 0 0 1 1 1 chip 5 0 0 0 2 2,5 PUF response distribution (6 challenges) (a) (b)

HWD of a PUF approaches this scenario the better the PUF is.

Figure 2.11: Hamming Weight table

Although APUFs seem to represent a useful class of PUFs, it could become the target of reversing engineer modeling attacks [13]. Some techniques have been proposed to address this shortcoming, by obfuscating the PUF output, like arbiter designs based on an XOR array and feed forward arbiters [13]. Nevertheless, there are still questions concerning its resistance to such attacks [27]. The focus of this work is in using design techniques to improve the response variability of PUFs. Design techniques to improve the security of APUFs are not covered in this dissertation.

After describing the theory used in this work, the next chapters present a set of new design techniques for APUF designs and evaluate its performance focusing on answering the research questions presented in Section 1.

### Chapter 3

# Techniques to Improve Delay Variability

There are a number of ways to design an APUF delay stage. In [6], Gassend et al. uses a chain of cross-bar switches, built using muxes or tri-state gates, where the behaviour of each stage is defined by a bit of the challenge (Figure 2.2). Other types of delay-based PUFs are ring oscillators [4] and glitches [28]. Each such designs have their own advantages and drawbacks, but all of them could benefit from the gate sizing techniques proposed in this work. Hence, for the sake of simplicity, and without lacking generality, we have selected Ozturk's APUF [12] as the baseline design to discuss the techniques proposed herein.

In Ozturk's architecture, the delay paths at each stage (highlighted in Figure 3.1) are exclusive, i.e. each signal flows through its own path that contains tri-state buffers and delay gates. In order to avoid output spikes when both tri-state buffers are changing states (enabled to high-impedance), a MUX is also used at each path. The tri-state APUF is a good vehicle to analyze how gate sizing affects stage variability, given that it is a fully-balanced architecture (gates and net lengths) and enables the designer to easily change the delay gate type and configuration.

Figure 3.1: APUF tri-state buffer circuit

As described in the previous section, the APUF is a circuit which seeks to exploit, as much as possible, the variability of the fabrication process to create a physical unclonable

function. The goal with this is that two identically designed APUFs could produce a different sequence of responses when the same sequence of challenges is applied.

Given that an APUF architecture is composed of two modules, a delay network and an arbiter, the designer should develop techniques which: (a) increase the delay variability of the delay network (Section 3.1); and (b) improve the ability of the arbiter to detect any small difference in the delay of the network paths which arrive at its inputs (Section 3.2). By doing so, the designer will contribute to increase the variability of the output response of the APUF. Notice that requirement (a) is an undesirable feature in a typical circuit design methodology. This work proposes a novel set of techniques to address these two goals. Overall, the experimental results using such techniques (Section 4) reveal that slow delay networks and fast arbiters tend to produce better APUF designs.

#### 3.1 Delay network design techniques

Given that the path delay of an APUF network should expose the delay variations resulting from the fabrication process, the designer should focus in developing techniques that could expose, as much as possible, the intrinsic electrical variabilities. There are some potential ways in which a designer can achieve that, as described in Section 3.1.3 and Section 3.1.2. Section 3.1.1 contains a simplified model of transistor delay, used as a base to develop the design techniques. In this work the connection delay was not considered, focusing exclusively on the gates.

#### 3.1.1 Simplified model of transistor delay

#### Transistor delay model

Figure 3.2: RC circuit

To model the impact of L, W and its variations in the transistor delay ( $\tau$ ) [1], consider that a circuit can be represented as an RC tree (circuit with no loops). The tree's root is the voltage source and the leaves are the capacitors at the end of the branches (Figure 3.2). The circuit delay can be estimated by *Elmore delay model* [1] as shown in Eq. 3.1. The resistance R is defined by Eq. 3.2 and the capacitance over the area ( $C_a$ ) by Eq. 3.3.

$$\tau \propto [R * C] \tag{3.1}$$

$$R \propto \left[\frac{L}{W}\right] \tag{3.2}$$

$$C_a \propto [C_{ox} * L * W] \tag{3.3}$$

By replacing Eq. 3.2 and Eq. 3.3 into Eq. 3.1, the circuit delay is described as shown in Eq. 3.4. Notice there that the delay is directly affected by L, but not by W.

$$\tau \propto [R * C_a] = [R * \frac{L}{W}] * [C_{ox} * L * W] = R * L^2 * C_{ox}$$

(3.4)

The analysis below describes the impact of the process variation in each one of these delay parameters.

#### Transistor delay variation due to manufacturing process

To model a relative error, we consider a simple average error estimate, for example in equation z = x \* y, the error is expressed as shown in Eq. 3.5.

$$\frac{\Delta z}{z} = \frac{\Delta x}{x} + \frac{\Delta y}{y} \tag{3.5}$$

Hence, from equation Eq. 3.4, the relative error is modelled by equation Eq. 3.6.

$$\frac{\Delta \tau}{\tau} = \frac{\Delta R}{R} + \frac{\Delta L}{L} + \frac{\Delta L}{L} + \frac{\Delta C_a}{C_a}$$

$$\Delta \tau = \left(\frac{\Delta R}{R} + 2 * \frac{\Delta L}{L} + \frac{\Delta C_a}{C_a}\right) * \left(R * L^2 * C_a\right)$$

$$\Delta \tau = \Delta R * L^2 * C + \Delta C_a * R * L^2 + 2\Delta L * R * L * C$$

(3.6)

Given that the variation of R and  $C_a$  are very small within the same die [29], the simplified delay equation can be modelled as in Eq. 3.7 below.

$$\Delta \tau = 2\Delta L * R * L * C \tag{3.7}$$

Therefore, in order to increase the delay variability of the transistor, the designer should increase the transistor's length given that the other parameters in Eq. 3.7 are not under his/her control.

#### 3.1.2 Gate sizing

It is well-known that variations in the manufacturing process can impact the effective transistor geometries L and W. For example, mask variation and deposition fluctuations can create narrower or overstretched polysilicon. Moreover, sources and drains tend to diffuse laterally under the gate, producing a shorter effective channel length ( $L_{eff}$ ). In [22],

Boning et al. show that  $L_{eff}$  has the largest impact in the gate variability. Based on this and the delay model described in Section 3.1.1, we expect that any change in transistor's W barely affect the gate delay standard deviation. On the other hand, by increasing the size of L, the delay and the standard deviation of the gate could result in have a considerable increase.

It is important to define the difference between variability and  $delay \ variability$  when comparing the techniques on combinational gates. The variability is a function of the models provided by the foundry about the fabrication process for several parameter, which overall can be modelled in terms of  $process \ variation$  (variation between chips, wafers, lots), and mismatch (intra-chip variability). These variations are technology-dependent and are constant for every variation of  $L_{eff}$ . On the other hand,  $delay \ variability$  is a consequence of the manufacturing process, gate strength, and layout geometries. So, for the same process variation model, we expect the delay variability of the original geometry cell to be smaller when compared to the scaled in L versions.

The experiments related to gate sizing are described in Section 4.2.3.

#### 3.1.3 Gate drive strength

Focusing on studying if the delay variability of the delay network varies accord to gate drive strength, we studied the behaviour of the combinational library cells. From [30], one can see that cells with high drive strength tend to produce fast rising and falling output slope. Assuming that slow transitions of output slopes produce higher output delay mean, we expected to see that the variation over the delay mean also increases. Thus, in theory the best candidates to increase delay variability are the combinational gates with weak drive strength. From them, it is also necessary to analyze which gate type/drive strength maximizes the gate delay standard deviation ( $\sigma_q$ ).

Experiments to evaluate that are described in Section 4.2.2.

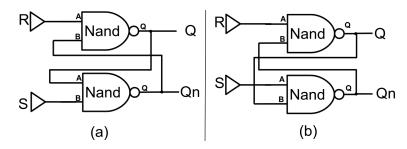

#### 3.2 Arbiter design techniques

As described in Section 1, APUF arbiters are designed using storage elements, to capture the path delay differences resulting from the fabrication process variability. The racing condition on the two signals of the delay network, shown in Figure 3.1, starts with logic value '0' and ends with logic value '1' after applying a step signal. Therefore, an arbiter candidate needs to be either rising-edge triggered, or level-triggered with the extra requirement of keeping the stored value when both signals are '1'. From the aforementioned conditions, two possible arbiter candidates are the *D Flip-flop* (*DFF*) as proposed by Gassend et al. [6] or the NAND SR-Latch, suggested by Lang et al [31]. Their respective truth tables are shown in Table 3.1.

The arbiter element is used to record which of the racing edges arrived first, and quantize it in a digital value. Based on Figure 2.2, the racing signals are respectively connected to ports CLK and D of a (DFF). The value to be stored in the arbiter depends on the relative delay of the signals, being '1' when it arrives first in D, and '0' otherwise. In order to guarantee that the delay difference on the two paths at the inputs of an

Table 3.1: Truth tables

(a) SR NAND Latch

| $\overline{S}$ | $\overline{R}$ | Action      |

|----------------|----------------|-------------|

| 0              | 0              | not allowed |

| 0              | 1              | Q = 1       |

| 1              | 0              | Q = 0       |

| 1              | 1              | No Change   |

(b) D flip-flop

| Clock       | D | $Q_{next}$ |

|-------------|---|------------|

| Rising Edge | 0 | 0          |

| Rising Edge | 1 | 1          |

| Non-Rising  | X | Q          |

arbiter is due only to the fabrication process, the designer must make sure that the two signals being compared go through similar (topologically and electrically) paths within the arbiter.

#### Arbiter logic paths

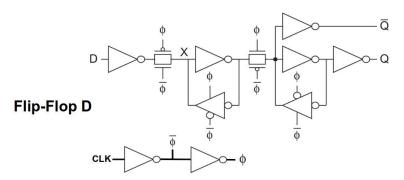

All internal logic paths of an arbiter, starting at its inputs to its output, should have the exact same delay. If there exists a tendency (bias) towards a certain value in the arbiter across many PUF instances, uniqueness will be reduced [4]. A careful analysis in the logic design of a typical CMOS DFF [1], shown in Figure 3.3, reveal that its internal paths are logically unbalanced and thus the path delays D-to-Q and CLK-to-Q are different. As the DFF inputs D and Clk have different functions, it is expected that they will be unbalanced. Therefore, by using a DFF as an APUF arbiter one cannot assure an unbiased evaluation of the delay differences of the paths arriving at its inputs, as required. Contrary to the DFF, the SR-Latch is a symmetric device (Figure 3.4b), and all its paths from input to output have the exact same delay [1], a required feature for correct APUF arbiter.

Figure 3.3: DFF internal architecture [1]

The architecture of a typical SR-LATCH, shown in Figure 3.4a, at first glance seems to be balanced, but a deeper analysis reveals that the feedback connections are not connected to the exact same NAND input ports. For this reason we propose a slightly different design in the SR-LATCH architecture, that changes the feedback connections to the same input ports (Figure 3.4b).

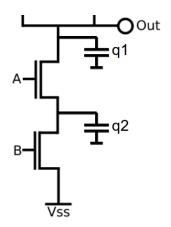

This scenario is better understood from the CMOS perspective. Considering the pull down NMOS transistors of the NAND gate (Figure 3.5), there are two parasitic capacitances connected in series, named  $q_1$  and  $q_2$ . Depending on the order in which the input

Figure 3.4: (a) Unbalanced SR-Latch; (b) Balanced SR-Latch

signals arrive, the capacitance discharge sequence is different. When input B changes to '1' before A, capacitance  $q_2$  discharges while  $q_1$  is still charging. Later when A arrives and changes to '1' it is only necessary to discharge  $q_1$ . The second scenario occurs when input B changes to '1' after A changes. In this case, only when B=1 arrives capacitances are discharged through transistor B which drains a charge of  $q_1 + q_2$ , thus making the output signal slower.

Figure 3.5: NAND CMOS

The impact of this design decision on HWD is confirmed by the experiments in Section 4.3.

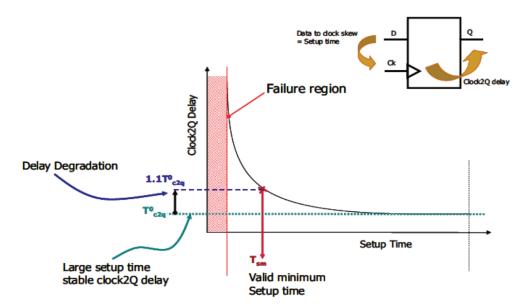

#### Arbiter setup and hold times

Since the arrival times of the two signals at the arbiter inputs can be very close, metastability [1] can result at the arbiter output. In other words, given the small values for the path delay standard deviations  $(\sigma_p)$  at the arriving paths, it is possible that the setup and hold window restriction are not satisfied, thus resulting in an undefined value for Q. Moreover, given an arbiter with a large setup time, the circuit could also miss the delay difference of the two paths, producing a similar response as if they were the same, an undesirable situation for an arbiter. Hence, decreasing the  $t_{su}$  of the arbiter as much as possible is a way to assure that even small differences between the two paths delays at its inputs will be detected. Moreover, if the delay difference between two paths is small enough and cannot satisfy the storage element hold time  $(t_h)$  the output transition is not guaranteed, another situation which should be avoided by the arbiter.

Section 4.3 evaluates the impact of using DFF and SR-Latch as APUF arbiters.

# Chapter 4

### Experimental Results

This section describes a number of experiments aiming at evaluating the impact of design techniques in APUF's response variability. The tri-state arbiter PUF, described in Section 1 is used as the baseline. Section 4.1 describes the simulation infrastructure used during the experiments. Section 4.2 describes the performed experiments focusing on finding the best logic design for the APUF delay network. In this section we evaluate the available cells in the standard library searching for the one that produce the largest delay variation. Also, we experimentally evaluate the impact of gate sizing (changes in transistor geometry - L and W) with respect to the gate delay variation. On Section 4.3 we experimentally define the forbidden window (setup + hold time) of each arbiter candidate(DFF, balanced and unbalanced SR-latch), searching for the architecture that exhibits the narrowest window, so as to minimize the chance of metastability. Thus we expect that even for small delay differences in the racing paths, the metastability problem will be reduced.

#### 4.1 Simulation Infrastructure

Experiments used Cadence Virtuoso Analog Design Environment (ADE) with Spice-based Monte-Carlo support, a professional tool for analog circuit design and simulation. ADE supports a proprietary script language, named OCEAN, which gives the designer full control over the simulation process. Standard cells and process-related information were provided by the AMS 350nm v3.80 hitkit.

The simulations performed in this work used a cluster (Figure 4.1) composed of seven nodes, each having a 32-cores CPU, 16GB RAM memory and individual hard-disks to store the results and to run the simulation locally. Nodes setup was done by installing the Cadence simulation tools natively, using a compatible operational system; no virtual machine was required. They are connected through a high-speed local LAN for fast result sharing. This robust infrastructure was required due to the high amount of SPICE analog simulations necessary to have a high enough sample space to perform an adequate statistical analysis.

Figure 4.1: Cluster de simulação dos experimentos

# 4.2 Delay Network Simulation

A set of Monte-Carlo simulation experiments was performed in order to determine the best logic design for the APUF delay network as discussed in Section 3.1. This was achieved through a set of two experimental groups. In the first group (Section 4.2.2) the goal is to determine, from all gates in the standard-cell library, those which have the largest gate delay standard deviation ( $\sigma_g$ ). The second group (Section 4.2.3) studies the dependence of  $\sigma_p$  with gate sizing, i.e. when the channel Length (L) and Width (W) of the gate transistors' change.

## 4.2.1 Testbench for cell delay characterization

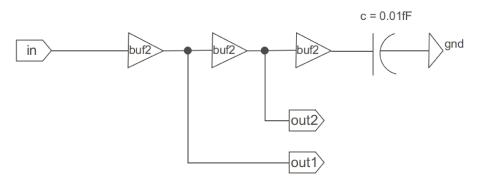

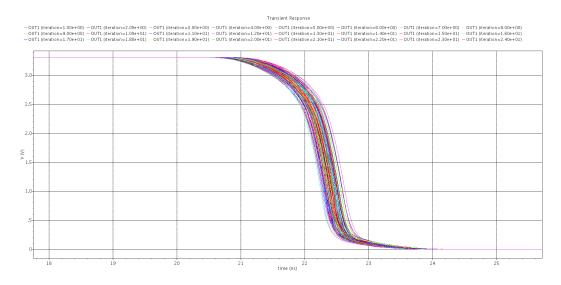

Figure 4.2 shows an example of a circuit using buf2 cell, used to characterize every cell candidate for the delay network, whose results are listed in Section 4.2.2 and Section 4.2.3. The circuit is composed by three cells of the same type and drive strengths connected in series. The cell under characterization is located at the centre, so that the input signal slope and output load offer real conditions.

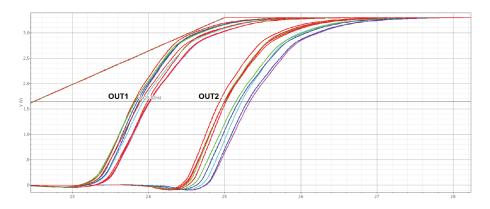

The characterization procedure starts by applying a step signal in the input port and measuring the delay difference between signals out1 and out2. As it is performed using analog simulation, the output signals are rising curves. The time measurement points used are located in 50% of VDD, in this case at 1,65V. The cell delay mean and standard deviation uses Monte-Carlo simulation with 400 iterations, providing 400 pairs of (out1,out2) timestamps values, varied according to fabrication process distribution model (Figure 4.3). The difference of each pair of values provide the cell delay for the given Monte-Carlo iteration. These data are used to calculate cell delay mean and standard

deviation. Table 4.1 shows the obtained results for each cell type.

Figure 4.2: Single cell characterization circuit

Figure 4.3: Transient result of the simulation

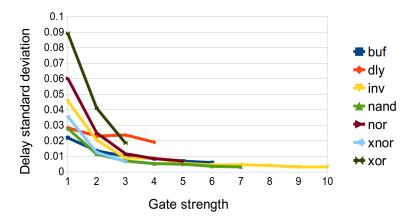

## 4.2.2 Selecting the gate with best $\sigma_q$

The AMS 350nm library contains a few drive strength options for each combinational gate. The objective of this study is to validate our hypothesis, described in Section 3.1.3, that the best candidate to increase delay variability is the one with the weakest drive strength. For this analysis, each gate type and strength went through Monte-Carlo simulation using 400 instances for each one. The results, shown in Figure 4.4, reveal that the  $\sigma_g$  of the library gates increase as the gate strength decreases. Hence, the weakest gates are those which produce the largest standard deviation over the delay mean. As shown in Table 4.1, for all combinational gate types and strengths of Figure 4.4, the xor20 is the best candidate for the delay network, presenting the largest  $\sigma_g$ .

## 4.2.3 Variation of $\sigma_p$ with gate sizing ( $\Delta W$ and $\Delta L$ )

The experiment described in this section aims at analyzing the impact of gate sizing (changes in transistor geometry parameters – L and W) on  $\sigma_g$  and evaluate its consequence to the path delay deviation  $\sigma_p$ . The analytical model, described in Section 3.1.1, shows that the increase of  $\sigma_g$  is directly proportional to transistor L size, and that W size has a little impact over it.

Figure 4.4: Standard deviation  $(\sigma_g)$  as gate strength increases.

| Gate Type | Avg. Delay | Std. Dev. $(\sigma_g)$ |

|-----------|------------|------------------------|

| buf2      | 2,718      | 0,022                  |

| dly12     | 3,826      | 0,028                  |

| inv0      | 6,966      | 0,046                  |

| nand20    | 5,762      | 0,028                  |

| nor20     | 7,005      | 0,060                  |

| xnor20    | 5,857      | 0,036                  |

| xor20     | 10,295     | 0,089                  |

Table 4.1: Average delay and standard deviation  $(\sigma_g)$  for combinational library gates

To confirm this hypothesis, we respectively modify the original gate transistors size (L and W) by multiplying their baseline values  $L_0$  and  $W_0$  from the smallest gate by factors  $K_L = L/L_0$  and  $K_W = W/W_0$ . Each version of the modified gate went through Monte-Carlo simulation using 400 instances, and the respective  $\sigma_g$  was determined.

Figure 4.5 shows the value of  $\sigma_g$  for various strengths of the combinational gates when  $K_W$  scales the size of W from 1 to 32 times. The results show that although  $\sigma_g$  increases only slightly for fairly small values of W, the variation is irrelevant. Thus, according to the analytical model in Section 3.1.1, increasing W will not affect much the standard deviation of the gate delay  $(\sigma_g)$  and therefore gates used in APUF network paths should have the smallest possible value of W.

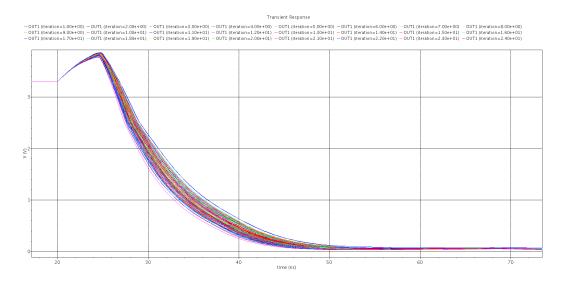

A similar experiment was also performed for L. As shown in Figure 4.6,  $\sigma_g$  increases considerably with  $K_L$ . Therefore, contrary to W and according to the analytical model of Section 3.1.1, increasing the gate's transistors channel length has a significant impact on the gate delay standard deviation over the delay mean. Figure 4.7 shows the experimental result of the delay variation of an inverter gate when having the original L size, and Figure 4.8 when having it scale 32 times bigger.

The same behaviour was present in all other combinational gates of the library. Therefore, given the considerable impact of  $K_L$  in  $\sigma_g$ , channel length sizing will be used, from the remaining of this work, as the design technique of choice to control the  $\sigma_p$  of APUF delay network paths. Notice the reader that, contrary to a typical logic design, designing APUFs requires an increase in L so as to improve delay variability.

Figure 4.5: Gate delay standard deviation  $\sigma_g$ s a function of  $K_W$   $(K_L=1)$

Figure 4.6: Gate delay standard deviation  $\sigma_g$ s a function of  $K_L$  ( $K_W = 1$ )

Figure 4.7: Delay variability fast cell

Figure 4.8: Delay variability slow cell

Table 4.2 lists the values of  $\sigma_g$  for all combinational gates in the library and the smallest (1) and the largest (32) values of  $K_L$ . Given that APUF design seeks to use gates with the largest delay variability, the best candidate in Table 4.2 is dly12.

| Gate Type | N       | Iean    | Std. Dev. $(\sigma_g)$ |        |  |

|-----------|---------|---------|------------------------|--------|--|

|           | $K_L=1$ | 32      | $K_L=1$                | 32     |  |

| buf2      | 0,151   | 36,460  | 0,077                  | 1,437  |  |

| dly12     | 1,269   | 798,758 | 0,068                  | 30,065 |  |

| inv0      | 0,208   | 20,206  | 0,052                  | 1,193  |  |

| nand20    | 0,299   | 40,869  | 0,042                  | 2,540  |  |

| nor20     | 0,166   | 27,709  | 0,034                  | 1,658  |  |

| xnor20    | 0,349   | 65,242  | 0,041                  | 5,295  |  |

| xor20     | 0.300   | 87,854  | 0,059                  | 5,077  |  |

Table 4.2: Mean and standard deviation for modified combinational gates

### 4.3 Arbiter Simulation

The first step a designer must take to design an APUF arbiter is to evaluate all possible storage element candidates according to the the requirements described in Section 3.2. As mentioned before, two possible arbiter candidates are the DFF and the SR-Latch.

As discussed in the first requirement of Section 3.2, a simple analysis of the logic of DFF and SR-Latch shows that the DFF has unbalanced input to output paths, suggesting that the SR-Latch is probably a better choice for an APUF arbiter. On the other hand, a careful analysis of the setup and hold times of the DFF and SR-Latch should be performed to evaluate the storage element which satisfies the second requirement in that section, i.e. the smallest possible forbidden window. This is done to assure that the selected device is the most sensitive one, capable of capturing any small path delay differences produced

by the APUF network paths. Section 4.3.1 describes the used procedure and obtained results.

### 4.3.1 Selecting the arbiter with smallest forbidden window

The setup time characterization process for a DFFs and SRLs is well-known [2] and follows a straighfoward procedure which measures the delay from each input to the Q output. For the case of the DFF, two input signals are used: Data (D) and Clock (CLK). In each of the signals it is applied a rising edge step-function out of phase, illustrated by the letters C and D in Figure 4.9.

Figure 4.9: Setup and Hold times specification for rising-edge-triggered flip-flop

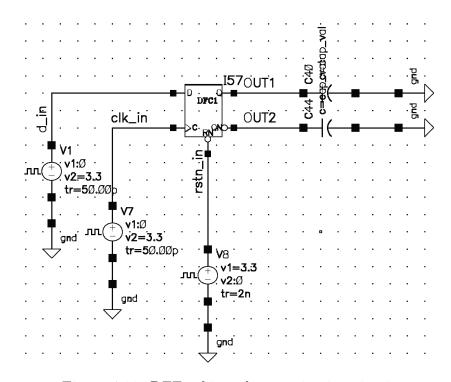

To determine the nominal delay, the experiment is initially configured so that a long time difference is used between the moment that D and CLK transitions are applied. This guarantees that the setup time is satisfied and that the clk-to-Q delay is the fastest possible nominal delay. The next steps in the experiment consists in decreasing the application time between D and CLK and measuring its impact in clock-to-Q. The experiment keeps reducing the difference until the output signal stops transiting to '1'. The setup time  $(T_{su})$  is then defined to be in between 5% to 10% of the nominal delay clk-to-Q (industrial standard). The hold time characterization for the DFF is not necessary for this work because, after the transition, both signals stay stable at logic '1' until the next APUF challenge is applied, which just occurs after evaluating the arbiter result. Figure 4.10 illustrates the described procedure and Figure 4.11 shows the circuit used for the DFF arbiter characterization, which also includes a signal to reset the flip-flop to a well-known state at the beginning of every simulation.

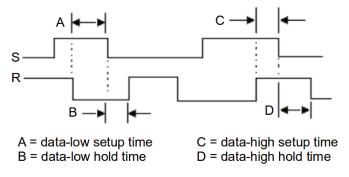

For the latch characterization, we defined the equivalent setup and hold time conditions (Figure 4.12) [2]. The setup time is the minimum time that signal S needs to arrive in NAND SR-latch before signal R. In case S arrives very close to R, the output signal stays in a metastable value for a certain time before stabilizing to zero(Figure 4.14). This could take as long as many nanoseconds. The hold time is the minimum time that signal R needs to arrive in NAND SR-latch before signal S. In case R arrives very close to S, it causes the output value to bounce to a value that can be lower than  $V_{ih}^{-1}$  or even flip the output (Figure 4.15).

Figure 4.13 shows the circuit used for the SR-Latch arbiter characterization. The experiments have shown that the *setup time* for the SR-Latch can be less strict than the

<sup>&</sup>lt;sup>1</sup>Minimum input voltage guaranteed to be recognized as a logical "1".

Figure 4.10: DFF characterization procedure [2]

Figure 4.11: DFF arbiter characterization circuit

Figure 4.12: Setup and Hold times specification for SR-Latch