### Instituto de Computação Universidade Estadual de Campinas

## Metodologias de Suporte a Verificação e Análise de Modelos de Plataformas em Alto Nível de Abstração

#### Bruno de Carvalho Albertini

Este exemplar corresponde à redação final da Tese devidamente corrigida e defendida por Bruno de Carvalho Albertini e aprovada pela Banca Examinadora.

Campinas, 6 de Outubro de 2011.

Prof. Dr. Sandro Rigo (Orientador)

Prof. Dr. Guido Araújo (Co-orientador)

Tese apresentada ao Instituto de Computação, UNICAMP, como requisito parcial para a obtenção do título de Doutor em Ciência da Computação.

### FICHA CATALOGRÁFICA ELABORADA POR ANA REGINA MACHADO – CRB8/5467 BIBLIOTECA DO INSTITUTO DE MATEMÁTICA, ESTATÍSTICA E COMPUTAÇÃO CIENTÍFICA – UNICAMP

AL14m

Albertini, Bruno de Carvalho, 1980-

Metodologias de suporte a verificação e análise de modelos de plataformas em alto nível de abstração / Bruno de Carvalho Albertini. – Campinas, SP: [s.n.], 2011.

Orientador: Sandro Rigo. Coorientador: Guido Costa Souza de Araújo. Tese (doutorado) - Universidade Estadual de Campinas, Instituto de Computação.

1. Depuração na computação. 2. Reflexão (Computação). 3. Arquitetura de computador. 4. Hardware - Engenharia de sistemas. I. Rigo, Sandro, 1976-. II. Araújo, Guido Costa Souza de, 1962-. III. Universidade Estadual de Campinas. Instituto de Computação. IV. Título.

#### Informações para Biblioteca Digital

Título em inglês: Analysis and verification support methodologies for

high abstractions level platforms **Palavras-chave em inglês:**

Debugging in computer science

Reflection (Computer science)

Computer architecture

Hardware - Systems engineering

**Área de concentração**: Ciência da Computação **Titulação**: Doutor em Ciência da Computação

Banca examinadora:

Sandro Rigo [Orientador]

Rodolfo Jardim de Azevedo

Paulo Cesar Centoducatte

Luiz Cláudio Villar dos Santos

Ney Laert Vilar Calazans

Data da defesa: 06-10-2011

Programa de Pós-Graduação: Ciência da Computação

### TERMO DE APROVAÇÃO

Tese Defendida e Aprovada em 06 de outubro de 2011; pela Banca examinadora composta pelos Professores Doutores:

| Prof. D | r. Luiz | Cláudio Villar | dos Santos |

|---------|---------|----------------|------------|

|---------|---------|----------------|------------|

INE / UFSC

Prof. Dr. Ney Laert Vilar Calazans Faculdade de Informática / PUC-RS

Prof. Dr. Paulo Cesar Centoducatte

IC / UNICAMP

Prof. Dr. Rodolfo Jardim de Azevedo

IC / UNICAMP

Prof. Dr. Sandro Rigo IC / UNICAMP

### Instituto de Computação Universidade Estadual de Campinas

## Metodologias de Suporte a Verificação e Análise de Modelos de Plataformas em Alto Nível de Abstração

### Bruno de Carvalho Albertini<sup>1</sup>

Outubro de 2011

#### Banca Examinadora:

- Prof. Dr. Sandro Rigo (Orientador)

- Prof. Dr. Rodolfo Jardim de Azevedo Unicamp

- Prof. Dr. Paulo Cesar Centoducatte Unicamp

- Prof. Dr. Luiz Cláudio V. dos Santos Universidade Federal de Santa Catarina

- Prof. Dr. Ney Laert V. Calazans

Pontifícia Universidade Católica do Rio Grande do Sul

- Prof. Dr. Edson Borin Unicamp (Suplente)

- Prof. Dr. Mario Lúcio Côrtes Unicamp (Suplente)

- Prof. Dr. Roberto A. Hexsel

Universidade Federal do Paraná (Suplente)

<sup>&</sup>lt;sup>1</sup>Suporte financeiro da Fundação de Amparo à Pesquisa do Estado de São Paulo (FAPESP, processo 2007/58129), CNPq (processo 141774/2007-0) e suporte material do Laboratório de Sistemas Computacionais (LSC) da Universidade Estadual de Campinas (UNICAMP)

## Resumo

A crescente complexidade das descrições de hardware em alto nível tem motivado a criação de metodologias de desenvolvimento por vários anos, sendo o mais recente nível de abstração representado pelo que é chamado de projeto Electronic System Level (ESL) e os projetos baseados em plataformas. Neste cenário, a exploração simultânea de diversos modelos arquiteturais, como os Systems-on-Chip (SoC), é a chave para se obter um bom balanceamento no particionamento hardware-software e melhorar o desempenho tanto do hardware quanto do software. Isto demanda uma infraestrutura de simulação de plataformas capaz de simular com rapidez, em um alto nível de abstração, tanto o software quanto o hardware. SystemC despontou como uma das linguagens de descrição mais adotadas e, juntamente com a modelagem em nível de transação (TLM, do inglês Transaction Level Modeling), vem sendo amplamente reconhecido como a técnica mais propícia para desenvolvimento em ESL. Uma das características mais marcantes de TLM é a possibilidade de reutilizar toda a infraestrutura da plataforma para a simulação de hardware e software [12].

A integração da verificação no fluxo de projeto é muito importante em uma metodologia baseada em TLM. Uma das técnicas de verificação mais conhecidas é a injeção de estímulos, usada para guiar a simulação para casos limite. Este tipo de funcionalidade é útil para aumentar a cobertura da verificação. As ferramentas disponíveis para descrições SystemC não permitem injeção de estímulos sem que o modelo seja alterado ou sem a utilização de um núcleo de simulação modificado para tal tarefa. Para a depuração, não temos notícia de nenhuma ferramenta de código aberto disponível, porém existem boas ferramentas comerciais preparadas especificamente para a depuração de modelos em SystemC.

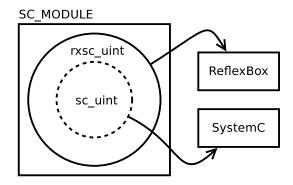

Nesta tese são propostas três metodologias para melhorar a capacidade de introspecção, depuração e análise de modelos de hardware descritos em alto nível de abstração. A primeira delas é composta por uma metodologia de reflexão computacional aplicável a módulos SystemC através da inserção de módulos de inspeção, que chamamos de ReflexBox. A segunda técnica desenvolvida foi chamada de SignalReplay, e representa uma evolução da primeira técnica voltada para a captura, análise e injeção dos dados coletados

pela reflexão. A última metodologia proposta, chamada de PDFA (do inglês, *Platform Dataflow Analysis*) visa extrair metadados através da reflexão de tipos sobrecarregados, permitindo que o projetista aplique técnicas de compiladores para a análise de *hardware*.

Os resultados obtidos são apresentados como experimentos, implementados na forma de estudos de caso. Estes experimentos permitiram avaliar a eficácia das técnicas propostas que, ao contrário de trabalhos correlatos, aderem a seis princípios que consideramos fundamentais: (1) não são intrusivas em relação às modificações no modelo que podem ser necessárias para implementar a introspecção; (2) não necessitam de modificações no ambiente de simulação, compiladores ou bibliotecas, incluindo nossa linguagem alvo: SystemC; (3) geram uma sobrecarga pequena no tempo de simulação; (4) proveem observabilidade e controlabilidade; (5) são extensíveis, permitindo a adaptação para utilização em trabalhos similares, com pouca ou nenhuma modificação nas metodologias; e (6) protegem a propriedade intelectual do módulo sob verificação.

## Abstract

The increasing complexity of high level hardware descriptions has motivated the creation of development methodologies for several years, being the most recent level of abstraction represented by projects based on platforms and on the so called Electronic System Level design (ESL). In this scenario, simultaneously exploring different architectural models, like Systems-on-Chip (SoC), is the key to achieve a good balance on hardware-software partitioning and improve performance of both hardware and software. This requires a platform simulation infrastructure able to simulate at high speeds and high level of abstraction, both software and hardware. SystemC emerged as one of the most widely adopted description languages and, when used with the Transaction Level Modeling (TLM), has been widely recognized as the most suitable for ESL development. One of the most striking features of TLM is the possibility to reuse all the infrastructure platform for the simulation of hardware and software [12].

Integration of the verification into design flow is a key point in a TLM-based methodology. One well-known verification technique is the injection stimuli, used to guide the simulation to borderline states. This kind of functionality is useful to increase the coverage of the verification. The tools currently available for SystemC descriptions do not allow stimuli injection without model modifications, or without the use of a modified SystemC simulation core specially crafted for this task. We could not find any open source tool for debugging, but there are good commercial tools specifically prepared to SystemC model debugging.

This thesis proposes three methodologies focused on improving the support for introspection, debug, and analysis of hardware models described in high abstraction level. First one is a methodology using computational reflection, applicable to SystemC descriptions by inserting inspection modules, that we call *ReflexBoxes*. The second technique is called *SignalReplay*, an evolution of the first technique focused on the capture, injection, and analysis of data collected by reflection. The last proposed methodology, called Platform Dataflow Analysis (PDFA), aims on the metadata extraction through overloaded type reflection, allowing the designer to use compiler techniques for hardware analysis.

The results are presented as experiments, implemented as case studies. These expe-

riments allowed us to evaluate the effectiveness of the proposed techniques that, unlike related work, adhere to what we consider six fundamental principles: (1) are not intrusive regarding any model modifications that may be necessary to implement introspection; (2) do not require any change in simulation environment, compilers, or libraries, including our target language: SystemC; (3) generate minimal overhead in simulation time; (4) provide observability and controllability; (5) are extensible, allowing the adaptation for use in similar work with little or no change in the methodology; and (6) protect the intellectual property of the module under verification.

# Agradecimentos

Agradeço ao CNPq e à FAPESP, por proporcionar o suporte financeiro que me manteve no doutorado durante os anos iniciais. Também à Unicamp, em especial ao LSC (Laboratório de Sistemas Computacionais) do Instituto de Computação, do qual utilizei intensivamente os recursos para a implementação das ideias aqui expostas.

Aos professores, Côrtes, Pannain, Ducatte e Rodolfo, que me ensinaram a maior parte do que sei hoje sobre a minha área. Um agradecimento especial ao Guido e ao Sandro, que são os responsáveis pelo amadurecimento das ideias, pelas horas de discussão e paciência em me orientar.

À minha família, que me proveu o suporte necessário, aos meus pais que me deram os genes e a minha namorada, que graciosamente cedeu seu tempo comigo em prol do doutorado em diversas ocasiões.

Por último, aos colegas de laboratório pelo convívio diário, pelas discussões de ideias e pelo companheirismo, dentro e fora do ambiente acadêmico. Até mais e obrigado pelos peixes.

# Sumário

| $\mathbf{R}$     | esum  | 10       |                                                  | $\mathbf{v}$ |

|------------------|-------|----------|--------------------------------------------------|--------------|

| $\mathbf{A}$     | bstra | ct       |                                                  | vii          |

| $\mathbf{A}_{i}$ | grade | ecimen   | tos                                              | ix           |

| 1                | Intr  | oduçã    | 0                                                | 1            |

| 2                | Tra   | balhos   | Relacionados                                     | 9            |

| 3                | Intr  | cospec   | ção em Plataformas SystemC                       | 15           |

|                  | 3.1   | Depur    | ação e Verificação de Modelos em SystemC         | . 15         |

|                  | 3.2   | Por qu   | ue a Reflexão Computacional?                     | . 16         |

|                  | 3.3   | Intros   | pecção em Módulos SystemC                        | . 18         |

|                  | 3.4   | Depur    | ando uma Plataforma Exemplo Através de Simulação | . 21         |

|                  | 3.5   | Verific  | ação de Módulos Isolados                         | . 30         |

|                  |       | 3.5.1    | Signal Replay                                    | . 31         |

|                  | 3.6   | Conclu   | ısão                                             | . 37         |

| 4                | Ana   | álise de | e Fluxo de Dados em Plataformas                  | 39           |

|                  | 4.1   | Anális   | e de Fluxo de Dados                              | . 39         |

|                  |       | 4.1.1    | Conjuntos generate e kill                        | . 41         |

|                  |       | 4.1.2    | Conjuntos input e output                         | . 43         |

|                  | 4.2   | Anális   | e de Fluxo de Dados em Plataformas               | . 44         |

|                  |       | 4.2.1    | Conjuntos generate e kill                        | . 45         |

|                  |       | 4.2.2    | Conjuntos input e output                         | . 46         |

|                  |       | 4.2.3    | Comentários Sobre a Implementação                | . 46         |

|                  |       | 4.2.4    | Interações Entre os IPs                          | . 47         |

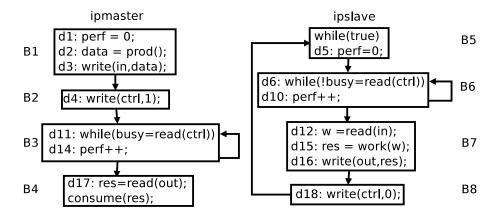

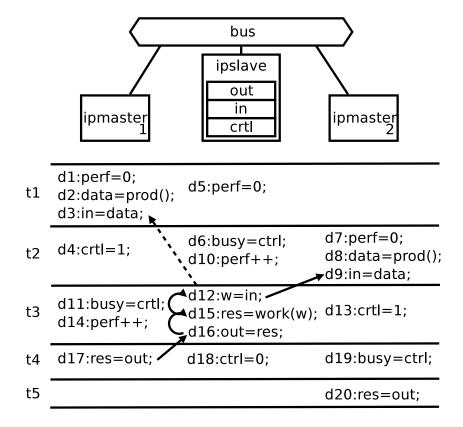

|                  | 4.3   | Estude   | o de Caso #1                                     | . 48         |

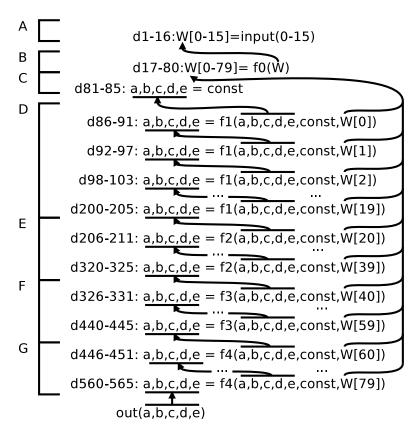

|                  | 4.4   | Estude   | o de Caso #2                                     | . 51         |

|   |     | Experimentos                |

|---|-----|-----------------------------|

|   |     |                             |

| 5 | Cor | nclusão e Trabalhos Futuros |

|   | 5.1 | Trabalhos Futuros           |

|   | 5.2 | Lista de Publicações        |

| A | Lin | h <sub>o</sub>              |

# Lista de Tabelas

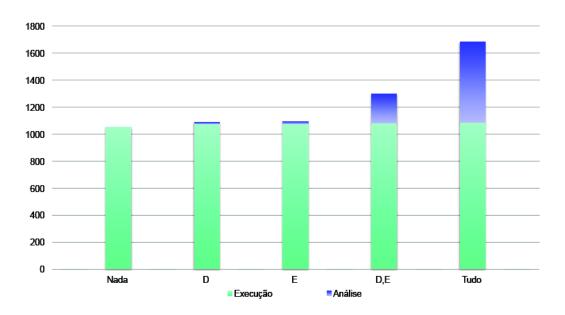

| 3.1 | Tempo médio de simulação (segundos) do MP3 com Signal Replay, desvio |    |

|-----|----------------------------------------------------------------------|----|

|     | padrão (DP) e ganho                                                  | 35 |

| 4.1 | O conjuntos generate e kill para o código de exemplo                 | 42 |

| 4.2 | O conjuntos generate e kill para os blocos básicos do exemplo        | 43 |

| 4.3 | O conjuntos $in$ e $out$ para os blocos básicos do exemplo           | 44 |

| 4.4 | O conjuntos generate e kill para o estudo de caso #1                 | 51 |

| 4.5 | Conjuntos $in e out$ para o estudo de caso $\#2$                     | 53 |

| 4.6 | Tempos de execução para o estudo de caso #2                          | 55 |

# Lista de Figuras

| 1.1  | Níveis de abstração usados na modelagem de hardware                          | 2  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Fluxo básico de desenvolvimento ESL                                          | 6  |

| 3.1  | Fluxo de reflexão usando a biblioteca Reflex-SEAL                            | 19 |

| 3.2  | Arquitetura da Plataforma MP3 dist10 modificada                              | 23 |

| 3.3  | Trecho do dicionário de dados para o IP ac_tlm_imdct                         | 24 |

| 3.4  | O arquivo main.cpp representando a configuração da plataforma MP3            |    |

|      | usada no exemplo                                                             | 25 |

| 3.5  | Interagindo com o <i>ReflexBox</i> através de telnet                         | 26 |

| 3.6  | Exemplo de execução do ReflexBox                                             | 28 |

| 3.7  | Inserindo um breakpoint no ReflexBox                                         | 28 |

| 3.8  | Mudando a condição de parada do $\textit{ReflexBox}$                         | 29 |

| 3.9  | Atributos refletíveis do módulo IMDCT, mostrados pelo $\textit{ReflexBox}$   | 29 |

| 3.10 | Saída da introspecção do módulo IMDCT                                        | 29 |

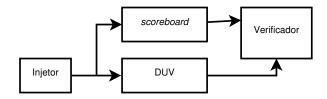

| 3.11 | Reprodução da simulação do estudo de caso para o $Signal\ Replay$            | 32 |

| 3.12 | Exemplo de Plataforma DUV para scoreboard                                    | 33 |

| 3.13 | A plataforma de estudo para o $Signal\ Replay$ instrumentada usando reflexão | 35 |

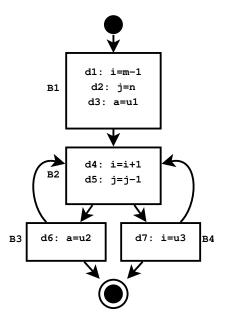

| 4.1  | Trecho de código com as sentenças numeradas de $s_1$ a $s_{10}$              | 40 |

| 4.2  | Definições contidas no trecho de código, numeradas de $d_1$ a $d_7$          | 40 |

| 4.3  | CFG para o trecho de código da Figura 4.2                                    | 41 |

| 4.4  | Encapsulamento to tag                                                        | 47 |

| 4.5  | CFG do estudo de caso #1                                                     | 48 |

| 4.6  | Plataforma do estudo de caso #1                                              | 50 |

| 4.7  | Organização interna da primeira versão do IP SHA                             | 52 |

| 4.8  | A plataforma SHA                                                             | 54 |

| 4.9  | Tempos de execução em segundos para o estudo de caso #2                      | 56 |

# Capítulo 1

# Introdução

Os projetos eletrônicos modernos estão se tornando cada vez mais complexos. O crescimento do mercado de dispositivos eletrônicos a partir da segunda metade da década de 90, impulsionado principalmente pela crescente utilização de dispositivos móveis, mudou a forma como a indústria eletrônica executa os projetos. Antes da revolução SoC (do inglês, System-On-Chip) as indústrias eletrônicas possuíam o domínio de todo o ciclo de projeto, desde a definição até a fabricação. Nos dias atuais, a identificação de uma nova oportunidade de mercado, a definição e especificação do projeto, o desenvolvimento e montagem dos diversos componentes e a fabricação do produto final são etapas cada vez mais realizadas por diferentes organizações. Chamamos esta característica de **ortogonalização** da indústria eletrônica, pois esta mudou de uma posição de projetos vertical (interna) para horizontal.

Além de focar na competência principal de cada organização envolvida, esta forma de projeto permite que as empresas trabalhem em paralelo, de forma a reduzir o tempo entre a concepção e a entrega de um produto, também chamado de TTM (do inglês, *time-to-market*). Esta pressão do mercado pela diminuição do TTM e a complexidade crescente dos projetos, forçou os projetistas a adotarem técnicas que aumentem a produtividade, porém sem prejudicar a qualidade dos produtos. As propostas que sobreviveram até os tempos atuais possuem duas características em comum: o alto nível de abstração e a reutilização de componentes.

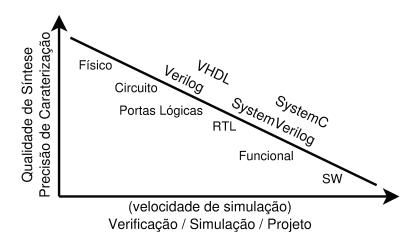

Os níveis de abstração dos projetos de *hardware* possuem várias nomenclaturas e diferentes classificações, começando no silício, o nível **físico**, passando pelos níveis de **circuitos**, ainda amarrado à disposição física dos componentes mas já com certa modularização, e o de **portas lógicas**. A maioria das linguagens de descrição de *hardware* permitem que um modelo seja escrito no nível de portas lógicas, porém este nível normalmente é fruto da compilação de níveis com abstração mais alta. Na prática, estes três níveis somente são utilizados quando o projetista precisa de uma caracterização precisa (ex. consumo,

atraso, tamanho, etc), normalmente na fase final de um projeto.

Quanto mais baixo o nível de abstração, mais próximo se está de um modelo sintetizável, em detrimento da velocidade com que se desenvolve o projeto, incluindo-se a verificação e depuração do mesmo. Hoje em dia, podemos dizer que os níveis físico e de circuito são usados somente em módulos isolados que possuem pré-requisitos específicos quanto a disposição física dos módulos no circuito final. Até mesmo o próximo nível, de portas lógicas, está se tornando obsoleto, principalmente devido à qualidade dos algoritmos de síntese atuais, capazes de gerar descrições sintetizáveis comparáveis às feitas pelo ser humano a partir de descrições de alto nível [6]. Dificilmente usa-se estes níveis para uma plataforma inteira pois possuem um desenvolvimento custoso, principalmente em relação ao tempo de projeto, além de serem muito propícios a erros.

Após as descrições de circuitos, os projetistas partiram para descrições de portas lógicas, suportadas por linguagens como Verilog e VHDL. Estas linguagens também abrangem os níveis de abstração de transferência entre registradores (RTL, do inglês Register Transfer Level). Linguagens mais recentes, como SystemC e SystemVerilog, suportam também o nível funcional, atualmente o nível de abstração mais próximo possível de uma implementação em software puro. Como dissemos anteriormente, o nível de portas lógicas está sendo gradualmente abandonado, sendo priorizados os níveis RTL e funcional. No nível funcional, algumas primitivas de hardware, como a temporização, normalmente são ignoradas de forma a se obter uma descrição comportamental do hardware. Com este aumento do nível de abstração, ganha-se a velocidade de simulação e a facilidade de depuração, em detrimento da síntese e precisão da caracterização.

Figura 1.1: Níveis de abstração usados na modelagem de hardware

Na Figura 1.1, mostramos uma visão geral dos níveis de abstração e as quatro linguagens mais utilizadas para descrições de *hardware*. Note que existe uma troca entre a qualidade da síntese e a velocidade de simulação. A primeira reflete diretamente na

precisão da caracterização e a segunda nas facilidades proporcionadas pelo maior nível de abstração, tais como maior velocidade de simulação e menor tempo de projeto (incluindo o tempo necessário para se efetuar mudanças).

Mesmo com o nível de abstração das descrições de hardware próximo a um software, a busca pela diminuição do TTM continha pressionando a indústria. O reuso de componentes, em todos os níveis de abstração, foi a solução encontrada para aumentar a confiabilidade do produto final e diminuir ainda mais o tempo de projeto. A reutilização de componentes sempre existiu, porém até a popularização das descrições em RTL, era utilizada com restrições pois, nos níveis de abstração mais baixos, os módulos possuem características que dificultam a portabilidade dos mesmos (ex. a interface de acesso externo). Com a adoção de descrições RTL, os projetistas passaram a contar com um grau maior de portabilidade, o que aumentou a reutilização devido a facilidade com que este nível de abstração proporciona na integração e personalização dos módulos. Com a portabilidade facilitada, os projetistas adotaram uma modificação do reuso, herdada do desenvolvimento de software: a utilização de componentes pré-validados. Estes módulos são chamados de IPs (do inglês, Intelectual Property), e normalmente são fornecidos em diferentes níveis de abstração, equivalentes funcionalmente entre si. Estes componentes são escritos de forma a possuírem características específicas de desempenho e consumo de energia, validados, e então fornecidos na forma de um módulo que o projetista pode integrar em sua plataforma. Nos tempos atuais, é possível comprar um IP com uma (ou mais) descrição sintetizável e sua equivalente funcional, usada para fins de simulação. O desenvolvedor do IP garante o funcionamento do módulo através de testes e feitos com este propósito. Normalmente, os vetores de testes utilizados são disponibilizados junto com o módulo, com informações sobre as simulações realizadas para validação, possibilitando que o desenvolvedor assuma que o módulo atende os requisitos necessários.

A reutilização de IPs possibilitou que o desenvolvedor construa plataformas baseadas total ou parcialmente em componentes prontos, chamados de componentes de prateleira (do inglês, off-the-shelf). Chamamos esta abordagem de desenvolvimento baseado em plataformas (do inglês, Platform Based Design). Uma plataforma é um conjunto de recursos de hardware e software capazes de operar conjuntamente para prover funcionalidade a uma classe de aplicações. Nesta forma de projeto, o projetista divide o sistema final em módulos funcionais, onde cada módulo realiza uma tarefa que contribui para o resultado final. Com a plataforma dividida em módulos, o projetista pode então experimentar diversas configurações da mesma, de forma a atingir os requisitos do produto final. Dois exemplos de exploração de plataformas são: a infraestrutura de comunicação entre os módulos e o particionamento hardware-software.

Particionamento é como se conhece a decisão de tornar um módulo um *hardware* ou executar a tarefa equivalente em *software*. Devido a abundância de processadores e a

facilidade de utilização (disponibilidade de compiladores, ferramentas de depuração e integração), a decisão de transformar um módulo em hardware está corriqueiramente ligada a requisitos de latência e consumo. Em relação a reutilização de módulos, é desejável que se utilize o máximo possível de módulos prontos e desenvolva-se somente módulos específicos. Apesar de a reutilização de IPs pré-validados ajudar a reduzir o trabalho de verificação dos módulos isoladamente, gera uma sobrecarga na validação da plataforma como um todo pois a combinação de vários IPs complexos pode levar a erros não previsíveis e difíceis de serem detectados.

Para descrever plataformas, criaram-se níveis de abstração baseados nos existentes para a descrição de hardware. O mais conhecido deles é o TLM (do inglês, Transaction Level Modeling). TLM utiliza o mesmo nível de abstração do nível funcional, mas também abstrai a comunicação entre os módulos, tornando-a chamadas de função. Como afirma Ghenassia no seu livro sobre técnicas TLM [12], um dos aspectos mais atraentes do nível TLM é a possibilidade de reutilizar toda a infraestrutura de uma plataforma para o desenvolvimento e verificação tanto do software quanto do hardware. Isso significa que a mesma plataforma em alto nível é utilizada como modelo de referência no fluxo de verificação funcional para o desenvolvimento do hardware, e também pelos desenvolvedores de software como uma especificação executável do sistema. Além disso, outro fator importante para uma descrição de hardware proporcionado pelo TLM, é a integração precoce da verificação no ciclo de desenvolvimento.

No âmbito de descrições de plataformas, chamamos de ESL (do inglês *Electronic System Level*) o conjunto de abstrações, linguagens e metodologias capazes de descrever plataformas em um alto nível de abstração (mesmo que utilizando vários níveis em uma mesma plataforma). No livro [27], capítulo 1, seção 1.2, os autores detalham os requisitos para que uma descrição possa ser chamada de ESL. Usando ESL, o projetista de *hardware* pode construir sua plataforma modularmente, escrevendo seus próprios módulos, infraestrutura de conexão e processadores. O objetivo principal é a simulação do projeto antes que o mesmo seja sintetizado, possibilitando a verificação, depuração e caracterização em alto nível, diminuindo assim os custos do projeto e o tempo de desenvolvimento.

Bailey e outros [3] dividem a capacidade de depuração e análise em três grupos distintos. A observabilidade é simplesmente a habilidade de identificar o estado interno e valores instantâneos de grandezas do sistema. A controlabilidade significa prover ao projetista os meios necessários para que este possa conduzir o sistema a atingir um estado interno preciso, de forma a aumentar o controle sobre o mesmo. A corretude é a capacidade de ajudar o projetista a corrigir erros descobertos, o que é mais fácil no nível ESL que no nível do silício, porém ainda não suportado completamente pelas ferramentas ESL.

Quanto mais alto o nível de abstração, mais fácil se torna conseguir boas ferramentas de depuração e análise. É sabido que em um sistema em silício, os únicos pontos que

podem ser observados são as interfaces externas e os pontos de observação, determinados ainda no projeto. No caso das descrições de hardware, a limitação da observabilidade e da controlabilidade está somente ligada a capacidade da linguagem e do ambiente utilizado de proverem mecanismos. Nas tecnologias ESL, os altos níveis de abstração utilizados nas descrições não devem ser somente vistos como atrativos devido à velocidade de simulação, mas também pela flexibilidade de exploração e recursos para depuração e análise (ex. substituição de IPs por equivalentes funcionais, introspecção interna dos módulos, mudança de topologia de comunicação, etc). Esta visão de uma plataforma como alvo de projeto cria uma demanda por novas funcionalidades relacionadas com a verificação em modelos de plataformas descritos em TLM. Os objetivos principais neste cenário são:

- aumentar a **cobertura da verificação** visando exercitar o maior número possível de caminhos tanto do *hardware* quanto do *software*, suficiente para que o módulo seja considerado correto;

- aumentar as possibilidades de **interação** do projetista com a plataforma, por exemplo guiando o fluxo de simulação para casos extremos de teste usando injeção de estímulos escolhidos propositalmente;

- tornar o ambiente de simulação mais amigável durante a depuração da plataforma, permitindo pontos de parada da simulação automáticos e introspecção da plataforma.

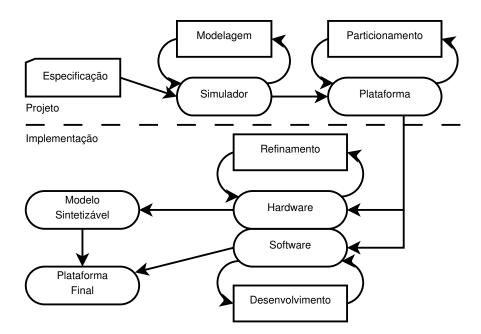

O ciclo de desenvolvimento mais comum de uma plataforma usando ESL é descendente (da mais alta abstração para a mais baixa), podendo ser dividido em duas fases distintas, conforme mostrado na Figura 1.2. A primeira consiste em montar uma especificação no mais alto nível possível, senão em software, para viabilização do projeto. Esta mesma fase gera um modelo da plataforma ou uma especificação executável da plataforma, de onde se retira a partição ideal entre software e hardware (entenda-se: decidir qual parte do modelo irá executar como software dentro de um processador e qual parte será executada em hardware). Com a abundante disponibilidade atual de processadores de uso geral e específico, esta decisão é normalmente tomada com base no tempo de entrega dos resultados do módulo (latência) e no consumo de energia do mesmo, mantendo-se em software os módulos que atingirem os requisitos mesmo quando executados em um processador.

A segunda fase possui dois fluxos de projeto. O primeiro diz respeito ao desenvolvimento do *software*, também chamado de *firmware* ou *midlet*, quando presente. Quase sempre, este fluxo consiste em desenvolver ou adaptar os módulos que executarão parte das funcionalidades na forma de *software* executando em um ou mais processadores, gerando o que chamamos de *software-IP*, um processador encapsulado que faz o trabalho que seria feito por um *hardware*. No outro fluxo, desenvolve-se o *hardware*, montando-se

Figura 1.2: Fluxo básico de desenvolvimento ESL

a plataforma através de módulos disponíveis ou descrevendo cada módulo, conectando-os por meio de estruturas específicas para tal (ex. barramentos). Neste fluxo existe um ciclo importante que chamamos de refinamento de IP. Na primeira rodada do fluxo, o que se tem é a especificação executável em alto nível, resultado da primeira fase, que pode ser usada como base para a elaboração da plataforma. Como esta é a primeira especificação executável, dificilmente é sintetizável. A cada iteração deste ciclo, o projetista faz uma descrição equivalente do módulo em uma abstração de mais baixo nível, alterando a linguagem de descrição se necessário, até atingir o nível sintetizável ou com detalhamento suficiente para que seja feita a caracterização da plataforma.

A grande vantagem do ESL em relação ao particionamento é que os dois fluxos podem ser feitos ao mesmo tempo. A partir da primeira iteração do fluxo de hardware, os projetistas de software já possuem um modelo estável e simulável da plataforma, com uma descrição do hardware condizente com o que será gerado em silício. Mais que isso, o desenvolvedor de software pode adotar qualquer uma das descrições oriundas das iterações de refinamento, incluindo a possibilidade de misturar descrições do mesmo módulo com diferentes níveis de abstração na mesma plataforma, de modo a obter o detalhamento do hardware que precisa para o desenvolvimento do software. Se o projetista está testando determinada funcionalidade, pode necessitar de um detalhamento maior no módulo alvo, porém caso não tenha interesse, pode usar uma versão funcional deste, de forma a obter um tempo de simulação mais rápido. O desafio dos desenvolvedores de ferramentas voltadas para ESL, é justamente manter a equivalência e a proximidade do hardware real mesmo

nos níveis de abstração mais altos.

A simulação virtual de plataformas [20], a verificação por asserções [17, 9, 15] e a introspecção [11, 8] são técnicas que têm sido adotadas como suporte para a exploração de plataformas escritas em linguagens de descrição de hardware, como SystemC. Notadamente, o que se busca com estas técnicas é analisar, caracterizar e validar (incluindo teste, depuração e verificação) as representações de projeto ainda no domínio do software.

Um dos problemas que encontramos é que estas técnicas usualmente são específicas de cada fabricante de ferramentas ESL ou específicas para uma determinada plataforma, não permitindo uma análise extensiva do comportamento da plataforma através do software, hardware e a comunicação entre estes dois domínios. Idealmente o projetista deveria ser capaz de rastrear qualquer valor (ex. contido em um registrador ou em uma variável) até sua origem, possivelmente em outro módulo, seja este um módulo de hardware ou software, independentemente da quantidade de outros módulos que estejam no caminho. Esta tarefa pode ser realizada por técnicas baseadas no rastreamento de dados [18], porém a análise resultante deste tipo de técnica não fornece informações suficientes para uma ampla verificação ou otimização da plataforma.

O objetivo principal desta tese é propor uma solução para alguns dos problemas encontrados na exploração de plataformas de descrição de hardware em alto nível. As contribuições deste trabalho serão apresentadas divididas em três fases. A primeira fase está relacionada à uma base para exploração de plataformas, consistindo em um arcabouço de ferramentas de apoio às técnicas propostas. Desenvolvemos e aplicamos uma metodologia de exploração ESL baseada na reflexão computacional como meio de obtenção das informações necessárias e injeção de sinais. Sobre esta metodologia e como complemento da mesma, desenvolvemos um módulo em SystemC capaz de utilizar a metodologia proposta e aplicá-la a qualquer módulo SystemC, em qualquer nível de abstração, sem se tornar intrusivo e com pouca interação do usuário. Esta metodologia, bem como o módulo de introspecção, estão descritos no Capítulo 3.

A segunda fase corresponde a uma adaptação da metodologia de reflexão, aplicada especificamente no modelo de verificação chamado de DUV. Na metodologia proposta, mostraremos como se utilizar as técnicas de reflexão desenvolvidas para melhorar a velocidade de simulação quando utilizada para verificação de módulos isolados da plataforma. Os vetores de teste são retirados da própria plataforma, através de uma simulação confiável, normalmente feita com o modelo de referência, com a especificação executável do sistema ou com uma plataforma onde o módulo alvo esteja descrito em um nível de abstração maior (no caso do refinamento). Chamamos esta metodologia de *Signal Replay* e pode-se encontrá-la na seção Seção 3.5.

A terceira e última fase corresponde a uma proposta para a análise de fluxo de dados em plataformas, usando a metodologia proposta no Capítulo 3 aliada à sobrecarga de

tipos para implementarmos uma adaptação da teoria de análise de fluxo de dados (compiladores). No Capítulo 4 mostramos a metodologia e dois exemplos práticos de aplicação voltados para a depuração de plataformas e para a análise de paralelismo em plataformas.

# Capítulo 2

## Trabalhos Relacionados

### Ferramentas Comerciais <sup>1</sup>

A ARM tem entre seus produtos uma ferramenta chamada RealView Development que, entre outras coisas, possibilita a depuração de modelos em SystemC em tempo real, incluindo exploração de plataformas TLM, depuração remota, onde é possível depurar uma simulação executando em uma máquina diferente da aplicação, e de baixo nível (esta última somente para modelos de processadores ARM).

O programa Vista Architecture é uma das ferramentas do pacote Vista, da Mentor Graphics. Este pacote de ferramentas possui o depurador para projetos em SystemC com o maior número de funcionalidades dentre as ferramentas avaliadas, permitindo que o projetista faça o trace das transações, veja a sequência de eventos e acompanhe a execução dos processos SystemC passo a passo. Através da própria ferramenta pode-se analisar o desempenho de um modelo específico na plataforma, considerando a implementação em hardware e na forma de um IP de software (é possível analisar o desempenho tanto no domínio do tempo quanto da potência).

O *Platform Architect* da *Synopsys* (originalmente da *CoWare*), possui a mesma abordagem que as ferramentas da Mentor, com foco na exploração de plataformas em alto nível e monitores de dados. A empresa possui um ambiente gráfico específico para a modularização de projetos, usando modelos C/C++ como ponto de partida de uma especificação executável. Hoje, esta ferramenta destaca-se pela sua capacidade de visualização gráfica de pacotes TLM, o que beneficia o projeto de arquiteturas de interconexão complexas, como NoCs.

A Cadence possui um conjunto de ferramentas chamadas Incisive Palladium que possui várias ferramentas de introspecção. A versão do SystemC fornecida com as ferramentas

<sup>&</sup>lt;sup>1</sup>Consulte o Apêndice A para referências às ferramentas citadas.

suporta asserções dinâmicas, uma versão da empresa para asserções condicionais, porém com parâmetros alteráveis em tempo de simulação; instrumentação de código, para inserção de pontos de depuração, *breakpoints*, etc; e depuração em tempo de execução. Há inclusive uma ferramenta chamada *Incisive Simulator* que, entre outras funcionalidades, é capaz de instrumentar o código automaticamente para permitir a geração automática de casos de teste.

Uma empresa japonesa chamada CATS, possui uma ferramenta de depuração para SystemC chamada XModelink SystemC Debugger. A ferramenta possui as operações básicas de depuração como watches, traces, etc., similares aos seus concorrentes, porém com limitações em relação às opções de depuração (ex. nem todos os tipos de dados podem ser inspecionados).

O problema principal das ferramentas comerciais é que muitas vezes elas utilizam versões proprietárias da biblioteca SystemC e da biblioteca de comunicação TLM, seja total ou parcialmente. Estas versões são especialmente projetadas para ajudar na depuração por meio de instrumentação das bibliotecas. A utilização destas versões instrumentadas está fortemente ligada à ferramenta oferecida. Na maior parte das vezes, o núcleo do SystemC adere à padronização da OSCI, porém com primitivas extras sobre o padrão, fazendo com que projetos específicos sejam amarrados à ferramenta e a portabilidade de IPs seja degradada. Devemos ainda considerar que a integração com qualquer código legado é difícil a ponto de inviabilizar a integração frente a um projeto completamente novo.

Também não há entre as ferramentas comerciais uma padronização dos testes, portanto não é possível utilizar um caso de teste gerado em uma ferramenta para alimentar um IP executando em outra sem antes adaptar os arquivos de dados para teste (traces).

Na medida do possível, avaliamos as ferramentas comerciais disponíveis, através dos convênios do Laboratório de Sistemas Computacionais (IC-UNICAMP) ou de versões disponíveis para avaliação. Nosso propósito desde o início do projeto foi ater-se estritamente às especificações padronizadas pela OSCI e usar somente ferramentas disponíveis gratuitamente, preferencialmente de código aberto. Por este motivo e pelo SystemC estendido ou fora de padrão, descartamos neste projeto a utilização das ferramentas comerciais avaliadas. Cabe ressaltar que, apesar de todas as ferramentas avaliadas oferecerem algum tipo de introspecção, nenhum mecanismo comercial é similar ao proposto neste trabalho.

### Trabalhos Acadêmicos

Rogin e outros [28] apresentaram um ambiente voltado para a depuração SystemC. Seu trabalho é baseado em uma biblioteca que sobrescreve o núcleo de simulação original do SystemC para capturar as informações de depuração. Além disso, este trabalho introduz

uma representação intermediária dos módulos de hardware desenvolvidos, permitindo um mapeamento da simulação com a descrição do modelo, em tempo de execução. A representação intermediária desenvolvida é compatível com o GDB, possibilitando que sejam desenvolvidas ferramentas gráficas para auxiliar no trabalho de depuração. De fato, os autores apresentam um exemplo de tal ferramenta. É importante salientar que a metodologia apresentada somente é aplicável a modelos em SystemC cujo código-fonte seja integralmente conhecido e disponível em tempo de execução, o que nem sempre é verdade quando se trabalha com bibliotecas comerciais, cujo código fonte é protegido.

SystemCXML [23] e LusSy [26] são ferramentas de código aberto voltadas para a visualização da hierarquia de conexão dos módulos SystemC. Apesar de proverem extração de metadados para módulos SystemC, não é possível depurar em tempo de execução sem que o projetista escreva os próprios módulos de depuração. Para esta abordagem de depuração em tempo de execução, pudemos encontrar somente o GDB e ferramentas derivadas do mesmo. O problema do GDB é que este se torna muito difícil de utilizar em plataformas, principalmente porquê este programa foi feito para depuração de um código genérico, não distinguindo assim o código da biblioteca SystemC do código do usuário. Os depuradores trazidos do domínio de software para o ambiente de prototipação de hardware, normalmente consideram todo o código de uma especificação executável, mesmo escrita em SystemC, como um único fluxo de execução. Se o projetista não tomar o devido cuidado, pode acabar com o depurador inspecionando o código que o projetista quer realmente depurar. Este fato, somado à complexidade da biblioteca SystemC, desencoraja a utilização de depuradores convencionais para C/C++, mesmo em projetos simples.

Até o momento, os trabalhos com a SCV (System C Verification Library) limitamse à verificação de modelos RTL. Sabemos pelas discussões nos grupos de interesse que há a intenção de também fornecer suporte para a depuração em alto nível em versões futuras, porém os trabalhos ainda não estão em uma fase madura o suficiente para serem utilizáveis, restringindo-se, no nível funcional, a verificações declarativas do tipo assert. Também nota-se que a SCV não está seguindo os planos de projeto da OSCI. A versão atual não é compatível diretamente com os compiladores atuais e não há previsão de atualização da biblioteca.

Lapalme e outros [19] desenvolveram um ambiente de prototipação de hardware baseado em uma linguagem de descrição chamada de ESys.NET [24], uma extensão da linguagem .NET (baseada em C#) para descrições de hardware. Eles foram pioneiros em identificar a necessidade de introspecção de código para propósitos de depuração e verificação mas, para eles, a introspecção é facilmente obtida pois C# possui suporte nativo à reflexão. Apesar de ter os trabalhos reconhecidos em publicações da área (ex. Transactions on Embedded Computing Systems, ACM), o grupo baseou-se na linguagem

C# como base de prototipação, ignorando as linguagens emergentes como SystemC e SystemVerilog. Acreditamos que a baixa aceitação do ambiente se deve ao fato de o mesmo ser fortemente ligado a um único sistema operacional e representar uma grande mudança de paradigma em relação às linguagens usadas nos níveis de abstração anteriores. Com o surgimento de SystemC, a utilização da ESys.NET está restrita a um pequeno grupo de pesquisadores, gerando dúvidas em relação a sua continuidade.

Déharbe e Medeiros [7] mostraram outra forma de se obter introspecção usando programação orientada a aspectos. A ideia principal do artigo é a instrumentação de todo o código para gerar métricas de codificação, porém a mesma técnica pode ser aplicada para propósitos de verificação e depuração. A instrumentação foi realizada usando a biblioteca AspectC++, uma extensão de C++ largamente utilizada como meio de obtenção deste paradigma de programação para esta linguagem de programação. A principal desvantagem desta abordagem é que os projetistas precisam ter conhecimento que o módulo a ser projetado será acessado usando esta metodologia e escrever todo o código usando o paradigma de orientação à aspectos (AOP, do inglês  $Aspect\ Oriented\ Paradigm$ ) que, na maior parte dos casos, significa que os projetistas precisam aprender um novo paradigma de programação. Outro problema da técnica é que o código legado deve ser adaptado de forma a adotar os mesmos princípios, tornando difícil a adoção em massa da metodologia proposta para o domínio da modelagem de hardware.

O ReSP [4] é uma proposta de uma ferramenta para depuração de modelos de SystemC que utiliza a linguagem Python para a obtenção da reflexão. O núcleo de simulação do SystemC e os modelos do usuário são mantidos sem modificações. O ambiente gera automaticamente um código envoltório sobre cada módulo SystemC (do inglês, wrapper) usando uma biblioteca de conexão de código C/C++ com a linguagem Python. Como esta última possui reflexão nativa, seus autores beneficiaram-se desta para implementar a introspecção. Em tese, a principal desvantagem deste trabalho é a sobrecarga na velocidade de simulação imposta pelo adaptador entre o ambiente de execução C/C++ (onde se executam os módulos em SystemC) e o ambiente interpretado do Python. Não obtivemos dados concretos sobre a sobrecarga deste projeto por meio de simulações próprias, pois o ambiente não é público. No artigo (e em outros relacionados) os autores afirmam que esta sobrecarga é de cerca de 1% do tempo total de simulação, porém o adaptador que os autores utilizaram gera uma sobrecarga dependente do número de chamadas entre os dois ambientes de execução. Para a característica de introspecção, são realizadas diversas chamadas de leitura e escrita em cada ciclo de simulação, motivo pelo qual acreditamos que esta técnica somente se aplique à introspecção de pequenos conjuntos de dados que não necessitam ser monitorados frequentemente. Este é o trabalho que hoje mais se assemelha ao proposto no Capítulo 3 desta tese.

Mathaikutty [23] e Shukla propõem uma maneira de classificar IPs de acordo com

metadados extraídos diretamente do código fonte dos módulos SystemC. A técnica para extrair os metadados utiliza reflexão computacional através de uma ferramenta chamada KaSCPar, que extrai os metadados do IP SystemC para um formato XML. O principal objetivo é a composição de IPs usando uma biblioteca de IPs previamente analisados, porém a abordagem com a reflexão é similar a que adotamos para nossos propósitos.

Misera [25] e outros mostraram que as metodologias de injeção de falhas podem ser aplicadas em SystemC para verificação. No artigo, os autores aplicam diversas técnicas de engenharia de software para injeção de falhas, como a inserção de mutantes e sabotadores. A injeção é feita explitamente, alterando o código para que o módulo aceite estímulos de verificação. A técnica que mostraremos possui a vantagem de injetar estímulos sem modificação no módulo. Não aplicamos as técnicas de verificação propostas, porém a metodologia que apresentaremos pode ser usada para os mesmos propósitos. Já Lisherness e Chang [21] apresentam SCEMIT, uma ferramenta para gerar e injetar automaticamente erros em plataformas SystemC. O foco é a técnica de injeção de mutantes para garantir a cobertura de testes gerados automaticamente. A injeção de mutantes consiste na inserção de códigos ou valores que simulem um estado específico do sistema, desejado para fins de verificação (ex.: forçar a tomada de um caminho condicional forçando um valor específico na variável de controle). Destacamos neste artigo a técnica utilizada para a injeção de estímulos: os autores criaram um módulo para um compilador capaz de injetar automaticamente os estímulos gerados. Esta técnica se mostrou mais rápida que as demais como asserções dinâmicas, modificações no núcleo de simulação e a reflexão, incluindo a que desenvolvemos. A técnica porém, possui seu uso limitado à injeção de sinais, não sendo genérica o suficiente para outras utilizações, mesmo relativas à depuração e à verificação. Além disso, é necessária a alteração do compilador, o que viola um dos nossos objetivos.

Chugh e outros [5] mostram uma forma de detectar e analisar condições de disputa de dados em programas concorrentes. Uma disputa de dados é caracterizada por acessos destrutivos concorrentes, como a escrita em uma variável compartilhada, cujo resultado final não é determinístico. Sua abordagem é baseada em uma centralização dos acessos concorrentes. Cada vez que o programa encontra uma definição, grava uma referência para a mesma em um módulo central. Para cada acesso concorrente com potencial para gerar uma condição de disputa, o programa consulta este módulo central para descobrir se a definição pode gerar um acesso indevido naquele ponto de execução. Apesar deste trabalho ser totalmente focado em paralelização de software, contribuiu para o desenvolvimento das definições de alcance mostradas no Capítulo 4.

O trabalho apresentado aqui possui vantagens em relação aos citados nesta seção. Nosso objetivo principal é prover um mecanismo de introspecção seguindo os seguintes princípios:

• O mecanismo não pode ser intrusivo. O projetista deve necessariamente não

ter que preparar seu IP para introspecção. Conforme mostra-se no Capítulo 3, na implementação proposta não é necessário nem mesmo o código-fonte do módulo a ser refletido.

- O mecanismo não deve requerer modificações no ambiente de simulação. Este trabalho se baseia na biblioteca SystemC padrão, sem modificações. A biblioteca de reflexão utilizada também é de código aberto, permitindo que o usuário altere ou escreva seus próprios módulos sem muito esforço de aprendizado. O ambiente utilizado na aplicação das técnicas apresentadas é o mesmo utilizado somente para simulação, sem necessidade de alteração do compilador, do sistema operacional ou qualquer biblioteca.

- O mecanismo deve ter **pouco impacto no tempo da simulação**. Realizaram-se experimentos (Capítulo 3) que permitem comparar o tempo gasto pela infraestrutura de reflexão com tempo gasto com a adição de um processo SystemC vazio. A implementação proposta também não altera o tempo de simulação interno do SystemC. Quando insere-se o módulo de reflexão na simulação, a penalidade no tempo total gasto na execução da simulação não interfere na temporização interna SystemC, não refletindo portanto na análise temporal dos modelos.

- O mecanismo deve **ser expansível**. Conforme se mostra, derivam-se dois trabalhos diferentes do mecanismo, mostrados no Capítulo 4 e na Seção 3.5.

- O mecanismo deve prover observabilidade e controlabilidade. A introspecção deve ser nos dois sentidos (leitura e escrita de valores). Parece óbvio, mas os trabalhos relacionados que utilizam programação orientada a aspectos não conseguem injetar sinais nos módulos.

- O mecanismo deve proteger a propriedade intelectual do módulo sob verificação. Os fornecedores de módulos somente devem ser obrigados a revelar informações suficientes sobre o seu produto para permitir sua utilização e verificação.

# Capítulo 3

# Introspecção em Plataformas SystemC

Neste capítulo, discutimos um mecanismo baseado em reflexão computacional que torna possível que os desenvolvedores interajam com a simulação da plataforma, durante a execução. Este mecanismo permite que os projetistas monitorem e mudem os sinais ou até mesmo os valores armazenados nos registradores internos dos IPs, de forma a explorar, em um alto nível de detalhamento, o que está realmente acontecendo em cada módulo da plataforma. A idéia foi originalmente introduzida em [2], cujo desenvolvimento apresentamos neste trabalho.

Um dos objetivos do que chamamos de metodologia de introspecção é aumentar a capacidade do desenvolvedor de testar os casos extremos, melhorando assim a cobertura funcional das verificações executadas, sem que para isso seja preciso modificar os módulos de descrição de *hardware* ou o código da biblioteca SystemC, bem como preservar a liberdade na escolha do compilador e do ambiente de execução.

## 3.1 Depuração e Verificação de Modelos em SystemC

SystemC é basicamente composto de um núcleo de simulação e uma biblioteca com estruturas e tipos de dados que representam as estruturas mais comuns em *hardware*, como sinais, portas de comunicação (registradores expostos), vetores de bits, etc. Estes tipos são disponibilizados através de bibliotecas escritas em C++, com a infraestrutura de orientação a objetos normalmente encontrada neste paradigma, como a hierarquia de classes, suporte a heranças e especialização (sobrecarga). Com esta infraestrutura, os usuários de SystemC escrevem os seus próprios modelos, que geralmente são organizados em uma hierarquia composta por vários módulos SystemC interligados entre si de modo a formar uma especificação executável do sistema sendo modelado. Através desta especificação,

espera-se que o desenvolvedor possa simular o sistema descrito, de acordo com o nível de abstração utilizado (ex.: simulação funcional ou comportamental, com precisão de ciclos anotada ou simulada, etc).

Os problemas surgem quando o desenvolvedor precisa depurar um módulo escrito em SystemC com as ferramentas de depuração existentes para C++, como GDB, durante o desenvolvimento do seu módulo de hardware. Projetistas de hardware não estão interessados nos detalhes internos de implementação do SystemC, mas sim na descrição do modelo que estão trabalhando no momento. As ferramentas para depuração de código C++ não são capazes de distinguir entre a descrição de hardware em si e o código interno do SystemC, tornando a depuração uma tarefa árdua e susceptível a erros. Mesmo se compilarmos o SystemC sem suporte a depuração, cada operação onde um dos parâmetros é um tipo de SystemC irá gerar códigos que não interessam ao projetista de hardware, que serão interpretados pelo depurador como trechos sem código fonte. A troca de contexto intrínseca do modelo de simulação baseado em eventos usado no SystemC também atrapalha. Ao depurar uma simulação com diversos processos SystemC, o projetista se depara com um único fluxo de execução serializado, sem diferenciação clara entre os processos.

Estas particularidades explicam por que as ferramentas de depuração especializadas em SystemC são praticamente imprescindíveis para que se possa acelerar o ciclo de desenvolvimento dos projetistas de *hardware* que usam SystemC. O problema piora quando temos um projeto baseado no conceito de plataforma, dado que estas podem conter vários módulos complexos em SystemC ligados uns aos outros, incluindo a utilização de módulos específicos para isso. Nestes casos, a tarefa de depuração não se restringe aos módulos isolados, mas também inclui a comunicação entre eles, seja diretamente ou indiretamente, através de uma estrutura de interconexão (um módulo descrevendo um barramento, uma rede, um roteador, etc).

A técnica que apresentamos aqui não só cobre esta lacuna como o faz sem intervenção alguma no código da biblioteca SystemC ou do usuário. Além disso, não é necessário nem mesmo o código fonte do módulo, desde que o arquivo de cabeçalho dos módulos nos quais será aplicada a introspeção seja fornecido junto com o binário correspondente.

## 3.2 Por que a Reflexão Computacional?

Reflexão computacional é a habilidade de um sistema de observar e modificar a si mesmo. No domínio do *software*, a reflexão é usada para conseguir otimizações de desempenho, por meio de automodificações realizadas pelo programa em tempo de execução, ou para adaptar dinamicamente um sistema a situações específicas. A linguagem Java, por exemplo, possui um mecanismo nativo de reflexão que permite a escrita de um trecho de código genérico, que possa receber instâncias de mais de um tipo de objeto, não conhecidas em

tempo de compilação. Através da reflexão computacional, é possível identificar a classe do objeto em tempo de execução e tomar a decisão de invocar diferentes métodos de acordo com o tipo do objeto recebido.

A reflexão pode ser classificada como estática ou dinâmica, dependendo do mecanismo usado para gerar as estruturas de dados adicionais necessárias à reflexão [10]. A reflexão estática pode ser usada por compiladores para realizar otimizações de memória. Neste tipo de reflexão, o compilador analisa o código em tempo de compilação, gerando estruturas que facilitem o acesso às instâncias dos objetos (ex.: a desalocação da área de memória ocupada por uma instância de objeto, depende da invocação do método de destruição implementado pelo objeto, cujo endereço relativo pode ser calculado por meio de reflexão estática). A reflexão é mais comum na sua forma dinâmica, cujo suporte, quase na sua totalidade, é intrínseco à linguagem. Java, C#, Python, Ruby e Smaltalk são exemplos de linguagens de alto nível com suporte nativo à reflexão computacional.

Mas por que estamos tão interessados em usar a reflexão computacional em um ambiente de desenvolvimento de plataformas de alto nível como SystemC?

Uma das características principais que desejamos na concepção da metodologia de introspecção apresentada neste trabalho é a não intrusividade: os desenvolvedores de IPs não deveriam saber que seus modelos serão inspecionados, significando que deveriam descrever o IP da mesma forma que o fariam se o mesmo não fosse submetido à introspecção.

Mais que isso, queríamos que fosse possível inspecionar, usando o mecanismo de reflexão, os IPs cujo código-fonte possa não estar disponível. Isto parece estranho à primeira vista, porém com a adoção das descrições em alto nível, acreditamos que o mercado de IPs "de prateleira" se desenvolva, tornando possível que um projetista opte por comprar um IP ou parte dele, adequando-o se necessário. De fato, isto vem acontecendo com o mercado de IPs descritos em baixo nível (RTL). OpenCores é um repositório de IPs de código aberto, onde se pode encontrar diversos IPs de prateleira, prontos para uso. No caso deste repositório, é possível se obter todo o código fonte, dada a natureza de código aberto do projeto. Porém, em um cenário comercial, é comum que o vendedor não exponha sua propriedade intelectual, fornecendo apenas uma especificação executável do IP, podendo inclusive ser criptografada, e o código fonte da interface para utilizá-lo.

Estes requisitos inviabilizam a utilização da reflexão estática ou qualquer método que necessite de anotação por parte do usuário (onde o mecanismo de reflexão ou o código fonte devem ser reescritos para cada IP). Uma observação importante é que as técnicas de programação orientada a aspectos podem ser uma alternativa interessante para possibilitar a introspecção de dados [7], mas com a desvantagem de que necessitam de uma mudança no paradigma de programação ao qual os desenvolvedores de hardware estão acostumados. Cada módulo SystemC no qual deseja-se realizar a introspecção de dados deveria ser desenvolvido seguindo o paradigma de orientação a aspectos. Isto vai totalmente no

caminho contrário do nosso objetivo de minimizar a intrusividade. Além disso, o fato de obrigar os projetistas a gastar um tempo razoável aprendendo e alternando entre dois diferentes paradigmas de programação restringe seriamente a adoção desta alternativa. Pior ainda, todos os IPs existentes teriam que ser reescritos para que a técnica funcionasse.

## 3.3 Introspecção em Módulos SystemC

Nesta Seção, mostraremos como tornamos possível a introspecção de dados em módulos SystemC através de uma biblioteca externa de reflexão. No nosso caso, escolhemos a biblioteca Reflex-SEAL [29], desenvolvida pelo CERN com parte do projeto ROOT. Os principais aspectos que nos levaram a escolher esta biblioteca são:

- a biblioteca não é intrusiva, não necessitando de nenhuma modificação na descrição do módulo para que a introspecção seja aplicada;

- provê um roteiro de extração de metadados semi-automático, onde um esqueleto da classe do objeto é gerado em uma descrição XML intermediária pelo próprio projetista, através de um programa externo, de código aberto;

- não necessita de dependências adicionais para gerar a especificação executável (exceto pela biblioteca em si);

- não necessita de modificações no compilador e não é dependente de algum compilador específico.

O software utilizado para gerar o ambiente de reflexão é composto por:

- GCC 4.4.x

- SystemC 2.2.0 (TLM 2.0)

- Reflex SVN r32289

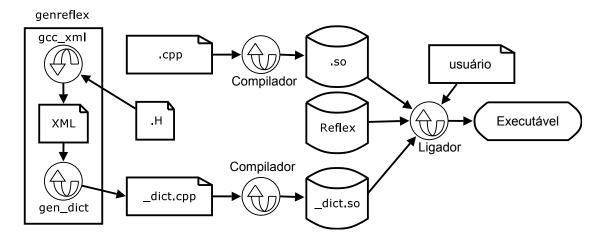

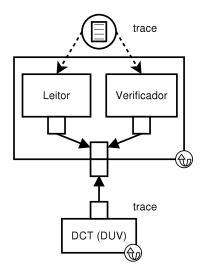

A Figura 3.1 mostra o fluxo de construção de uma especificação executável, com reflexão habilitada para um módulo SystemC, usando as ferramentas da biblioteca. Os passos necessários basicamente são três: extração de metadados, compilação e ligação (do inglês, linking).

A extração dos metadados é feita através de um *script* chamado **genreflex** e é composta de duas fases. A primeira utiliza o GCCXML, um programa de código aberto e parte do conjunto de ferramentas do compilador GCC, para ler o código fonte do arquivo que descreve a interface do objeto, chamado de arquivo de cabeçalho (.h ou .H, do

Figura 3.1: Fluxo de reflexão usando a biblioteca Reflex-SEAL

inglês header). A saída deste programa é uma estrutura XML equivalente ao objeto e é utilizada sem modificações. Na segunda fase, este arquivo XML é processado e gera-se um arquivo de dicionário compilável, contendo informações sobre a estrutura do objeto refletido, como o endereçamento relativo e tipo dos atributos e métodos. Toda a coleta de informações é feita antes da compilação da simulação e somente precisa ser feita uma vez para cada módulo a ser refletido. Note que o fluxo mostrado na Figura 3.1 não recebe nenhum arquivo de código fonte (.cpp ou .C). Além disso, nenhuma anotação no código se faz necessária para a utilização da metodologia.

O dicionário é importante para os programas que usam os dados refletidos. Usando os métodos disponíveis na biblioteca de reflexão, toda a representação da estrutura do objeto refletido pode ser lida e usada. Normalmente, somente o ponteiro para a instância do objeto a ser refletida é suficiente para as operações de reflexão. Na prática, o que se faz é utilizar o dicionário como uma máscara. Esta máscara representa o objeto em si, portanto a diferença (offset) entre o endereço base e qualquer atributo também é a diferença entre o ponteiro da instância e o atributo correspondente. Tendo o ponteiro para para a instância do objeto a ser refletido, podemos aplicar a máscara proveniente do dicionário sobre a região de memória que contém a instância do objeto, de modo a acessá-la em tempo de execução sem que qualquer parte da plataforma tome conhecimento que estamos realizando esta operação. Considerando o cenário de projeto de plataformas, estamos especialmente interessados em inspecionar os atributos dos objetos em SystemC, de modo a permitir sua leitura e escrita. É possível, também, realizar chamadas aos métodos e funções não virtuais do módulo, porém não estamos interessados nesta habilidade aqui.

Após a coleta de informações através da análise da representação intermediária XML, a compilação e ligação seguem os passos que seriam realizados se a reflexão não fosse aplicada. Na Figura 3.1, o código que fará a introspecção em tempo de execução, aplicando a

máscara do dicionário e interagindo com o projetista, está incluído no conjunto de programas inseridos pelo usuário, junto com o restante da plataforma. Este programa, assim como o módulo a ser refletido, deve ser ligado à biblioteca de reflexão, ao dicionário de dados e à biblioteca SystemC. O executável produzido na saída é um simulador SystemC da plataforma, capaz de realizar a introspecção para ajudar no processo de depuração e verificação.

SPIRIT é um consórcio criado com o objetivo principal de estabelecer um meio de troca de informações de IPs padrão entre as diversas empresas de EDA. As meta-descrições especificadas pelo padrão SPIRIT permitem que qualquer ferramenta seja capaz de ler de uma forma padronizada todas as informações necessárias para automaticamente importar, exportar e até mesmo compilar qualquer módulo de hardware descrito tanto em uma linguagem de baixo nível como em SystemC. Uma das notações padronizadas consistem em uma descrição XML que define WhiteBoxes como uma ferramenta de introspecção com capacidade de inspecionar, observar e depurar outros módulos. Apesar de os WhiteBoxes serem cobertos na especificação padrão, o consórcio SPIRIT não especifica como os WhiteBoxes devem ser implementados, mas sim suas funcionalidades. Sendo assim chamamos nossa implementação de WhiteBox inspirada no SPIRIT de ReflexBox.

Um módulo de hardware escrito em SystemC pode ser visto simplesmente como uma classe escrita em C++. O conteúdo dos registradores, as entradas, saídas e qualquer outro dado que possa ser de interesse para a introspecção de dados são armazenados como atributos de objetos ou variáveis. Este é exatamente o tipo de informação que podemos obter com a reflexão computacional. A implementação do ReflexBox consiste em um módulo SystemC que possui um atraso nulo e se comunica com o mundo exterior através de um protocolo simples, expondo um socket para conexão. Apesar de ser um módulo SystemC, e se comportar como tal, um ReflexBox não pode ser acessado por nenhum outro módulo de SystemC pois não possui interfaces expostas para núcleo de simulação SystemC. Quando o ReflexBox é escalonado pelo escalonador do SystemC, utiliza os dicionários disponíveis para aplicar a introspecção sobre a instância do objeto alvo da reflexão (outro módulo de SystemC), de modo que possa realizar as tarefas que a ele forem solicitadas através da conexão externa, um socket exposto, onde o usuário deve conectar-se em tempo de execução.

O ReflexBox é genérico o suficiente para inspecionar qualquer tipo de módulo SystemC. Cada módulo ReflexBox está amarrado a um módulo de SystemC através da instanciação do ReflexBox, que leva como parâmetro um ponteiro para o objeto a ser refletido. Um ReflexBox pode refletir apenas uma instância de um módulo SystemC, porém uma plataforma pode ter quantos módulos ReflexBox forem necessários. Contudo, por motivos óbvios, não é possível refletir estruturas que não são conhecidas em tempo de compilação ou possuem formato criado pelo usuário (ex. uma união (union) ou estrutura (struct)).

Em nossa implementação, procuramos deixar o código pronto para adaptações caso seja necessário refletir tais objetos.

Apesar de o ReflexBox ter a capacidade de refletir métodos, esta característica é pouco utilizada em descrições de hardware. É possível invocar qualquer método de uma classe (ex.: uma função em um módulo SystemC), interativamente, em tempo de execução. Esta característica, por exemplo, pode ser usada para inspecionar um registrador criptografado, invocando-se a função decriptográfica sobre o dado contido no registrador durante a depuração do módulo, com o propósito de visualizar o valor descriptografado. A restrição na utilização se deve à necessidade de conhecimento prévio das tarefas que cada método realiza (o ReflexBox lista todos os métodos disponíveis), incluindo possíveis efeitos colaterais que o método invocado pode gerar, como mudanças no estado interno do módulo.

Na primeira vez em que um ReflexBox é escalonado para execução, gera-se uma lista interna dos atributos refletíveis e permite-se que o usuário informe que atributos deseja refletir no módulo, colocando marcações em cada um. Com isso, o usuário pode selecionar quais atributos são de interesse evitando a reflexão dos que não forem selecionados. Além disso, o usuário pode especificar qual é o interesse, gerando por exemplo um breakpoint, que irá parar a simulação quando uma determinada condição for atingida ou até mesmo instruindo o ReflexBox a somente registrar qualquer mudança de valor do atributo. Quando uma condição que interrompe a simulação é atingida, o usuário é capaz de observar o valor em questão, interagir com a plataforma alterando seu valor ou solicitar que a execução continue sem alterações. Lembramos que o ReflexBox possui um atraso nulo, significando que parar a simulação através dele não avança o tempo de simulação. O escalonamento do ReflexBox deve ser feito de uma forma que o mesmo possa inspecionar o módulo refletido a cada ciclo de simulação onde o módulo alvo possa modificar o seu estado. Isto pode facilmente ser conseguido definindo-se a lista de sensibilidade do Reflex-Box como sendo igual à do módulo a ser refletido, garantindo-se assim que o ReflexBox será executado toda vez que o IP também o for.

Na próxima seção apresenta-se um estudo de caso detalhado, ilustrando todos os passos necessários para incluir o módulo ReflexBox na simulação, de forma a aplicar a metodologia de reflexão na plataforma e assim tornar possível a sua introspecção.

# 3.4 Depurando uma Plataforma Exemplo Através de Simulação

A plataforma exemplo roda uma versão modificada do decodificador de MP3 dist10. Este código fonte é parte do conjunto de software de referência da divisão MPEG da ISO. Foi a última distribuição padrão para o MPEG-1 e MPEG-2, porém suporta MPEG-3 sem

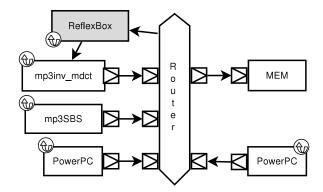

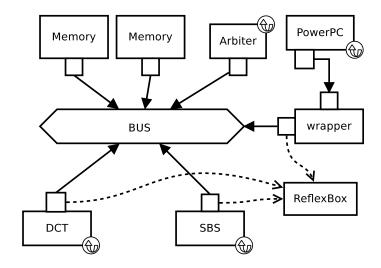

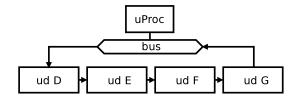

otimizações de desempenho nem qualidade. Usamos este algoritmo por se tratar de um código de referência que pode ser obtido na internet (veja Capítulo A). As modificações que fizemos são: a) o decodificador sempre usa os mesmos nomes de arquivo de entrada e de saída, para simplificar o acesso aos mesmos por parte do processador; b) a cadeia de decodificação MP3 foi dividida em duas partes, de forma que agora é possível rodar o algoritmo em um esquema de double buffering usando dois processadores. A estrutura geral do exemplo é mostrada na Figura 3.2.

O núcleo principal de processamento é composto por dois simuladores de processador PowerPC, modelados na linguagem ArchC, cada um executando metade da cadeia MP3. A memória foi particionada em três blocos, permitindo que os IPs sejam mapeados em memória nos endereços entre os três blocos de memória. Entre cada bloco de memória, deixamos propositalmente um espaço de endereçamento em aberto, suficiente para endereçarmos todos os registradores dos IPs.

Os dois IPs implementam funções selecionadas da aplicação original, simulando em hardware o que era feito no software original. A seleção das funções foi feita por meio de profiling do software MP3 utilizando o gprof [13]. Após rodarmos o software na plataforma, usando somente um processador para rodar o algoritmo todo e somente a primeira memória, obtivemos os dados estatísticos do software de profiling. No caso do desempenho, as melhores funções para serem transformadas em hardware são as que consomem o maior tempo de processamento e, dentre estas, as que estão mais perto das folhas na árvore extraída do grafo de chamadas de função. Uma função é considerada folha se ela é chamada por alguma função, porém não chama nenhuma outra. Isso garante que todo o trabalho realizado por esta função é realizado sem dependências externas, tornando-a uma forte candidata a ser transformada em hardware. No caso da transformação de uma função não-folha, deve-se optar por transformar todas as funções com chamadas subsequentes em hardware ou fazer a troca de contexto entre hardware e software. O tempo para a troca de contexto não é desprezível e deve ser levado em conta no cálculo do ganho de desempenho proporcionado pela realização da tarefa em hardware.

No nosso exemplo, foram selecionadas as funções SBS (Side Band Synthesizer) e IMDCT (Inverse Modified Discrete Cosine Transform). Estas duas funções somadas representam cerca de metade do tempo de processamento do algoritmo. Como transformaremos estas funções em hardware, retiramos as mesmas do software original e substituímos por um código que programa e dispara o IP. Programar os IPs significa escrever os valores de entrada nos registradores dos mesmos, o que nesta plataforma nada mais é que escrever em determinadas posições de memória, dado que os IPs são todos mapeados em uma única memória. Os IPs foram construídos de forma a realizarem as tarefas que lhe cabem somente quando receberem uma sinalização para tal, através de um valor pré-estabelecido escrito em registrador específico. Adotamos que um valor zero contido neste registrador

Figura 3.2: Arquitetura da Plataforma MP3 dist10 modificada

(chamado de registrador de controle) representa que o IP não está trabalhando. Quando o processador escreve um valor diferente de zero neste registrador, o IP lê os valores gravados nos registradores de entrada e começa o processamento. Quando termina, o IP escreve o resultado nos registradores de saída e escreve zero no registrador de controle, sinalizando que terminou a tarefa e está novamente disponível.

No nosso estudo de caso, escolhemos refletir o IP IMDCT. Para isso, temos três passos a seguir:

1. Gerar um arquivo de dicionário para o IP;

1

- 2. Instanciar um ReflexBox, o módulo que executará a introspecção de dados;

- 3. Compilar a plataforma para produzir uma representação executável.

Este processo de três passos supõe que a infraestrutura de *software* descrita no início deste capítulo (GCC, SystemC e a biblioteca Reflex-SEAL) já esteja instalada e funcionando. O primeiro passo, gerar o dicionário, é conseguido através da aplicação genreflex:

```

genreflex ac_tlm_imdct.h -I <path_to_includes>

```

Note que este processo não utiliza o código fonte, somente o arquivo de cabeçalho do módulo, neste caso o arquivo ac\_tlm\_imdct.h. O resultado esperado é um arquivo chamado ac\_tlm\_imdct\_rflx.cpp, que representa o dicionário para este IP. Este processo precisa ser repetido para cada IP a ser refletido e pode ser feito pelo fornecedor do próprio IP (neste caso ele deve fornecer o modelo executável do IP e do dicionário, acompanhado do arquivo de cabeçalho para que o projetista possa inserir o IP na sua plataforma). Na Listagem 3.3 pode-se ver uma amostra de uma das classes dentro do arquivo ac\_tlm\_imdct\_rflx.cpp. Repare que os membros da classe que representa o IP, ac\_tlm\_imdct, como target\_export, answer\_ready, e memory, podem ser identificados entre as Linhas 3 – 8.

```

1

//----Delayed data member builder for class ac_tlm_imdct

void __user__ac_tlm_imdct_db_datamem(Reflex::Class* cl) {

:: Reflex:: ClassBuilder(cl)

4

.AddDataMember(type_3877, Reflex::Literal("target_export"), OffsetOf(

5

__shadow__::__user__ac_tlm_imdct, target_export), ::Reflex::PUBLIC)

.AddDataMember(type_14947, Reflex::Literal("memory"), OffsetOf(

__shadow__::__user__ac_tlm_imdct, memory), ::Reflex::PRIVATE)

.AddDataMember(type_2510, Reflex::Literal("answer_ready"), OffsetOf(

7

__shadow__::__user__ac_tlm_imdct, answer_ready), ::Reflex::PRIVATE)

}

8

9

namespace {

10

struct Dictionaries {

11

Dictionaries() {

12

Reflex::Instance initialize_reflex;

13

14

__user__ac_tlm_imdct_dict();

15

}

~Dictionaries() {

16

type_5923.Unload(); // class user::ac_tlm_imdct

17

}

18

19

};

20

static Dictionaries instance;

}

21

```

Figura 3.3: Trecho do dicionário de dados para o IP ac\_tlm\_imdct

O segundo passo, a instanciação do ReflexBox, é realizado no arquivo (main.cpp, também conhecido como arquivo principal ou top-level). Este arquivo é o local onde o projetista instancia e conecta os módulos da plataforma, na configuração desejada para uma simulação específica (pode-se ter mais de um arquivo principal, representando diferentes configurações da plataforma). Como esperado, aqui também deve-se instanciar o ReflexBox responsável pela introspecção em tempo de execução do IP alvo, como ilustrado na Listagem 3.4. A instanciação do ReflexBox pode ser feita manualmente para cada IP onde deseja-se aplicar a introspecção, ou automaticamente para todos os IPs da plataforma, postergando a seleção dos módulos refletidos para o tempo de execução.

A Linha 8 contém a instanciação do IP. Para os propósitos deste exemplo, é suficiente saber que este IP é um módulo SystemC qualquer. Na Linha 11, declaramos um ReflexBox que está refletirá um IP alvo do tipo especificado pelo nome da sua classe, (ac\_tlm\_imdct), e será responsável pela instância determinada pelo endereço do objeto instanciado na Linha 8 (&imdct). O último parâmetro do construtor do ReflexBox é um número inteiro representando a porta que o ReflexBox deve escutar por uma conexão externa de forma a receber as instruções de introspecção.

```

1 int sc_main(int ac, char *av[]) {

2

sc_clock mclock;

3

powerpc ppc_proc1("ppc1"), ppc_proc2("ppc2");

4

ac_tlm_mem mem("mem", 8 * 1024 * 1024);

ac_tlm_router router("router");

6

ac_tlm_sbs sbs("sbs");

ac_tlm_imdct imdct("imdct");

8

9

//ReflexBox instantiation

10

whitebox <ac_tlm_imdct > reflexbox("reflexbox","ac_tlm_imdct",&imdct

11

,6000);

12

char *av1[] = {"dual_ppc.x", "--load=dual_mp3.x", "-A", "source.mp3",

13

"dest.aiff", ""};

int ac1 = 5;

14

char *av2[] = {"dual_ppc.x", "--load=dual_mp3.x", "-A", "source.mp3",

15

"dest.aiff", ""};

int ac2 = 5;

16

17

wbmp3sbs.clock(mclock);

18

19

ppc_proc1.MEM_port(router.target_export1);

20

ppc_proc2.MEM_port(router.target_export2);

router.MEM_port(mem.target_export);

21

router.SBS_port(sbs.target_export);

22

router.IMDCT_port(imdct.target_export);

23

24

ppc_proc1.init(ac1, av1);

25

26

ppc_proc2.init(ac2, av2);

27

ppc_proc1.set_instr_batch_size(1);

28

ppc_proc2.set_instr_batch_size(1);

29

30

31

cerr << endl;</pre>

32

sc_start();

33

34