### Universidade Estadual de Campinas Instituto de Computação

### Isaías Bittencourt Felzmann

A framework for modeling and simulation of approximate computing in hardware

Uma ferramenta para modelagem e simulação de computação aproximada em hardware

### Isaías Bittencourt Felzmann

## A framework for modeling and simulation of approximate computing in hardware

## Uma ferramenta para modelagem e simulação de computação aproximada em hardware

Dissertação apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação.

Thesis presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Master in Computer Science.

Supervisor/Orientador: Prof. Dr. Lucas Francisco Wanner

Este exemplar corresponde à versão final da Dissertação defendida por Isaías Bittencourt Felzmann e orientada pelo Prof. Dr. Lucas Francisco Wanner. Agência(s) de fomento e nº(s) de processo(s): FAPESP, 2017/08015-8

**ORCID:** https://orcid.org/0000-0003-3048-8310

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Felzmann, Isaías Bittencourt, 1992-

F349f

A framework for modeling and simulation of approximate computing in hardware / Isaías Bittencourt Felzmann. – Campinas, SP: [s.n.], 2019.

Orientador: Lucas Francisco Wanner.

Dissertação (mestrado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Computação aproximada. 2. Computação consciente de energia. 3. Arquitetura de computador. 4. Hardware - Linguagens descritivas - Métodos de simulação. I. Wanner, Lucas Francisco, 1981-. II. Universidade Estadual de Campinas. Instituto de Computação. III. Título.

#### Informações para Biblioteca Digital

**Título em outro idioma:** Uma ferramenta para modelagem e simulação de computação aproximada em hardware

### Palavras-chave em inglês:

Approximate computing

Energy-aware computing

Computer architecture

Computer hardware description languages - Simulation methods

**Área de concentração:** Ciência da Computação **Titulação:** Mestre em Ciência da Computação

Banca examinadora:

Lucas Francisco Wanner [Orientador] Antonio Carlos Schneider Beck Filho

Rodolfo Jardim de Azevedo **Data de defesa:** 28-02-2019

Programa de Pós-Graduação: Ciência da Computação

### Universidade Estadual de Campinas Instituto de Computação

### Isaías Bittencourt Felzmann

# A framework for modeling and simulation of approximate computing in hardware

## Uma ferramenta para modelagem e simulação de computação aproximada em hardware

### Banca Examinadora:

- Prof. Dr. Lucas Francisco Wanner IC/UNICAMP

- Prof. Dr. Antonio Carlos Schneider Beck Filho INF/UFRGS

- Prof. Dr. Rodolfo Jardim de Azevedo IC/UNICAMP

A ata da defesa, assinada pelos membros da Comissão Examinadora, consta no SIGA/Sistema de Fluxo de Dissertação/Tese e na Secretaria do Programa da Unidade.

Campinas, 28 de fevereiro de 2019

### Acknowledgements

The author greets and thanks everyone who somehow contributed and allowed this work to be completed: Lucas Wanner, Rodolfo Azevedo, Andressa Marchesan, Matheus Susin, João Fabrício Filho, Jonathas Evangelista, Marcelo Jara, Liana Duenha and every colleague at the Computer Systems Laboratory, family member or friend for their help, advice or company.

In particular, thanks to São Paulo Research Foundation (FAPESP) for the financial support (grant #2017/08015-8). Any opinions, findings and conclusions or recommendations expressed in this material are those of the author and do not necessarily reflect the views of the Foundation.

### Resumo

Pesquisas recentes têm introduzido unidades de hardware que produzem resultados incorretos de maneira determinística ou probabilística para um pequeno conjunto de entradas. Por outro lado, permitem um maior desempenho ou um consumo de energia significativamente menor em comparação com versões precisas das mesmas unidades. Como integrar, validar e avaliar essas alternativas em uma arquitetura ou processador, porém, permanece um desafio. A falta de ferramentas para representar e avaliar hardware aproximado leva desenvolvedores a verificar suas soluções de maneira independente, sem considerar interações com outros componentes, exigindo um grande esforço em modelagem e simulação. Neste trabalho, introduzimos ADeLe, uma linguagem de alto nível para descrever, configurar e integrar unidades de hardware aproximado em um processador. ADeLe reduz o esforço de desenvolvimento de hardware aproximado por modelar aproximações em um alto nível de abstração e injetá-las automaticamente em um modelo de processador para simulação arquitetural. Na ferramenta relacionada a *ADeLe*, aproximações podem modificar ou substituir completamente o comportamento de instruções de hardware através de políticas definidas pelo usuário. As instruções podem ser modificadas deterministicamente ou probabilisticamente (por exemplo, baseado em tensão de operação e frequência). Para proporcionar um ambiente de teste controlado, as aproximações podem ser ligadas e desligadas a partir do software em execução. O consumo de energia é automaticamente computado com base em modelos customizáveis no sistema. Assim, a ferramenta proporciona um método de verificação genérico e flexível, permitindo uma fácil avaliação da troca entre energia e qualidade de aplicações sujeitadas a hardware aproximado. Demonstramos a ferramenta pela introdução de variadas técnicas de aproximação em um modelo de processador, com o qual aplicações selecionadas foram executadas. Ao modelar módulos de hardware aproximado dedicados, mostramos como ADeLe representa unidades aritméticas aproximadas e unidades funcionais de precisão reduzida executando 4 aplicações de processamento de imagens e 2 de computação de ponto flutuante. Com outro método de aproximação, também mostramos como a ferramenta é utilizada para estudar o impacto de memórias alimentadas por tensão ajustável sobre 9 aplicações. Nossos experimentos demonstram as capacidades da ferramenta e como ela pode ser utilizada para gerar processadores virtuais aproximados e avaliar o equilíbrio entre energia e qualidade para diferentes aplicações com esforço reduzido.

### **Abstract**

Recent research has introduced approximate hardware units that produce incorrect outputs deterministically or probabilistically for some small subset of inputs. On the other hand, they allow significantly higher throughput or lower power than their error-free counterparts. The integration, validation, and evaluation of these approximate units in architectures and processors, however, remains challenging. The lack of tools to represent and evaluate approximate hardware leads designers to verify their solutions independently, not considering interactions with other components, demanding high-effort modeling and simulation. In this work, we introduce ADeLe, a high-level language for the description, configuration, and integration of approximate hardware units into processors. ADeLe reduces the design effort for approximate hardware by modeling approximations at a high level of abstraction and automatically injecting them into a processor model for architectural simulation. In the ADeLe framework, approximations may modify or completely replace the functional behavior of instructions according to user-defined policies. Instructions may be approximated deterministically or probabilistically (e.g., based on operating voltage and frequency). To allow for controlled testing, approximations may be enabled and disabled from software. Energy is automatically accounted for based on customizable models that consider the potential power savings of the approximations that are enabled in the system. Thus, the framework provides a generic and flexible verification method, allowing for easy evaluation of the energy-quality trade-off of applications subjected to approximate hardware. We demonstrate the framework by introducing different approximation techniques into a processor model, on top of which we run selected applications. Modeling dedicated hardware modules, we show how ADeLe can represent approximate arithmetic and reduced precision computation units executing 4 image processing and 2 floating point applications. Using a different method of approximation, we also show how the framework is used to study the impact of voltage-overscaled memories over 9 applications. Our experiments show the framework capabilities and how it may be used to generate approximate virtual CPUs and to evaluate energy-quality trade-offs for different applications with reduced effort.

# **List of Figures**

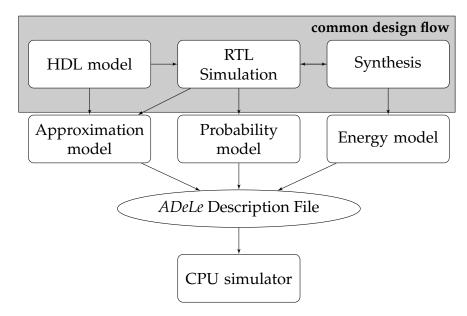

| 3.1  | ADeLe design flow showing how it affects the CPU simulator              | 18         |

|------|-------------------------------------------------------------------------|------------|

| 3.2  | Sample implementation of RandomBitFlip data modifier                    | 18         |

| 3.3  | ADeLe description of an adjustable supply voltage register bank         | 19         |

| 3.4  | Simulation control interface                                            | 20         |

| 3.5  | ADeLe description of half-precision FPU                                 | 21         |

| 3.6  | Example of a data modifier                                              | 23         |

| 3.7  | ADeLe description of Kulkarni's multiplier                              | 24         |

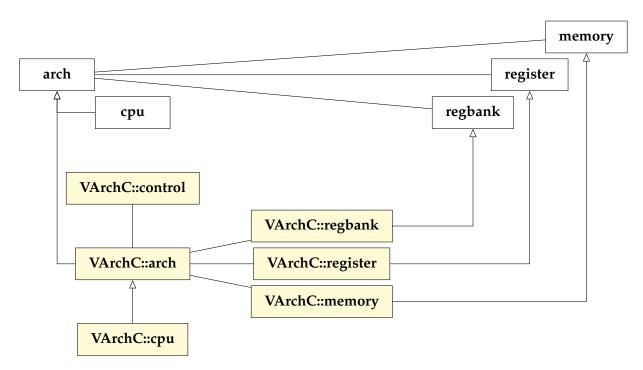

| 3.8  | Simplified class diagram of ArchC extension                             | 27         |

| 4.1  | ADeLe description of one EvoApprox8B instance                           | 30         |

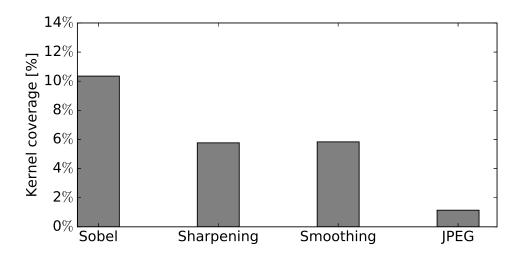

| 4.2  | Percentage of kernel multiplications approximated                       | 31         |

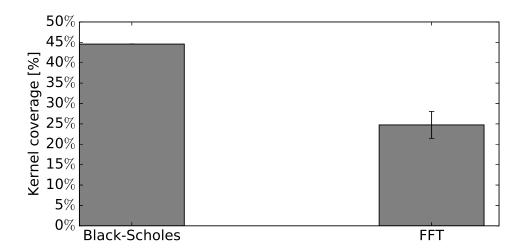

| 4.3  | Percentage of kernel floating point operations approximated             | 32         |

| 4.4  | Energy-quality trade-off of 32-bit multipliers                          | 33         |

| 4.5  | Peak Signal-to-Noise Ratio of computed images                           | 34         |

| 4.6  | Image Processing applications: Accurate and inaccurate multiplications. | 34         |

| 4.7  | Black-Scholes: Average relative error                                   | 35         |

| 4.8  | Fast Fourier Transform: Average relative error                          | 35         |

| 4.9  | Effect of approximations on average energy per instruction              | 36         |

| 4.10 | Relation between memory errors and energy                               | 37         |

| 4.11 | ADeLe description of one EvoApprox8B instance                           | 38         |

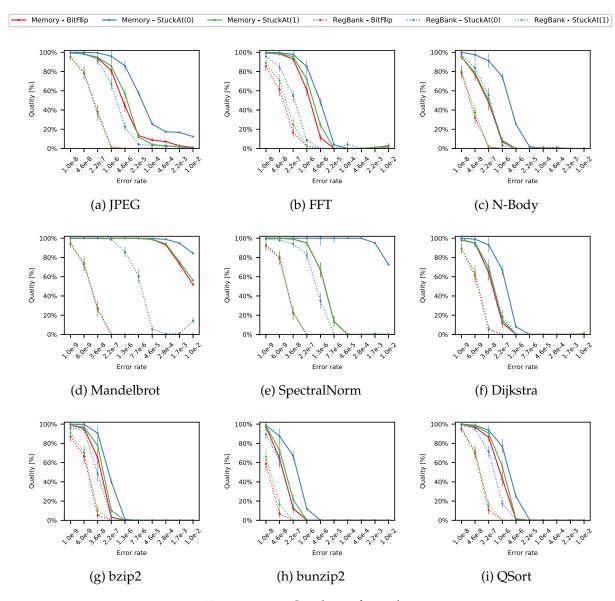

| 4.12 | Resilience analysis                                                     | 40         |

| 4.13 | Quality of results                                                      | 42         |

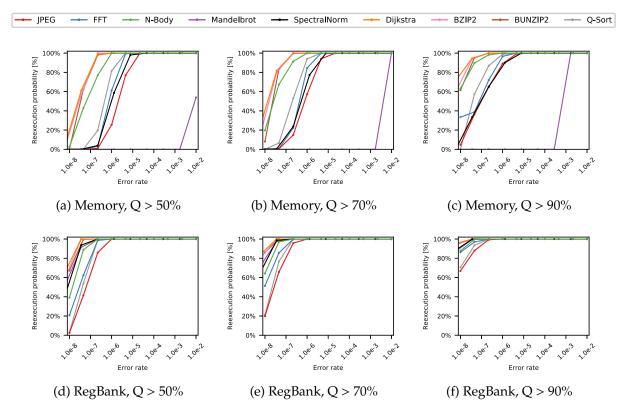

|      | Re-execution probability                                                | <b>4</b> 3 |

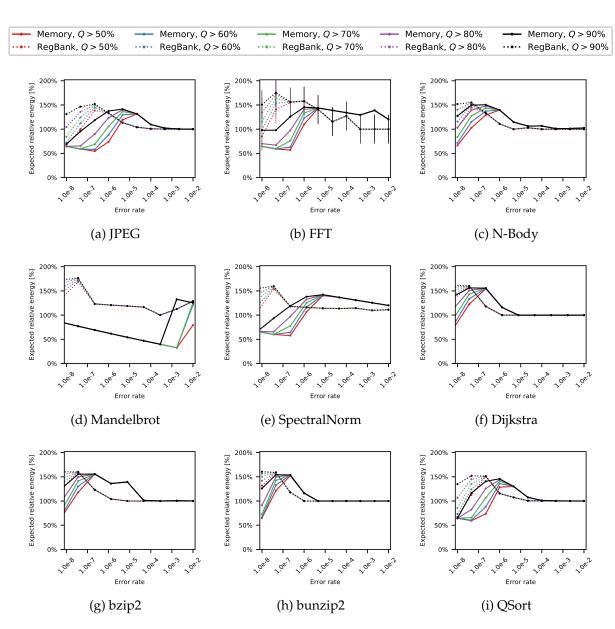

| 4.15 | Energy trade-off                                                        | 44         |

### **Contents**

| 1 | Introduction              |         |                                                    | 10 |  |  |

|---|---------------------------|---------|----------------------------------------------------|----|--|--|

| 2 | Rela                      | ated Wo | ork: Approximate Computing in the Dark Silicon era | 12 |  |  |

|   |                           |         | ware-level approximation techniques                | 13 |  |  |

|   |                           | 2.1.1   | Memory access approximation                        | 13 |  |  |

|   |                           | 2.1.2   | Inexact hardware                                   | 14 |  |  |

|   |                           | 2.1.3   | Voltage overscaling                                | 14 |  |  |

|   | 2.2                       | Mode    | ling techniques for Approximate Computing          | 15 |  |  |

| 3 | A Fı                      | ramewo  | ork for Approximate Computing                      | 17 |  |  |

|   | 3.1                       | The A   | DeLe Language                                      | 20 |  |  |

|   |                           | 3.1.1   | Approximation modeling                             | 21 |  |  |

|   |                           | 3.1.2   | Probability models (PM)                            | 23 |  |  |

|   |                           | 3.1.3   | Energy models (EM)                                 | 25 |  |  |

|   |                           | 3.1.4   | Operating parameters (OP)                          | 26 |  |  |

|   | 3.2                       | ADeLe   | e implementation into a CPU simulator              | 26 |  |  |

|   |                           | 3.2.1   | Software interface                                 | 27 |  |  |

| 4 | Demonstration and results |         |                                                    |    |  |  |

|   | 4.1                       | Under   | rdesigned hardware                                 | 29 |  |  |

|   |                           | 4.1.1   | Implemented approximations                         | 29 |  |  |

|   |                           | 4.1.2   | Selected benchmarks                                | 31 |  |  |

|   |                           | 4.1.3   | Results                                            | 32 |  |  |

|   | 4.2                       | Voltag  | ge-overscaled memories                             | 37 |  |  |

|   |                           | 4.2.1   | Implemented approximations                         | 38 |  |  |

|   |                           | 4.2.2   | Selected benchmarks                                | 38 |  |  |

|   |                           | 4.2.3   | Results                                            | 39 |  |  |

| 5 | Con                       | clusior | 1                                                  | 45 |  |  |

|   | 5.1                       | Produ   | action                                             | 16 |  |  |

### Chapter 1

### Introduction

Approximate computing has emerged as a promising solution to design issues in the Dark Silicon era [Esmaeilzadeh et al., 2011]. As power dissipation becomes the limiting factor for further increasing clock frequency on integrated circuits [Borkar and Chien, 2011], the exploration of an energy-quality trade-off can potentially allow further energy downscaling in comparison to traditional techniques. In addition to diverse software-based approximation approaches, the design of approximated hardware modules has attracted attention [Mittal, 2016; Xu et al., 2016]. The lack of specific tools for approximate-hardware development, however, increases the effort of validating and evaluating such hardware.

The common hardware design approach to develop approximate hardware modules typically consists in running input- and output-constrained circuit-level simulation to obtain energy and time metrics, followed by modeling the module behavior using a higher-level language or tool to estimate the quality of results. The results are then validated in a benchmark application substituting parts of the code for the behavioral model [Mittal, 2016]. In this method, the target application is explicitly changed to introduce the approximations, which lacks generality, given that applying the approximation in a different application may require extensive modification. Furthermore, architecture-level interactions between hardware modules may not be captured by modeling the behavior of approximate hardware at the application level.

Alternatives to higher-level software modeling include software instrumentation and architecture simulation. The latter has the advantage of generically representing the interaction between components in the target hardware and being transparent to the final application. Full-CPU simulators or emulators such as Wattch [Brooks et al., 2000], gem5 [Binkert et al., 2011], MARSS [Patel et al., 2011] and ArchC [Rigo et al., 2004] can model the process behavioral execution at varied detail levels, but lack a design framework to aid in the injection of hardware approximations.

In order to offer a reduced-effort method to model approximate architectures, we propose *ADeLe – The Approximation Description Language –* a high-level descriptive modeling language for hardware approximation, and demonstrate its use by injecting approximations into an off-the-shelf CPU model [Rigo et al., 2004]. The *ADeLe* abstraction focuses on representing approximations in a set of generic self-contained models designed to be automatically consumed by a CPU simulator, according to a high-level

description. Thus, the effort of validating a new approximation design is reduced to designing the models and the description file. *ADeLe* eliminates the effort of modifying a CPU simulator directly, and the models allow reuse in multiple target architectures. The method also embeds customizable energy models to estimate energy consumption, at the designer discretion, using abstractions of physical parameters that may influence in the simulation flow, and a flexible control structure to isolate resilient areas of the test application to be subjected to approximations.

In this work, *ADeLe* was implemented as an extension to the ArchC framework [Rigo et al., 2004] to show how it translates into simulation tools, allowing the execution of benchmark applications with minimal modification to the original source code, and the generation of comprehensive quality and energy consumption results. The *ADeLe* framework generates verifiable, uniform, reproducible, and reusable energy-quality results, and we show that by expanding known results to a set of different target applications. Moreover, the generic standardization herein proposed allows a fair and easier comparison of different approximation techniques, currently limited by the usage of incompatible or undisclosed modeling details and energy metrics [Mittal, 2016; Xu et al., 2016].

Thus, in this work, we summarize the following contributions:

- A high-level modeling language to describe how approximations affect an application at the architecture level;

- A framework to compile and translate the language in a simulation tool;

- A set of software models to represent common hardware approximations;

- A demonstration of how different applications behave when subjected to approximations.

The remainder of this text is organized as follows: In Chapter 2, we introduce the Approximate Computing paradigm and summarize related work on simulation techniques. The *ADeLe* language and its design flow is presented in Chapter 3, describing how to use it to model approximations. Our experiments demonstrating the language and the implementation applicability to model approximate hardware are described in Chapter 4, which includes descriptions of the selected hardware approximations modeled and benchmarks executed, as well as the results obtained. We conclude in Chapter 5.

### **Chapter 2**

# Related Work: Approximate Computing in the *Dark Silicon* era

For decades since the first microprocessor was conceived, the forecast exponential growth on the number of transistors [Moore, 1998] within a chip has been sustained by miniaturization [Dennard et al., 1974]. A smaller transistor can achieve a higher frequency which, when associated to microarchitecture developments and better memory systems, led to the exponential improvement in performance of computing systems overall [Borkar and Chien, 2011]. The Dennard model [Dennard et al., 1974] also defines a lower supply voltage in the scaling procedure. Although this resulted in better energy efficiency at first, the open-circuit leakage current increases exponentially the lower is the supply voltage [Borkar and Chien, 2011]. As a result, the power dissipated by the circuit increases to a point at which packaging and cooling techniques cannot handle [Shafique et al., 2014b].

This limitation in power dissipation forbids a chip to be used at its full capabilities for a long period of time. Thus, a significant part of the system runs at a lower frequency, or is even left powered off, in a situation often referred in the literature as *Dark Silicon* [Shafique et al., 2014a]. In a 22 nm architecture, the area affected by *Dark Silicon* exceeded in up to two times earlier forecasts [Esmaeilzadeh et al., 2011; Kapadia and Pasricha, 2017], and this amount is going towards 80% of the chip for recent manufacturing processes [Shafique et al., 2014b].

Despite being a waste of resources, leaving silicon dark does not necessarily improves power efficiency. Especially in many-core architectures, active computing cores should be kept at a distance from each other to maintain the temperature distribution within the chip and reduce their influence in one another. However, the longer the distance between the nodes, the further away data need to propagate, which increases latency, reduces performance, and negatively affects efficiency. Moreover, a longer and slower dataflow requires faster computation nodes to maintain throughput, resulting in more power dissipation [Yang et al., 2017; Kapadia and Pasricha, 2017].

Approximate Computing has been studied as an alternative design to improve power efficiency without negative effects in performance. Instead, Approximate Computing explores a trade-off between energy and quality, since many applications do not require computation to be exact and precise all the time [Kugler, 2015]. Recent studies

have shown how Approximate Computing techniques can achieve energy savings and improve power efficiency both in the software and hardware levels [Xu et al., 2016; Mittal, 2016].

Software-level Approximate Computing techniques include precision scaling, loop perforation, memoization, task skipping, and function replacement [Mittal, 2016]. They all have in common the intent of reducing computation time, thus reducing energy consumption but not power dissipation. These software techniques are usually specific to a target application and need to be redesigned to others. As a result, they achieve better controlled quality results and limited energy savings [Chippa et al., 2014].

The hardware-level techniques, on the other hand, affect a wider range of applications. These include replacing functional units by simpler ones or adjusting operating parameters, mainly supply voltage, below the nominal level. These modifications have direct impact on power dissipation and usually allow extended impact on the hardware by fine tuning the operating parameters, thus the energy savings are significant and extensible throughout the project [Chippa et al., 2014]. Their impact on quality, since they are not specific, however, can even be unpredictable in advance, thus requiring further evaluation and simulation for validation. The following sections present an overview of hardware-level approximation techniques (Sec. 2.1) and existing tools that allow such validation (Sec. 2.2).

### 2.1 Hardware-level approximation techniques

### 2.1.1 Memory access approximation

Load value prediction is a well known technique to minimize the cache miss penalty on a memory access. Miguel et al. [2014] followed this idea to create a load value approximation, a technique that augments prediction by not rolling back the application execution if a value is incorrectly predicted. Instead, the actual value read is only used to train the system and improve prediction quality. Furthermore, the data are not fetched from memory at every cache miss, but at a determined rate, saving energy on memory fetch. The study shows up to 8.5% better performance and 12.6% energy savings on average.

Similarly, Yazdanbakhsh et al. [2016b] also propose rollback-free value approximation, breaking the memory fetch process for each cache miss. The system is optimized for graphic processors, maintaining data consistency for all processing cores. The authors report 36% better performance and average 27% energy savings. Both Miguel et al. [2014] and Yazdanbakhsh et al. [2016b] used adapted simulation software to evaluate their designs. The former considers every memory read within a code region as a cache miss, computing the approximation, while the latter relates the memory reads with hot memory regions.

#### 2.1.2 Inexact hardware

Inexact hardware are modules developed, in logic level, to produce incorrect results at some determined input conditions, trading quality for energy and performance [Kahng and Kang, 2012]. The circuit is usually designed to reduce the critical path, allowing better performance and reducing energy consumption.

Kulkarni et al. [2011] propose an approximate multiplier hardware. The authors take advantage of the fact that there are only 8 possible products of 2-bit integers to create a module that outputs a 3-bit integer, instead of 4. In this concept, the result of the operation  $3 \times 3$  is 7, not 9. All the other possible products can be represented in a 3-bit integer, so the output is correct in 15 out of 16 possible input patterns. Besides, the multiplier can be connected to others, in a Wallace Tree topology, offering larger number multiplication. Moreover, the system was designed with a error correction mechanism to be used if the application demands. The statistical analysis shows that the multiplier can save up to 45% energy at an average calculation error in the order of 3%.

Kahng and Kang [2012] present the design of an approximate adder. In the project, the adder carry chain is sliced to reduce the circuit critical path, allowing it to operate in a higher frequency and use less area, thus reducing power dissipation. The authors describe how to set up the adder precision and a possible auxiliary circuit for error correction, if necessary. The results show up to 24.6% throughput and 37% energy savings in comparison with a regular exact adder.

EvoApprox8b [Mrazek et al., 2017] is a library of approximate hardware adders and multipliers evolved by genetic programming. The objective is to offer a common point of comparison for benchmarking approximate circuits, a library containing almost a thousand approximate implementations of commonly used hardware. The authors report energy and quality metrics, obtained individually, for each of the alternatives, and disclose high-level software and hardware description models for them.

The design projects of inexact hardware modules commonly use computer aided design to validate timing and power characteristics. This method, although necessary and very precise, limits the validation to a narrow set of operations, making it unlikely the test of a full application, let alone real-world applications. As alternatives, Kulkarni et al. [2011] and Mrazek et al. [2017] remodeled their designs in high level software, which allows for timely feasible verification but limits the representation of the designs in association with other modules in the architecture level.

### 2.1.3 Voltage overscaling

The Dennard model [Dennard et al., 1974] describes the relation between a transistor size, threshold and supply voltage and maximum operating frequency. As power is proportional to voltage, it is possible to reduce power dissipation by voltage reduction. The voltage is said "overscaled" when it is adjusted below the operating point, which causes timing and switching failures [Chippa et al., 2014]. Depending on the consequences of such failures and the resiliency of the application, in the context of Approximate Computing, they could be referred as approximations.

Voltage overscaling is the technique used by Chippa et al. [2014] and Rahimi et al. [2015]. The former uses the technique to approximate the adders in a multiply-and-accumulate (MAC) system, causing timing constraint violation and output errors. The authors employ overscaling in association with other techniques, and results show that the energy savings achieved by voltage overscaling alone are very similar to those perceived when other techniques are used together for smaller error tolerances. The larger the tolerance, however, the worse it performs when compared with the other, still achieving 50% energy savings over precise computation.

Rahimi et al. [2015] also use voltage overscaling in association with other techniques. They propose an auxiliary memory module at each Floating Point Unit of a graphics processor. This module stores data from common computations, avoiding them to be recomputed, a memoization technique. The auxiliary unit itself has the supply voltage overscaled, reporting average energy savings of 32%.

Both works by Chippa et al. [2014] and Rahimi et al. [2015] use integrated circuits design software to obtain the power characteristics of their propositions. To allow real-world simulation, Chippa et al. [2014] wrote their own dedicated system simulator, while [Rahimi et al., 2015] modified an existing GPU simulator to extract input patterns, without including simulation features of the designed module. In both cases, an architectural simulator would allow the modules to be integrated in the system, offering results validation in real conditions.

### 2.2 Modeling techniques for Approximate Computing

Modeling abstractions and methodologies have been proposed in both software [Sampson et al., 2011; Carbin et al., 2013; Sampson et al., 2015; Barbareschi et al., 2017] and hardware [Rahimi et al., 2013; Nepal et al., 2014; Yazdanbakhsh et al., 2015] levels. They enhance the design flow of a technique identifying target code or circuit areas that may benefit from approximation and providing a model of modifications. However, such methodologies, particularly the hardware-level ones, are focused on representing the approximations themselves in a self-contained fashion, with limited modeling of their integration in a target system. Their validation uses the typical methodology to validate custom-design hardware modules, which involves high-effort time-consuming Register Transfer Level simulation in *ABACUS* [Nepal et al., 2014] and *Axilog* [Yazdanbakhsh et al., 2015] or customization of a high-level simulation tool to represent the system [Rahimi et al., 2013].

Simulation or instrumentation can be used to estimate the final behavior of an application, when a hardware module is modified, in association with the rest of the system. Fault injection simulators are tools of consolidated research interest to represent possible modifications in a system [Hsueh et al., 1997; Kooli and Natale, 2014; Kooli et al., 2015]. In the context of Approximate Computing, consolidated simulators such as *FERRARI* [Kanawati et al., 1992], *DOCTOR* [Han et al., 1995], *FTAPE* [Tsai et al., 1996], *Xception* [Carreira et al., 1998], *FAUmachine* [Potyra et al., 2007] and *LIFTING* [Bosio and Natale, 2008] are some of the options to simulate approximations injection.

Application-directed fault injection simulators, however, typically work at application level. Thus, the injection is limited to each use-case application, sometimes requiring it to be individually modified, and the scope is usually limited to hardware regions directly accessed by the software, such as memory and storage locations. Moreover, such tools provide information of the computation result, but do not provide an interface to extract measurements such as energy, limiting the approximation analysis to quality of results.

Instrumentation tools such as *Pin* [Luk et al., 2005] can be used to inject approximations at the application level, usually for the same platform that runs the software. The *React* framework [Wyse et al., 2015] uses Pin to introduce approximations into multiple applications, some of them representing approximate hardware, and to account energy using a simplified linear model. The framework, however, does not provide a generic or flexible modeling method to represent approximations, limiting its coverage mostly to the provided models.

System simulators such as Wattch [Brooks et al., 2000], gem5 [Binkert et al., 2011] and MARSS [Patel et al., 2011] were already used by researchers to validate approximation techniques, although they do not offer a mechanism to directly modify the simulated hardware to inject approximations and are limited to a specific target architecture. The emulator QEMU [Bellard, 2005] has been used, in association with SystemC, as a virtual platform to represent a full system in hardware-software co-design [Monton et al., 2007; Yeh and Chiang, 2010; Chiang et al., 2011; Kleinert et al., 2016]. Thus, SystemC augments QEMU emulation capabilities adding customized hardware modules and creating a communication interface which allows high-performance emulation of fault-injected systems [Geissler et al., 2014; Ferraretto and Pravadelli, 2015; Höller et al., 2015]. The framework VarEMU [Wanner et al., 2013] extends QEMU with fault and power models to evaluate variability-aware software and supports the injection of faults into the emulated hardware. VarEMU and other QEMU-based techniques take advantage of binary translation to achieve high-performance verification. On the other hand, QEMU limits the representation of details in the architecture, such as multiple cores, thus the high performance comes at the expense of generality and control.

ArchC [Rigo et al., 2004], despite not performing as well as QEMU does to their target architectures, is an Architecture Description Language that can virtually represent any target system, allowing custom ISA extensions independently of any approximation injection mechanism. In association with SystemC Hardware Description Language support, ArchC can be expanded with custom functional units or peripherals at the designer discretion. The composition of ADeLe and ArchC as a framework provides a complete and general verification system, where ArchC represents a customized target CPU and its peripherals, and ADeLe handles approximation injection and approximation-aware simulation control, allowing full control and complete representation of the system in the verification process to designers.

### **Chapter 3**

# A Framework for Approximate Computing

The *ADeLe* language describes how approximations, associated with their energy models and probabilities, are injected into instructions in a CPU model. In this section, we describe a use case introducing the concepts and the approximation design flow using *ADeLe*. Our example targets a designer who wants to evaluate the impact of a new register bank design, powered by an adjustable supply voltage.

In the typical hardware development flow, the designer would model the hardware using a Hardware Description Language (HDL), evaluate it in a Register Transfer Level (RTL) simulator and synthesize it to obtain power and timing data, back annotating this information to the netlist for further simulation [Mittal, 2016]. At this point, the designer has data on how the register bank behaves under different voltage levels and characterization of soft errors when reading and writing data to certain locations, as well as their occurrence distribution [Tagliavini et al., 2017; Slayman, 2011; Calhoun and Chandrakasan, 2005]. In the context of Approximate Computing, errors under overscaled supply voltages may be seen as approximations that trade accuracy for energy savings in the computation [Chippa et al., 2014].

The HDL model and RTL simulation data alone cannot provide any information about how the new design impacts real applications. A CPU simulator may help in evaluating and validating the design, and its integration in a system. Nevertheless, extensive effort would be required to adapt the simulator in order to inject code that represents the faulty register bank, to develop a control mechanism that parameterizes it according to the supply voltage, and to aggregate the results of RTL simulation to represent energy metrics.

*ADeLe* proposes an enhanced design flow, summarized in Fig. 3.1, that eliminates the effort of modifying the CPU simulator source code directly. Taking, as inputs, a generic model of the approximation and a high-level description of how it interacts with the target CPU model, an *ADele*-compatible CPU simulator automatically modifies its execution flow to represent the approximated behavior.

The *ADeLe* design flow requires three *models*: the *approximation model* (Sec. 3.1.1) describes the black-box behavior of the approximation at instruction-level, in terms of its input data and output results; the *probability model* (Sec. 3.1.2) defines whether

Figure 3.1: ADeLe design flow showing how it affects the CPU simulator

```

void RandomBitFlip(source_t source, word &data) {

int bit = rand() % (8 * sizeof data);

data = data ^ (0x1 << bit);

}</pre>

```

Figure 3.2: Sample implementation of RandomBitFlip data modifier.

the described behavior should happen instead of the default execution behavior in the simulator; and the *energy model* (Sec. 3.1.3) computes how much energy was spent to execute the instruction, defined at the designer discretion.

In our use-case scenario described at the beginning of this Section, the designer would implement the approximation model as a method that takes as input the handled data and outputs it with some random modification, modeling the unexpected bit flips perceived during RTL simulation when the register bank is powered by a lower supply voltage [Calhoun and Chandrakasan, 2005] – in the *ADeLe* language, such an approximation model is called *data modifier* (Sec. 3.1.1). The sample in Fig. 3.2 illustrates the C++ implementation of a data modifier that flips a random bit in the data.

Similarly, the probability model uses the statistical fault occurrence distribution to determine whether an approximation is supposed to happen, given the applied supply voltage. Finally, the designer uses consolidated dynamic and static power models [Rabaey et al., 2002; Kim et al., 2003] to determine, in the energy model, the energy cost of each single instruction.

These models are generic and self-contained in the sense that they should not require nor use, by definition, any information specific to the target simulator or even to the target architecture. However, to represent the architecture and integrate all three models together, they share information encoded in a set of *operating parameters* (Sec. 3.1.4) that represent, for example, the current supply voltage, frequency and temperature of the system.

```

1 DM RandomBitFlip();

2 PM LowVddProbability();

3 EM DefaultEM();

OP default_op = {voltage = 1.0,

5

frequency = 400.0}; // MHz

6

7

OP low_vdd_op

= {voltage

= 0.8;

8

= DefaultEM();

energy

10 parameters = default_op;

11

approximation LOW_VDD_REGBANK {

12

= off;

13

initial

parameters

= low_vdd_op;

14

regbank_read = RandomBitFlip();

15

regbank_write = RandomBitFlip();

16

probability = LowVddProbability();

17

18 }

```

Figure 3.3: ADeLe description of an adjustable supply voltage register bank.

All models and operating parameters are related to each other and to the target architecture, at instruction level, using the *ADeLe Description File*. Being a bridge between the generic, self-contained models and the target simulator, this description file is the only part of the design flow that is written specifically for a target.

Fig. 3.3 exemplifies the *ADeLe* Description File that represents the adjustable supply voltage register bank as an approximation that affects all instructions in the ISA. Lines 1-3 declare the methods that implement the three required models: the approximation model, as a data modifier (DM), the probability model (PM) and the energy model (EM). Lines 5-7 define two sets of operating parameters that represent the regular CPU execution and a lower voltage – and low-power – state. The energy model and parameters that should be used to compute the energy cost in non-modified executions are set in lines 9,10. Finally, lines 12-18 define how the approximation itself is composed: all instructions are injected with the data modifier implementation when reading or writing to the register bank with the probability defined by the probability model. Moreover, when the execution is approximated, the target processor uses the lower voltage set of operating parameters, which affects energy computation, as well as the other models.

To enhance control of the final application execution, *ADeLe* defines that the approximations may be activated or deactivated at execution time, avoiding that non-error-resilient sections of the application are submitted to approximation. An *ADeLe*-compatible CPU simulator generates, after processing the description file, a library containing code to be included into the test application. This library defines a set of constants representing each approximation defined in the *ADeLe* Description File and control functions to interface with the CPU simulator control mechanism. Fig. 3.4 il-

```

data_t *data;

data_t *data;

data = acquire_data();

adele_activate(ADELE_APPROX_LOW_VDD_REGBANK);

data = computation_kernel(data);

adele_deactivate(ADELE_APPROX_LOW_VDD_REGBANK);

store_data(data);

```

Figure 3.4: Simulation control interface.

lustrates how a resilient computation kernel may be isolated from non-resilient data acquisition and storage operations, allowing just the kernel to be affected by approximations.

### 3.1 The ADeLe Language

The approximation representation proposed by *ADeLe* is composed of a set of models and a description file that relates them. The *ADeLe* Description File declares all the models to be injected into a CPU design, defines sets of operating parameters, groups instructions in the ISA to support approximation injection, and describes the approximations themselves. The model declarations (Fig. 3.3, lines 1-3) contain the signatures of the method implementations, prefixed with an identifier to classify them in approximation (DM or IM – Sec. 3.1.1), probability (PM – Sec. 3.1.2), or energy models (EM – Sec. 3.1.3).

The definition of operating parameters (Fig. 3.3, lines 5-7), identified by the *OP* keyword, is the main integration mechanism between models. Not all operating parameters in a set need to be explicitly defined, in which case *ADeLe* keeps the previous value of the given parameter unchanged. Sec. 3.1.4 details the operating parameters structure and its integration with the other models defined by *ADeLe*.

Regardless of whether approximations are activated in the final simulation, *ADeLe* requires the definition of a method to compute the energy spent by the simulated CPU regular operation. Thus, a default energy model and a default set of operating parameters need to be defined, such as exemplified in Fig. 3.3 in lines 9 and 10. These defaults are used at the beginning of the simulation and overwritten whenever an approximation that uses different configurations is activated.

Finally, the *ADeLe* Description File defines two types of groups: instruction groups and approximation groups. The instruction groups are arbitrary sets of instructions in the ISA that share some features in the description, for example, all floating-point instructions that deal with single-precision data may be subject to a different set of operating parameters that indicates that their energy cost is higher [Tong et al., 2000]. The example in Fig. 3.5 introduces the description of another approximation in which the CPU includes a Floating-Point Unit that adjusts itself to a lower-precision (IEEE

```

1 DM Float2HalfPrecision();

2 EM DefaultEM();

3

OP default_op = {voltage

= 1.0,

// V

4

frequency = 400.0}; // MHz

5

// Scalar

OP fpu_op

= {scaling

= 1.2};

6

// Scalar

7

OP half_fpu_op = {scaling

= 0.6;

= DefaultEM();

energy

10 parameters = default_op;

11

12 group SINGLE_FP { // Single-Precision Floating-Point

parameters

13

= fpu_op;

14

instruction = {add.s, sub.s, ...}; // List instructions

15 }

16

approximation HALF_PRECISION {

17

initial = off;

18

group SINGLE_FP {

19

regbank_read = Float2HalfPrecision();

20

21

regbank_write = Float2HalfPrecision();

= half_fpu_op;

22

parameters

}

23

24 }

```

Figure 3.5: *ADeLe* description of half-precision FPU.

754-2008 Half Precision [IEEE, 2008]) low-power state, in which an instruction group (lines 12-15) defines that floating point instructions spend more energy than the other ones in the ISA, using a scaling factor [Tong et al., 2000; Ho et al., 2017].

The approximation groups – or simply approximations – define and name the approximations injected in the CPU simulator themselves. Each approximation has a default state (Fig. 3.3, line 13 and Fig. 3.5, line 18) that indicates whether the given approximation is activated or not at the simulator startup. This state may be changed by the final application at simulation execution time, thus selecting areas of the application that are resilient to approximations. The defined approximations can be injected into all instructions in the ISA (Fig. 3.3), one or more of the previously defined instruction groups (Fig. 3.5), or to specific instructions, at each case all the models and operating parameters applied to the instructions are selected. This configuration tells the simulator at which point the execution flow needs to deviate to an approximated behavior.

### 3.1.1 Approximation modeling

The methods that define approximation models are divided into two categories: data modifiers, that model alterations in the data used by an instruction, and implementation

modifiers, that change the execution behavior of the affected instruction. Data and implementation modifiers are identified by the keywords *DM* and *IM*, respectively, and can receive arbitrary data as parameters to model the approximation.

#### Data modifiers (DM)

These are methods that receive data accessed by an instruction and can apply some modification in the data. Data modifiers can be applied to read or write operations on any data source in the target architecture. When using data modifiers, the instruction is executed without any knowledge that the data was modified. These approximations are injected into instructions using the set of keywords *source*, *source*, where *source* is the data source and *operation* is the data-handling operation. Fig. 3.5 exemplifies the inclusion of data modifiers in register bank read and write operations (lines 20 and 21). This approach can be used to model, for example, incorrect reads in the register bank due to voltage overscaling [Tagliavini et al., 2017; Slayman, 2011; Calhoun and Chandrakasan, 2005], data precision tuning [Ho et al., 2017; Sampson et al., 2011] and other memory access approximations [Miguel et al., 2014; Yazdanbakhsh et al., 2016b; Ganapathy et al., 2015].

The *ADeLe* description example in Fig. 3.5 declares the data modifier *Float2HalfPrecision* and then associates it with a group of instructions that contains all single-precision floating-point operations (lines 19-23), provided that the respective approximations are activated at execution time. The implementation of *Float2HalfPrecision* (Fig. 3.6) uses bitwise operations on floating-point values to read and write single-precision data as half-precision [IEEE, 2008]. Thus, the floating-point operations can be executed by the original models defined in the CPU modeling, but the results are taken as if the model had a half-precision floating-point unit.

A data modifier method implicitly receives a data structure containing information about the source of the data it is modifying and a reference to the data itself. The source of the data is encoded in a data structure containing the type of the data source (memory, register bank, special registers), the name of the data source (in case of multiple sources of the same type), the address of the data (in case of memory or register bank) and the operation being performed (read or write). This information may be used to determine whether the approximation should be applied to the data or not. In the data modifier illustrated in Fig. 3.6, for example, the data modifier is only targeted at the register bank called "RBF", representing a register bank dedicated to storing floating-point data. Thus, although all instructions that deal with floating-point data are affected by the approximation, only operations in the floating-point register bank are actually modified.

### Implementation modifiers (IM)

Instructions in the CPU model are usually represented as methods that implement their behavior, performing the action that the operation would execute on hardware. Implementation modifiers augment this behavioral description by adding code before

```

void Float2HalfPrecision(source_t source, word &data) {

if (source.type == REGBANK && source.name == "RBF") {

// Bitwise operations to convert data

data = BitwiseOps(data);

}

```

Figure 3.6: Example of a data modifier.

the original model (*pre-behavior*), after (*post-behavior*), or replacing completely the behavior by another function (*alt-behavior*). *AdeLe* associates implementation modifiers to instructions using the keywords *pre\_behavior*, *post\_behavior* and *alt\_behavior*, indicating the model that implements the approximation and its parameters, which are data objects available in the processor model scope, such as registers and register bank.

Alt-behavior models apply to dedicated hardware approximation techniques, such as approximate arithmetic [Lau et al., 2009; Kahng and Kang, 2012; Kulkarni et al., 2011; Camus et al., 2015; Mrazek et al., 2017], and floating-point [Lee et al., 2009; Camus et al., 2016b,a; Yin et al., 2016] modules, that replace (or replicate) functional units in the architecture by approximate counterparts, thus generating, in a modeling perspective, behaviors that are similar but cannot be represented solely by modifications in the data. Pre- and post-behavior models can be applied combined with alt-behavior, when some common procedure needs to take place before or after the approximation to better represent the results and support code maintainability, or individually, when the approximation affects operands or results and the instruction itself is executed following its original behavior, similar to a data modifier, but more specific to a single instruction.

The example in Fig. 3.7 injects Kulkarni's multiplier [Kulkarni et al., 2011] into integer multiplication instructions. The multiplier implementation receives the operand data from the register bank and references to the target registers where the product is written to. We took advantage of C++ method overloading to represent Kulkarni's method for both 32-bit and 64-bit (divided into halves) results, according to the MIPS ISA specification. Considering that Kulkarni's multiplier is unsigned, sign extension needs to be performed in order to correctly represent signed multiplication with signed operands, which is modeled as a post-behavior for the signed multiplication instruction (line 21).

### 3.1.2 Probability models (PM)

The method that implements a probability model, identified by the keyword *PM*, should return a boolean defining whether or not the approximation, at an instruction level, should take place. Probability models, as all other methods defined by *ADeLe*, have access to the operating parameters data structure, that can be used to determine the probability. For example, consider the function *LowVddProbability* in Fig. 3.3 (line 2): a lower supply voltage may increase the probability of a data-modifier approximation

```

1 IM Kulkarni(word a, word b, word &hi, word &lo);

2 IM Kulkarni(word a, word b, word &r);

3 IM SignExtend(word a, word b, word &hi, word &lo);

4 EM DefaultEM();

6 OP default_op = {voltage

= 1.0,

// V

frequency = 400.0}; // MHz

8 OP kulkarni_op = {scaling

= 0.7;

// Scalar

= DefaultEM();

10 energy

11 parameters = default_op;

12

13 approximation KULKARNI_MUL {

14

initial = on:

instruction multu {

15

alt_behavior

= Kulkarni(RB[rs], RB[rt], hi, lo);

16

parameters

= kulkarni_op;

17

}

18

instruction mult {

19

alt_behavior

= Kulkarni(RB[rs], RB[rt], hi, lo);

20

21

post_behavior = SignExtend(RB[rs], RB[rt], hi, lo);

22

parameters

= kulkarni_op;

23

}

instruction mul {

24

alt_behavior

= Kulkarni(RB[rs], RB[rt], RB[rd]);

25

parameters

= kulkarni_op;

26

27

}

28|}

```

Figure 3.7: *ADeLe* description of Kulkarni's multiplier.

affecting the register bank [Calhoun and Chandrakasan, 2005; Tagliavini et al., 2017], thus a function that accounts for supply voltage when rolling the dice to determine the occurrence may be implemented as the probability model for this approximation.

The probability model is coupled to an approximation using the keyword *probability*, which may be included either within the approximation group, when the same probability applies to all instructions that receive the approximation, or within an instruction block. Considering that probability models represent the likelihood of an approximation, they are not always required. While in the example of the adjustable voltage register bank (Fig. 3.3, line 17) the model decides if the lower supply voltage should affect the register bank operation at a given time, in the following half-precision FPU (Fig. 3.5) and Kulkarni multiplier (Fig. 3.7) examples, the occurrences are deterministic – the results are always approximated – and the probability model is not required.

### 3.1.3 Energy models (EM)

The methods that implement energy models, as defined by *ADeLe*, can take arbitrary parameters (such as a functional unit input operands), as well as the operating parameters, and return a number that represents, in Joules, how much energy one single instruction execution uses. Such flexible approach when computing energy allows designers to model their approximate circuits consumption at various levels of simplification. That is, the energy model abstraction can accommodate, but not be limited to, simplified models that assume every instruction to contribute equally and proportionally to the energy consumption [Tiwari et al., 1996; Guedes et al., 2013; Gupta et al., 2010; Jaiantilal et al., 2010], consolidated models that take into account physical variables such as voltage and frequency [Rabaey et al., 2002; Kim et al., 2003], common assumptions that energy is determined by the functional units involved in computation, disregarding control structures [Kulkarni et al., 2011; Camus et al., 2015; Kahng and Kang, 2012], or even fully customized models targeted at specific scenarios to represent precisely the energy consumption of a real system [Isci and Martonosi, 2003; Bertran et al., 2012].

Regardless of the chosen modeling approach, the reliability of the computed energy consumption resides on the model, and not in the abstraction proposed by *ADeLe*, and thus care must be taken to adequate and evaluate the model for the targeted scenario. At this point, *ADeLe* still contributes as a powerful tool, in a sense that models can be easily replaced at a high-level description and tested against multiple scenarios, at the designer discretion.

Energy models are declared using the *EM* keyword within the *ADeLe* description file. Models can be associated with instruction groups (where they are used for those instructions regardless of an active approximation), approximation groups, or approximated instructions, using the *energy* keyword. Considering that the simulator needs to compute energy for the whole execution, an energy model needs to be associated outside any groups, approximations or instructions in the description, and it is taken as the default energy model when no other is set.

### 3.1.4 Operating parameters (OP)

The operating parameters structure represent a collection of physical conditions in which the simulated processor is running, such as supply voltage, operating frequency, and temperature. The operating parameters represent the primary integration mechanism between all three types of models defined by *ADeLe*. For example, the voltage at which the CPU is running can be used to determine whether an approximation should happen, in the probability model, compute the energy used by the operation, in the energy model, and define what parts of the execution are affected and how, in the approximation model, affecting multiple implemented approximations at the same time [Mineo et al., 2016; Gautschi et al., 2016; Tagliavini et al., 2017; Calhoun and Chandrakasan, 2005].

Considering that operating parameters are dependent on the implemented approximations, they can also be changed at execution time. This can, for example, represent dynamic voltage-frequency scaling (DVFS) features in the simulated CPU and trigger, using probability and approximation models, different behaviors in the functional units due to overscaling [Chippa et al., 2014].

The operating parameters are declared using the *OP* keyword, and associated with groups of instructions (Fig. 3.5, line 13), approximations (Fig. 3.3, line 14), instructions (Fig. 3.7, lines 17, 22, 26), or as the default parameters using the *parameters* keyword.

### 3.2 *ADeLe* implementation into a CPU simulator

ADeLe was designed to represent approximations according to their behavior in the target architecture, resembling a functional simulator. To implement these concepts, we extended the simulation tools in the ArchC framework [Rigo et al., 2004] with the VArchC module, that allows the generation of ADeLe-compatible simulators. Based on the SystemC Hardware Description Language, the ArchC language generates processor models written in C++ by describing the behavior of each instruction in a customized software method, and thus ADeLe is a good fit for these models. Moreover, the integration with the ArchC framework allows the representation of other target architectures, by modeling them in the ArchC abstraction, and associated peripherals, in their SystemC description, creating an extensible and generic framework. Although ArchC is a convenient framework to represent a generic simulator, the proposed extension modifies common structures in functional simulators – the instruction decoder and storage accesses – and could similarly by applied to other simulators. Fig. 3.8 shows a simplified class diagram of a original ArchC CPU model and, highlighted, the VArchC extensions.

The ArchC Language describes processor models according to their structure and the behavior of the instructions. The structural information contains declarations for higher-level architecture characteristics, such as word size, number of words fetched from memory at each instruction, instruction formats, register bank size and memory connectivity. These provide the required information for a behavioral description of the instructions [Rigo et al., 2004]. Each instruction in the ISA is represented by a C++

Figure 3.8: Simplified class diagram of ArchC extension.

method describing the operations executed, which the simulator instruction decoder calls when the corresponding instruction is executed.

This model has a straight-forward relation with the modeling of implementation modifiers using *ADeLe*. The instruction decoder was modified to deviate from the instruction default behavior. It verifies whether an implementation modifier is activated for the given instruction, using internal control structures, and runs the probability model. If an approximation is activated for the given instruction, it dispatches function calls to pre-behavior, the default behavior, alt-behavior, and/or post-behavior accordingly, as well as to the energy model.

Storage structures, such as memories, register banks and dedicated-purpose registers in the architecture, are modeled, in ArchC, using specific C++ classes that implement their function. Then, each storage structure in the CPU model is represented as an instance of the class that models the respective structure. To inject data modifiers, we use approximation-enabled C++ classes that interface with the original storage classes, and use method and operator overloading to produce approximate reads and writes, calling the selected data modifier implementation method for each operation. This modeling approach is transparent to the original instruction behavior description, in a sense that data accesses are still performed the same way, not requiring any modification.

### 3.2.1 Software interface

ADeLe defines that approximation groups may be enabled or disabled at execution time, to isolate, in the application, regions that are resilient and more likely to benefit from the energy-quality trade-off. However, to allow such feature, a communication interface

was defined between the final application and the CPU model, controlling the internal structures that define which approximations are enabled for which instructions.

In the current ArchC-based implementation, this interface is defined through a memory-mapped hardware register. In the application side, an auto-generated library header defines a pointer to the hardware register and methods that allow control over the simulation, activating and deactivating approximations. The simulator recognizes that the application uses the hardware register and triggers the control subroutines whenever an instruction accesses the pointer.

The memory-mapped hardware register alternative has the advantages of being transparent to the final application and independent of architectural characteristics. However, since the control relies on memory operations in the application side, the control subroutine may be affected by approximations applied to memory operations. To avoid such unlikely situation, the *ADeLe* framework offers the alternatives of creating a dedicated instruction for control or using a set of existing instructions with pre-defined operands. These alternatives improve the simulation control, but may require further architectural modeling and compiler support in the application level.

### **Chapter 4**

### Demonstration and results

To demonstrate how the *ADeLe* framework can be employed in the validation of Approximate Computing techniques, we built two simulation scenarios. In the first one, *underdesigned hardware* (Sec. 4.1), we show how to model modified functional units in a processor, and how such modified hardware affects common applications [Felzmann et al., 2018b]. The second scenario, *voltage-overscaled memories* (Sec. 4.2), brings a adjustable-voltage memory architecture in which we show how various supply voltage levels affect the execution of multiple applications from various computing domains [Felzmann et al., 2018a].

We executed our experiments on an ArchC-generated MIPS processor model. The MIPS model (v. 2.4.0) and ArchC software (v. 2.4.1), both compiled with GCC 4.9.2, are available at the ArchC webpage. Benchmarks were cross-compiled using ELLCC v. 0.1.34, with target set to big-endian, hard-float 32-bit MIPS.

### 4.1 Underdesigned hardware

In *underdesigned hardware*, we use the *ADeLe* framework to simulate a processor that had two functional units, the hardware multiplier and the Floating Point Unit, replaced by approximate counterparts. The multiplier replacements were five selected alternatives from the EvoApprox8B library [Mrazek et al., 2017], over which we executed four image processing applications. The FPU was configured to operate in Half Precision [IEEE, 2008] to run two floating point applications. The results show significant error saving with negligible quality degradation for most individual cases.

### 4.1.1 Implemented approximations

Approximation techniques were selected to cover both integer and floating-point applications and model instruction and data modifiers. Due to their energy consumption, time restrictions and perceived resiliency to approximations we target multiplication and floating-point instructions [Kulkarni et al., 2011; Mrazek et al., 2017; Camus et al., 2016b; Yin et al., 2016].

```

1 IM Evo479 (word a, word b, word hi, word lo, bool sign);

2 IM Evo479 (word a, word b, word r);

3 EM SimpleEM();

OP default_op = {scaling = 1.0000};

5

OP evo479_{op} = \{scaling = 0.7005\};

7

8

energy

= SimpleEM();

parameters = default_op;

10

11 approximation EVOAPPROX_479 {

initial = off:

12

13

instruction multu {

alt_behavior = Evo479(RB[rs], RB[rt], hi, lo, false);

14

15

parameters = evo479_op;

16

}

17

instruction mult {

alt_behavior = Evo479(RB[rs], RB[rt], hi, lo, true);

18

19

parameters = evo479_op;

}

20

21

instruction mul {

22

alt_behavior = Evo479(RB[rs], RB[rt], RB[rd]);

parameters = evo479_op;

23

}

24

25 }

```

Figure 4.1: *ADeLe* description of one EvoApprox8B instance.

### **EvoApprox8b** multipliers

EvoApprox8b [Mrazek et al., 2017] is a benchmarking library of approximate 8-bit adders and multipliers evolved by genetic programming. The authors provide Verilog HDL descriptions and C models for all units in the library. We consider only the approximate multipliers, and built 32-bit modules from partial products using a Wallace Tree architecture. Energy savings were estimated using Cadence RTL Compiler over a baseline multiplier built completely from the tool optimization of a Verilog regular multiplication operation. The approximated multiplication instruction was represented as an implementation modifier, as illustrated in Fig. 4.1, which shows the representation of one multiplier instance in the library (479). The overloaded methods *Evo479()* build the Wallace Tree from multiple copies of multiplier instance 479 to allow 32-bit multiplication. The Energy Model *SimpleEM()* returns the scaling operating parameter as the instruction energy cost, thus providing a relative energy counter.

#### Single- to half-precision floating-point

Both operands and results of single-precision operations are converted to half-precision according to the IEEE 754 pattern [IEEE, 2008]. Tong et al. [2000] analyzed the energy

Figure 4.2: Percentage of kernel multiplications approximated.

consumption of multiple bitwidth floating-point architectures and reported 30% energy savings when using 16-bit operands and half-precision compatible significand fields. The approximated half-precision floating-point operations were represented as a data modifier, as described in the example in Sec. 3.1.1, Fig. 3.5.

### 4.1.2 Selected benchmarks

To represent the selected classes of approximations, applications on Image Processing – that usually rely on integer arithmetic, multiplication included – and floating point computation were selected and adapted from the AxBench [Yazdanbakhsh et al., 2016a] benchmark suite, as well as other freely distributed software. Image Processing applications were executed on 26 images from the USC-SIPI image database [SIP, 1997].

### **Image Processing**

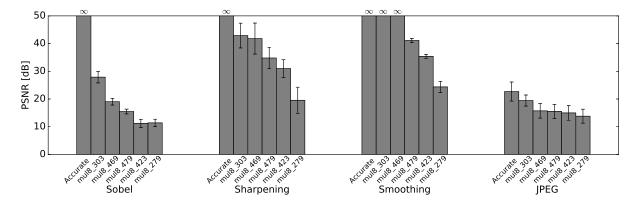

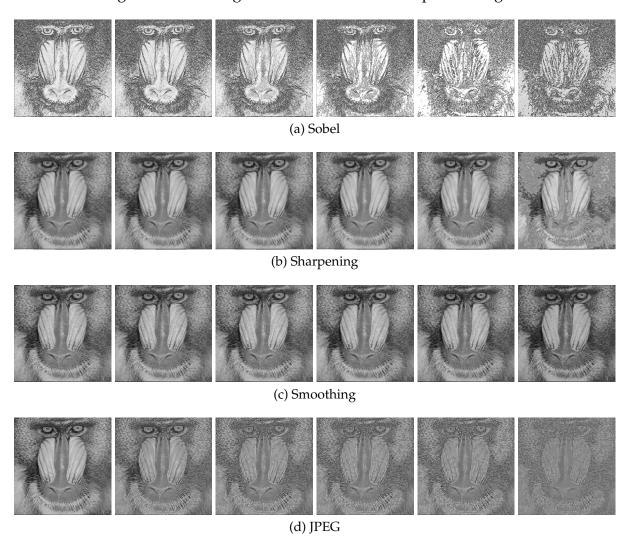

The selected Image Processing applications were the *Sobel edge detection* algorithm, as employed in [Wanner et al., 2013], the Gauss filter implementation for *Image Sharpening* and *Image Smoothing*, as described in [Lau et al., 2009] and [Kulkarni et al., 2011], and the JPEG compression algorithm from AxBench [Yazdanbakhsh et al., 2016a]. In the convolution-based algorithms (Sobel, Sharpening, and Smoothing), we replaced the multiplication in the convolution for selected approximate multipliers from EvoApprox8b [Mrazek et al., 2017]. For JPEG, AxBench provides additional information, in the source code, about which data structures are resilient to approximations, so we approximate all the multiplication operations where products were written to these structures. Fig. 4.2 shows the number of approximate operations relative to the application kernel. The resulting images for all approximate applications were compared with accurate executions using a usual Peak Signal-to-Noise Ratio (PSNR) metric.

Figure 4.3: Percentage of kernel floating point operations approximated.

### Floating-point

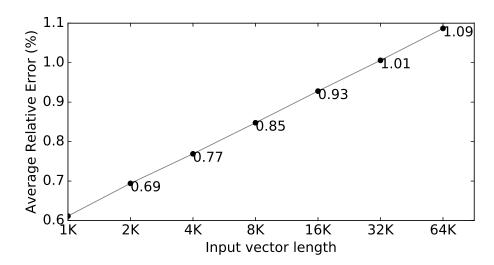

Two applications were selected from the AxBench [Yazdanbakhsh et al., 2016a] benchmark suite: *Black-Scholes* option price computing and *Fast Fourier Transform*. In both applications, we replaced all single-precision floating-point operations with half-precision operations (Fig. 4.3), truncating the operands with a data modifier as discussed in Sec. 3.1.1. Black-Scholes was executed over one thousand options, generated using the input generator from PARSEC [Bienia, 2011] suite, and results were evaluated according to the absolute error. The FFT execution was repeated 50 times over vectors of length 1K to 64K random values each, and results compared using the average relative error between the accurate (single-precision) and inaccurate (half-precision) computations.

### 4.1.3 Results

Applications were executed in the simulator in order to obtain the quality of results and relative energy consumption, comparing accurate and inaccurate computations. Except for the JPEG application, Image Processing applications showed resiliency to relative error rates on integer multiplication from 2% to 5%, allowing energy savings at a visually indistinguishable loss in quality. The floating-point approximation achieved higher instruction coverage than the integer one in the tested applications and thus exhibited a higher potential to save energy at low error rates.

### **Quality - Image Processing**

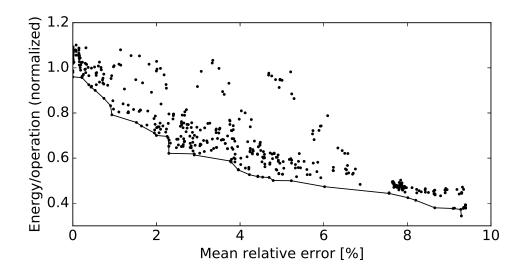

EvoApprox8b [Mrazek et al., 2017] is an extensive library, thus we selected a subset of the multipliers based on their theoretical, non-specific, energy-quality trade-off. After expanding the original 8-bit modules to 32-bit ones in a Wallace Tree organization, we used the software models distributed in the library to describe the same multiplier organization in software and evaluate the mean relative error for all multipliers, using an extensive uniform dataset. Fig. 4.4 shows the energy-quality trade-off for the mul-

Figure 4.4: Energy-quality trade-off of 32-bit multipliers.

| Multiplier | Mean relative error | Relative energy per operation |

|------------|---------------------|-------------------------------|

| Accurate   | 0.00%               | 100.0%                        |

| mul8_303   | 0.22%               | 95.68%                        |

| mul8_469   | 0.93%               | 79.19%                        |

| mul8_479   | 2.00%               | 70.05%                        |

| mul8_423   | 5.23%               | 49.97%                        |

| mul8 279   | 9.39%               | 39.30%                        |

Table 4.1: Selected EvoApprox8b multipliers.

tipliers, where energy per operation is normalized at the consumption of a multiplier fully optimized by the synthesis tool from the regular HDL multiplication operator.

At higher quality metrics, the approximate multipliers tend to have higher energy consumption than the baseline. This shows the energy overhead of associating multiple smaller multipliers to build larger ones. However, as quality decreases, it is clear that the architectures consume less energy, achieving savings of up to 60%. In addition to the baseline accurate multiplier, we selected the five multipliers that achieve the lowest energy consumption at given maximum error metrics, and ran the benchmark applications after modeling their behavioral description in our processor model. The selected multipliers are summarized on Table 4.1.

Fig. 4.5 shows the resulting image quality after computation. Except for the JPEG application, PSNR was calculated between the accurately computed image and the approximated one. For JPEG, the images were compared directly with the original uncompressed image. Fig. 4.6 demonstrates the image outputs.

The approximate multipliers performed particularly well in the algorithms based on the Gauss filter – Sharpening and Smoothing. Using *mul8\_303*, 10 out of 26 are identical to the accurately computed ones for Image Sharpening. For Image Smoothing, the results show that up to 1% mean relative error in multiplication has no effect on the resulting image. Higher error rates, despite lowering the PSNR, are still visually indistinguishable (Figs. 4.6b and 4.6c).

Figure 4.5: Peak Signal-to-Noise Ratio of computed images.

Figure 4.6: Image Processing applications: Accurate and inaccurate multiplications.

The other convolution-based algorithm, Sobel edge detection, despite presenting smaller Signal-to-Noise ratio than the Gauss-based ones, also showed some visual resiliency to approximations, as demonstrated in Fig. 4.6a. JPEG compression was the least resilient application (Fig. 4.6d), even though multiplication represents only 1.1% of the computation kernel (Fig. 4.2).

Figure 4.7: Black-Scholes: Average relative error.

Figure 4.8: Fast Fourier Transform: Average relative error.

### Quality - Floating-point

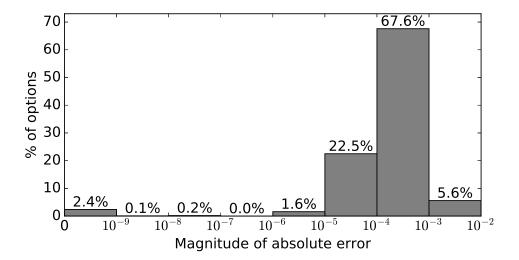

For Black-Scholes, approximations in floating-point instructions covered 44.6% of the instructions in the applications kernel (Fig. 4.3). The maximum absolute error observed was in the order of  $10^{-2}$ , and 2.4% of the options resulted in a value identical to the accurately computed ones. The majority (90.1%) was in an error range from  $10^{-5}$  to  $10^{-3}$  (Fig. 4.7). PARSEC's input generator [Bienia, 2011] just replicates the default 1000 options input set to generate larger ones and the modeled approximation is deterministic. Therefore, increasing the size of the input set has no effect on the quality of results.

In the Fast Fourier Transform application, the approximated floating-point instructions represent 24.8% of the application kernel (Fig. 4.3). All the approximate computations are in a range  $\pm 1\%$  relative to the accurately computed equivalents. Fig. 4.8 also shows that the relative error increases logarithmically with the size of the input set. The small relative error demonstrates the resiliency of FFT to this kind of approximation.

Figure 4.9: Effect of approximations on average energy per instruction.

### **Energy consumption**

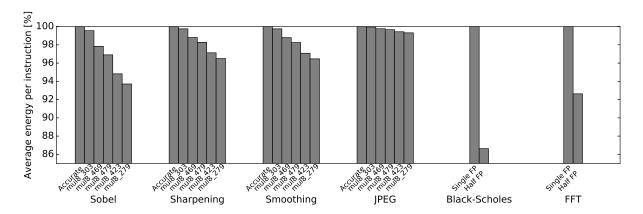

To compute energy, we use a simplified energy model that defines the energy consumption of all instructions as uniformly spent by the functional units used on computation, as an approximation for a scalar in-order microarchitecture [Guedes et al., 2013]. Thus, the energy savings in a single instruction is proportional to the savings in the executed operation, so the approximation lowers the average energy-per-instruction consumption of the application as a whole according to the approximation coverage in the computation kernel. Using *ADeLe*, this behavior is easily reproduced by changing the scaling operating parameter (Section 3.1.4). Although *ADeLe* can represent more complex and accurate energy models, we adopt such a simplified alternative for a plain comparison, considering it is commonly used in approximate hardware verification [Kulkarni et al., 2011; Camus et al., 2015; Kahng and Kang, 2012].

Fig. 4.9 shows how approximations affect the average energy per instruction relative to the accurate computation. As expected, the applications in which approximated instructions present higher coverages in the application kernel benefit more on energy savings, particularly the floating-point applications.

The Image Processing applications presented lower energy savings mostly due to the low coverage that multiplication instructions represent in the computation kernel. The convolutions nested loops impose a control overhead, lowering the relative number of calculations executed in the kernel. The multiplication operation itself, however, can potentially save up to 30% energy at a 2% mean relative error (Table 4.1). This suggests that more multiplication intensive applications can potentially benefit more from such approximations.

Furthermore, simpler hardware for both integer and floating-point approximations can potentially use a lower voltage supply, which lowers the energy consumption [Borkar, 2016; Chippa et al., 2014]. Considering that both the integer multiplication hardware and the floating-point unit may be in the processor critical path, the lower supply voltage could be applied not only to the particular module, but to the CPU as a whole, allowing even lower energy consumption [George et al., 2006]. Using *ADeLe*, this situation can be easily modeled with the proper energy model by changing the

Figure 4.10: Relation between memory errors and energy.

value of the voltage operating parameter (Sec. 3.1.4), making straight-forward energy estimations possible.

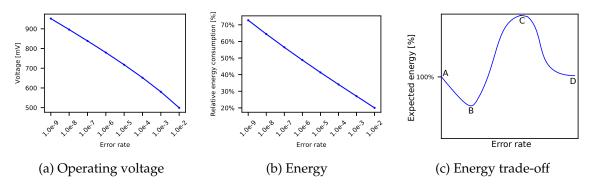

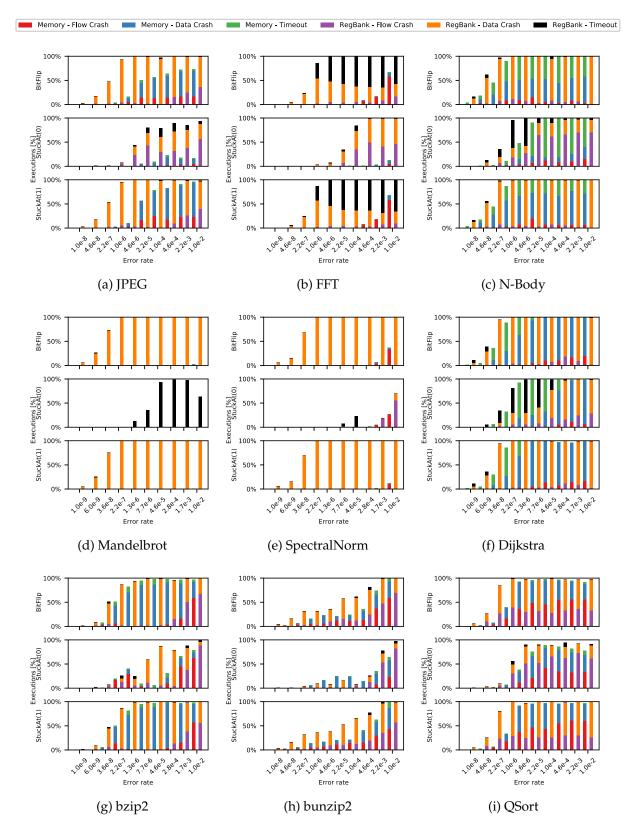

## 4.2 Voltage-overscaled memories

In our second scenario, *voltage-overscaled memories*, we use the *ADeLe* framework to demonstrate the energy-quality trade-off in multiple applications when their executions are subjected to error-susceptible memories. We injected three different types of errors – BitFlip, StuckAt(0) and StuckAt(1) – in memory read and write operations at given error rates and estimated a supply-voltage level according to a statistical model in the literature [Wang and Calhoun, 2011]. Figs. 4.10a and 4.10b show the relation between the error rate and operating voltage and energy.