## UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA MECÂNICA COMISSÃO DE PÓS-GRADUAÇÃO EM ENGENHARIA MECÂNICA

# Utilização de Ferramentas de Prototipagem Rápida direcionada à Concepção de Sistemas Embarcados baseados em Computação Reconfigurável

Autor: Wlamir de Almeida Passos

Orientador: Prof. Dr. João Maurício Rosário

66/2008

# UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA MECÂNICA COMISSÃO DE PÓS-GRADUAÇÃO EM ENGENHARIA MECÂNICA DEPARTAMENTO DE PROJETO MECÂNICO

## Utilização de Ferramentas de Prototipagem Rápida direcionada à Concepção de Sistemas Embarcados baseados em Computação Reconfigurável

Autor: Wlamir de Almeida Passos

Orientador: Prof. Dr. João Maurício Rosário

Curso: Engenharia Mecânica

Área de Concentração: Mecânica dos Sólidos e Projeto Mecânico

Dissertação de mestrado acadêmico apresentada à comissão de Pós Graduação da Faculdade de Engenharia Mecânica, como requisito para a obtenção do título de Mestre em Engenharia Mecânica.

Campinas, 2008. SP – Brasil

## FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA E ARQUITETURA - BAE - UNICAMP

P268u

Passos, Wlamir de Almeida

Utilização de ferramentas de prototipagem rápida direcionada à concepção de sistemas embarcados baseados em computação reconfigurável / Wlamir de Almeida Passos. --Campinas, SP: [s.n.], 2008.

Orientador: João Maurício Rosário Dissertação (mestrado) - Universidade Estadual de Campinas, Faculdade de Engenharia Mecânica.

1. Sistemas embutidos de computador. 2. Controle preditivo. 3. Robótica. 4. Robôs moveis. 5. Simulação (Computadores). 6. Robôs – Sistema de controle. I. Rosário, João Maurício. II. Universidade Estadual de Campinas. Faculdade de Engenharia Mecânica. III. Título.

Título em Inglês: Utilization of rapid prototyping tools for conception of embedded systems based on reconfigurable computation

Palavras-chave em Inglês: Reconfigurable computing, Control, Robotics, Modeling

Área de concentração: Mecânica dos Sólidos e Projeto Mecânico

Titulação: Mestre em Engenharia Mecânica

Banca examinadora: Humberto Ferasoli Filho, Niederauer Mastelari

Data da defesa: 27/06/2008

Programa de Pós-Graduação: Engenharia Mecânica

# UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA MECÂNICA COMISSÃO DE PÓS-GRADUAÇÃO EM ENGENHARIA MECÂNICA DEPARTAMENTO DE PROJETO MECÂNICO

## DISSERTAÇÃO DE MESTRADO

## Utilização de Ferramentas de Prototipagem Rápida direcionada à Concepção de Sistemas Embarcados baseados em Computação Reconfigurável

Autor: Wlamir de Almeida Passos

Orientador: Prof. Dr. João Maurício Rosário

A Banca Examinadora composta pelos membros abaixo aprovou esta Dissertação:

Prof. Dr. Voão Maurício Rosario, Presidente

UNICAMP

Prof. Dr. Humberto Ferasoli Filho

UNESP/Bauru

Prof. Dr. Niederauer Mastelari

UNICAMP

## Dedicatória:

Dedico este trabalho à minha esposa e filha.

## **Agradecimentos**

Presto a minha mais sincera homenagem a todos aqueles que de forma direta ou indireta ajudaram a construir este trabalho.

A minha família, pelo carinho, contínuo apoio e motivação dados durante estes anos.

Ao pessoal do Laboratório de Automação Integrada e Robótica da Faculdade de Engenharia Mecânica da Unicamp, em especial ao meu amigo e orientador Prof. Dr. João Maurício Rosário pelos valiosos conselhos e orientação, bem como pela confiança em mim depositada.

A todos os professores e funcionários do Departamento de Projeto Mecânico da Faculdade de Engenharia Mecânica da UNICAMP que ajudaram de forma direta e indireta na conclusão deste trabalho.

A empresa Altera e seus representantes, em especial ao Eng. Neimar Marques Duarte, pelo suporte oferecido.

Ao amigo e companheiro de trabalho Prof. Wellington Roberto Branco (in memoriam).

### Resumo

PASSOS, Wlamir de Almeida, Utilização de Ferramentas de Prototipagem Rápida direcionada à Concepção de Sistemas Embarcados baseados em Computação Reconfigurável, Campinas: Faculdade de Engenharia Mecânica, Universidade Estadual de Campinas, 2008. Dissertação (Mestrado).

Durante os últimos anos tem ocorrido uma grande evolução tecnológica na área de sistemas embarcados, abrangendo inovações tanto em hardware como em software. Tais inovações permitem o desenvolvimento de novas metodologias de projeto que levem em conta a facilidade de futuras modificações, modernizações e expansões do sistema projetado. Este trabalho apresenta um estudo de novas ferramentas de projeto para sistemas baseados em lógica reconfigurável. A principal motivação deste trabalho é a apresentação de ferramentas para prototipagem rápida baseadas em computação reconfigurável para implementação de protótipos de sistemas Embarcados. Será abordada a evolução deste tipo de tecnologia bem como os softwares de desenvolvimento disponíveis. Será também abordado um estudo de caso na área de Acionamento e Controle de Sistemas Mecatrônicos bem como a sua implementação e teste utilizando-se a técnica HIL - Hardware In the Loop.

#### Palavras Chave

Lógica Reconfigurável, Sistemas Embarcados, Robótica Móvel, Modelagem, Controle.

## **Abstract**

PASSOS, Wlamir de Almeida, *Utilization of Rapid Prototyping Tools for conception of Embedded Systems based on Reconfigurable Computation*, Campinas: Faculdade de Engenharia Mecânica, Universidade Estadual de Campinas, 2008. Dissertação (Mestrado)

In the last years, there has been a great technologic evolution in the embedded systems area, covering innovations both in hardware and software. Those innovations allow the development of new project methodologies that considers the facility of future modifications, upgrades and expansions for the system. This work shows a study about new design tools made for systems based on reconfigurable computation. The main motivation of this work is the presentation of tools for fast prototyping based on prototyping seeking the implementation of prototypes of embedded systems. It will be discussed the evolution of this type of technology as well as the available development software. It will be also discussed a case study on mechatronic control system as well as it's implementation and tests using Hardware In the Loop (HIL) techniques.

Keywords:

Reconfigurable Computing, Embedded Systems, Mobile Robotics.

## Índice

| Lista de Figuras                                                            | xii   |

|-----------------------------------------------------------------------------|-------|

| Lista de Tabelas                                                            | xvii  |

| Nomenclatura                                                                | xviii |

|                                                                             |       |

| Capítulo 1                                                                  | 1     |

| 1.1 Apresentação do Problema                                                | 3     |

| 1.2 Motivação                                                               | 5     |

| 1.3 Objetivos do Trabalho                                                   | 5     |

| 1.4 Delineamento do trabalho                                                | 6     |

| 1.5 Organização do trabalho                                                 | 8     |

| Capítulo 2                                                                  | 11    |

| 2.1 Introdução                                                              | 11    |

| 2.2 Estado da Arte                                                          | 13    |

| 2.3 O conceito de Prototipagem Rápida na Concepção de Sistemas Mecatrônicos | 17    |

| 2.4 Modelagem de Sistemas Físicos                                           | 20    |

| 2.5 Implementação do Sistema de Controle                                    | 22    |

| 2.6 Simulador Virtual                                                       | 27    |

| 2.7 Sistema de Supervisão e Controle                                        | 31    |

| 2.8 Sistemas Reconfiguráveis                                                | 32    |

| 2.9 Exemplos de Aplicações de Sistemas Reconfiguráveis                      | 37    |

| 2.10 Ferramenta de Projeto Quartus II                                       | 40    |

| 2.11 Conclusões                                                             | 42    |

| Capítulo 3                                                                           | 43       |

|--------------------------------------------------------------------------------------|----------|

| 3.1 Conceitos Básicos de Lógica Reprogramável                                        | 43       |

| 3.2 Descrição de Ferramentas para desenvolvimento de FPGA                            | 50       |

| 3.2.1 Ferramenta de projeto Quartus II                                               | 50       |

| 3.2.2 Implementação de um projeto                                                    | 51       |

| 3.2.3 Entrada de dados por esquema                                                   | 52       |

| 3.2.4 Entrada em arquivos formato Texto                                              | 55       |

| 3.2.5 Descrição das etapas para concepção e síntese de um FPGA                       | 56       |

| 3.2.5.1 Síntese RTL                                                                  | 56       |

| 3.2.5.2 Simulação RTL                                                                | 56       |

| 3.2.5.3 Place & Route                                                                | 57       |

| 3.2.5.4 Timing Analysis                                                              | 57       |

| 3.2.5.5 Gate Level Simulation                                                        | 58       |

| 3.2.5.6 PC Board Simulation & Test                                                   | 58       |

| 3.3 Ambiente de simulação e prototipagem MATLAB Simulink®                            | 58       |

| 3.3.1 Aplicações Multi-domínios                                                      | 59       |

| 3.3.3 Implementação do Sistema de Controle                                           | 61       |

| 3.3.4 A utilização do Simulink <sup>®</sup> como ferramenta gráfica para a concepção | 62       |

| 3.4 DSP Builder                                                                      | 63       |

| 3.5 SOPC Builder                                                                     | 64       |

| 3.6 Conclusões                                                                       | 67       |

| Capítulo 4                                                                           | 69       |

|                                                                                      | 60       |

| 4.1 Modelagem de Sistemas Mecatrônicos                                               | 69       |

| 4.2 Modelagem de um motor CC (Ogata, 1998)                                           | 71       |

| 4.2.1 Equação Elétrica                                                               | 71       |

| 4.2.2 Equação de Acoplamento Eletro-mecânico                                         | 71       |

| 4.2.3 Equação Mecânica                                                               | 71       |

| 4.3 Diagrama de Blocos Associados                                                    | 72       |

| 4.4 Transformada de Laplace                                                          | 73       |

| 4.4.1 Parte Elétrica                                                                 | 73       |

| 4.4.2 Parte Mecânica                                                                 | 74       |

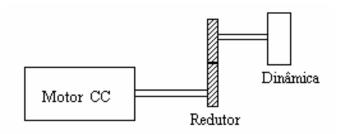

| 4.5 Transmissão Mecânica                                                             | 74       |

| 4.5.1 Redutor acoplado a uma carga                                                   | 77       |

| 4.5.2 Dinâmica do sistema                                                            | 77       |

| 4.6 Controlador PID baseado no modelo dinâmico                                       | 79       |

| 4.6.1 Projeto de um Controlador de posição PID                                       | 80<br>81 |

| 4.6.2 Determinação dos ganhos de um controlador PID                                  | 81       |

| 4.6.3 Método de Ziegler-Nichols                                                      | 83       |

| <ul><li>4.6.4 Método de Chien-Hrones-Reswick (CHR)</li><li>4. 7 Conclusões</li></ul> | 85<br>85 |

| T. / CONCIUSOUS                                                                      | 83       |

| Capítulo 5                                                                                          | 87         |

|-----------------------------------------------------------------------------------------------------|------------|

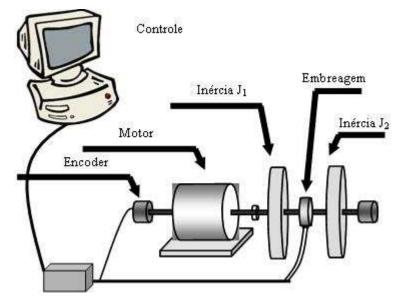

| 5.1 Descrição da Bancada Experimental                                                               | 87         |

| 5.2 Elementos Constituintes da Bancada Experimental                                                 | 90         |

| 5.3 Sistema de Monitoramento e Controle                                                             | 91         |

| 5.4 Implementação experimental do leitor de posição e velocidade                                    | 93         |

| 5.5 Interface com o motor                                                                           | 94         |

| 5.6 Resultados obtidos na implementação experimental do modelo                                      | 95         |

| 5.6.1 Análise da resposta do sistema submetido a uma entrada degrau                                 | 95         |

| 5.6.2 Controlador PID                                                                               | 96         |

| 5.6.3 Controlador PID na forma RST                                                                  | 96         |

| 5.6.3.1 Estrutura de controle na forma RST                                                          | 99         |

| 5.6.3.2 Controlador PID na forma RST                                                                | 100<br>102 |

| 5.6.3.3 Controlador PID na forma RST no Simulink® 5.6.4 Controlador PID na forma RST no DSP Builder | 102        |

| 5.6.4.1 Filtros FIR e IIR                                                                           | 104        |

| 5.6.4.2 Implementação do controlador RST                                                            | 104        |

| 5.6.5 Controlador RST – VHDL Import                                                                 | 110        |

| 5.7 Controlador RST – HIL (Hardware In the Loop)                                                    | 115        |

| 5.8 Controlador RST via DSP Builder - HIL                                                           | 119        |

| 5.9 Controlador RST – VHDL parâmetros constantes no VHDL                                            | 121        |

| 5.10 Implementação Final                                                                            | 123        |

| 5.10.1 Arquitetura proposta para implementação                                                      | 124        |

| 5.10.2 Implementação com processador Nios II                                                        | 125        |

| 5.11 Conclusão                                                                                      | 128        |

|                                                                                                     |            |

| Capítulo 6                                                                                          | 129        |

| Conclusões Finais e perspectivas futuras                                                            | 129        |

| Referências Bibliográficas                                                                          | 133        |

| Anexo A – Controladores Preditivos                                                                  | 145        |

| A.1 - Aspectos gerais                                                                               | 145        |

| A.2 Relacionamento com Outros Métodos                                                               | 149        |

| A.2. 1 Controle Linear Quadrático                                                                   | 149        |

| A.2.2 Projeto por Alocação de Pólos                                                                 | 151        |

| Anexo B – Código implementado em linguagem VHDL                                                     | 155        |

| Anexo C – Código implementado em linguagem VHDL (parâmetros constantes)                             | 159        |

## Lista de Figuras

| Figura 1.1: Ciclo de concepção de um produto através da prototipagem rápida.            | 7  |

|-----------------------------------------------------------------------------------------|----|

| Figura 2.1 : Definição do domínio da Mecatrônica (IFAC 2005)                            | 14 |

| Figura 2.2: Ciclo em V – Metodologia para Concepção e Desenvolvimento para sistemas     |    |

| Mecatrônicos (Isermann, 2005)                                                           | 16 |

| Figura 2.3: Concepção Integrada de um "Produto Inteligente"                             | 17 |

| Figura 2.4: Fluxograma das diferentes fases de implementação de um sistema mecatrônico  | 18 |

| Figura 2.5: Princípio da Prototipagem Rápida de Sistemas Mecatrônicos.                  | 19 |

| Figura 2.6: Conceitos a serem implementados na planta baseados na modelagem de sistemas |    |

| físicos                                                                                 | 21 |

| Figura 2.7: Hardware In the Loop através do Mathworks®.                                 | 25 |

| Figura 2.8: Esquema de prototipagem do controlador.                                     | 26 |

| Figura 2.9: Simulador Virtual dentro do processo de Prototipagem Rápida                 | 28 |

| Figura 2.10: Malha de acionamento e controle de posição de uma junta.                   | 29 |

| Figura 2.11: Simulador de um Robô Móvel.                                                | 30 |

| Figura 2.12: Proposta de interface de visualização para sistemas robóticos móveis       | 32 |

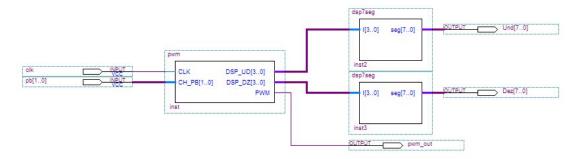

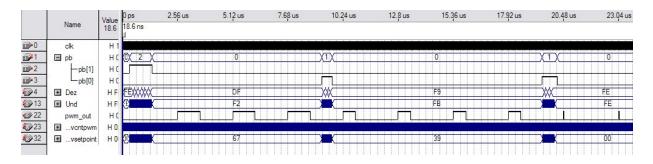

| Figura 2.13: Projeto PWM_top em linguagem gráfica (esquemático)                         | 40 |

| Figura 2.14: Representação de um sub bloco de projeto em linguagem VHDL                 | 41 |

| Figura 2.15: Simulação de um projeto em forma de onda                                   | 41 |

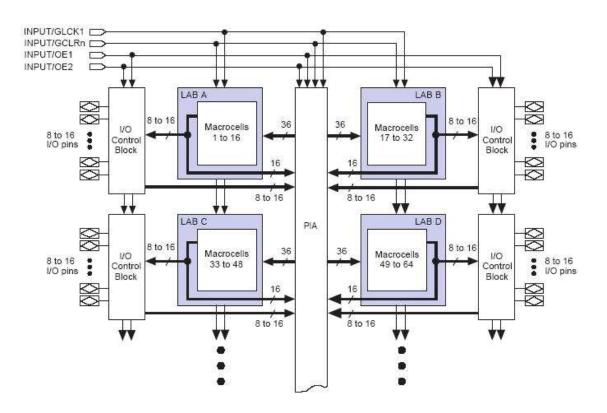

| Figura 3.1: Diagrama interno de uma PAL.[Texas, 1992]                              | 44 |

|------------------------------------------------------------------------------------|----|

| Figura 3.2: EPLD - Erasable Programable Logic Device. [ALTERA, 1999]               | 45 |

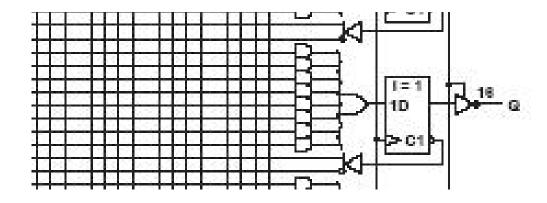

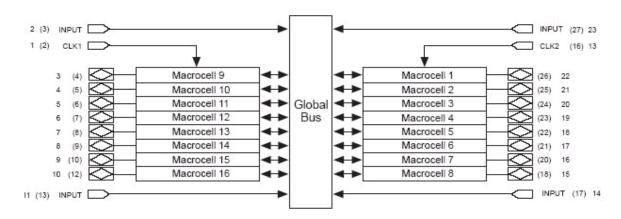

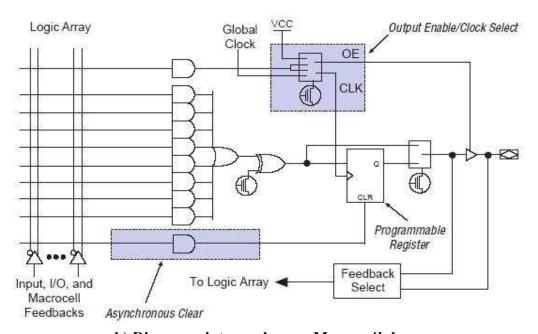

| Figura 3.3: Diagrama interno de um CPLD.[ALTERA, 2005]                             | 46 |

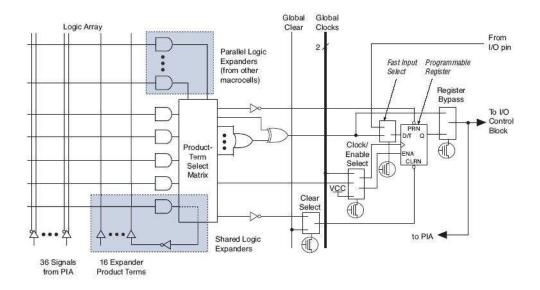

| Figura 3.4: Diagrama interno de uma macro-célula.[ALTERA,2005]                     | 47 |

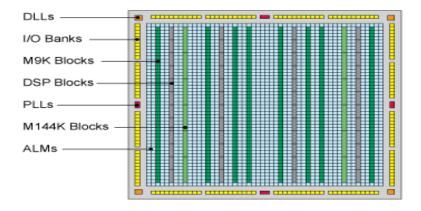

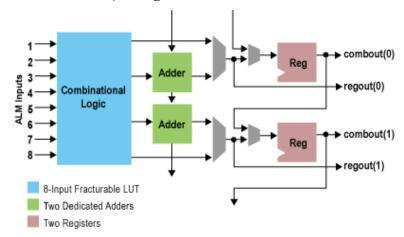

| Figura 3.5: FPGA família Stratix III. [ALTERA, 2007]                               | 49 |

| Figura 3.6: Projeto em linguagem gráfica utilizando a ferramenta Quartus II        | 51 |

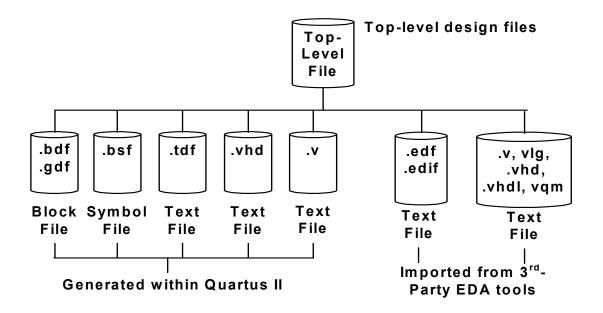

| Figura 3.7: Hierarquia de Projeto – Tipos de arquivos.                             | 52 |

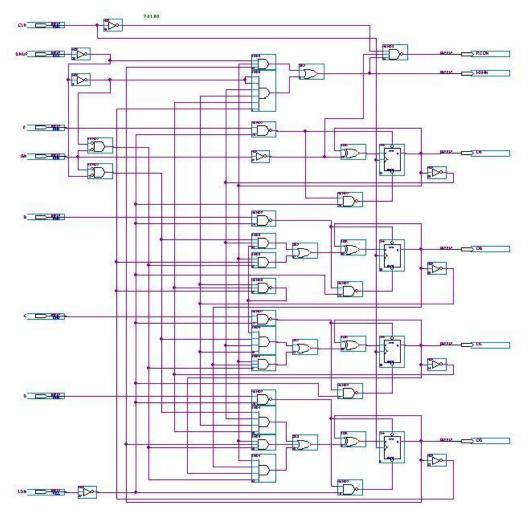

| Figura 3.8: Projeto de um contador com portas lógicas e flip-flop.                 | 54 |

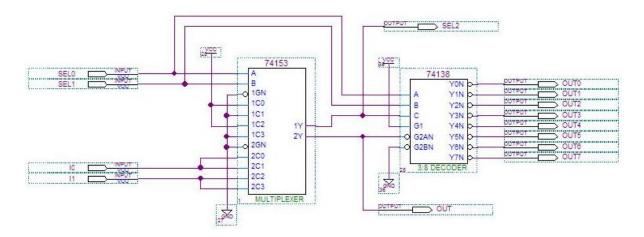

| Figura 3.9: Projeto com biblioteca 74xx.                                           | 54 |

| Figura 3.9: Projeto com blocos configuráveis.                                      | 55 |

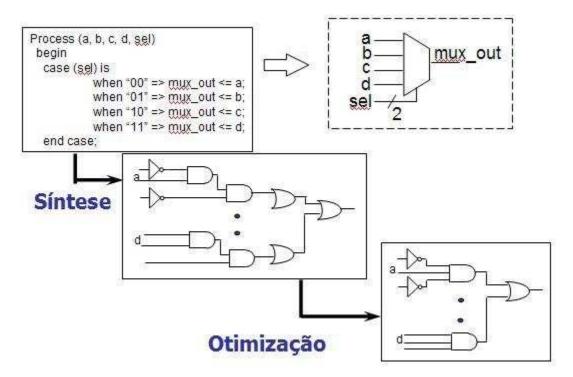

| Figura 3.10: Síntese Lógica.                                                       | 57 |

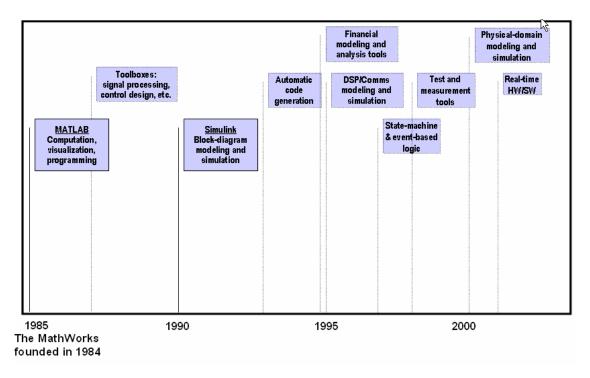

| Figura 3.11: A evolução da Mathworks desde a sua criação.                          | 59 |

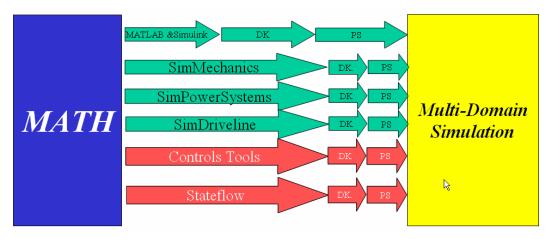

| Figura 3.13: Multi-domínios de aplicação do MATLAB®                                | 60 |

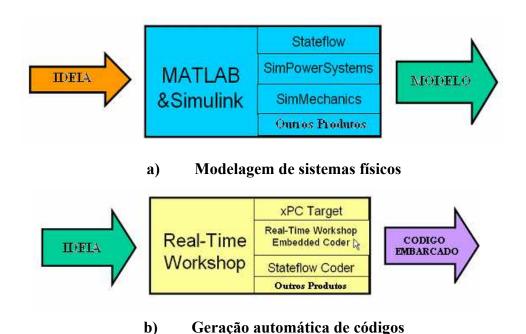

| Figura 3.14: Ferramentas para prototipagem de sistemas Mecatrônicos com MATLAB®    | 60 |

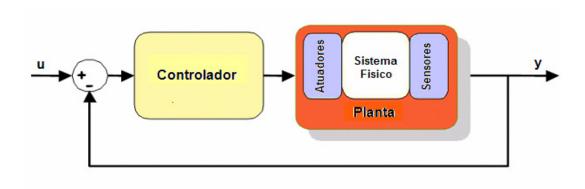

| Figura 3.15: Sistema de controle baseado na modelagem de sistemas físicos          | 61 |

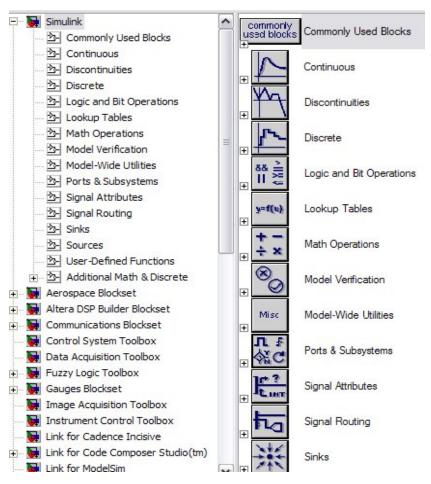

| Figura 3.16: Bibliotecas Matlab/Simulink®.                                         | 62 |

| Figura 3.17: Simulação HIL do Matlab/Simulink®                                     | 64 |

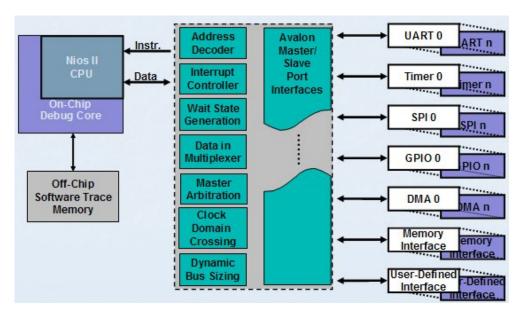

| Figura 3.18: Arquitetura das interfaces do processador Nios II ALTERA.             | 65 |

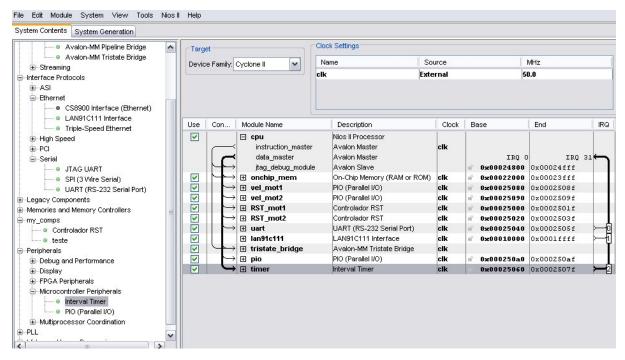

| Figura 3.19: Tela de configuração do SOPC Builder                                  | 66 |

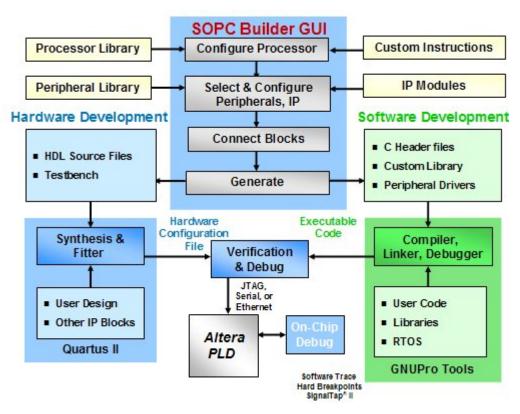

| Figura 3.20: Fluxo de projeto do SOPC Builder.                                     | 67 |

| Figura 4.1: Motor CC controlado pela corrente de armadura.                         | 70 |

| Figura 4.2: Motor CC - Diagrama de blocos associados às equações do modelo         | 72 |

| Figura 4.3: Diagrama de blocos para a equação completa.                            | 73 |

| Figura 4.4: Diagrama de blocos para o modelo completo das funções de transferência | 74 |

| Figura 4.5: Sistema de engrenagens.                                             | 75  |

|---------------------------------------------------------------------------------|-----|

| Figura 4.6: Sistemas mecânicos equivalentes.                                    | 76  |

| Figura 4.7: Representação do acoplamento de uma carga no eixo do redutor        | 76  |

| Figura 4.8: Diagrama de blocos associado.                                       | 77  |

| Figura 4.9: Relações Matemáticas – Motor acoplado a uma carga                   | 78  |

| Figura 4.10: Diagrama de blocos para a equação do sistema                       | 78  |

| Figura 4.11: Esquema de um sistema para o cálculo do ganho do PID.              | 81  |

| Figura 4.12: Ganhos de um controlador PID.                                      | 82  |

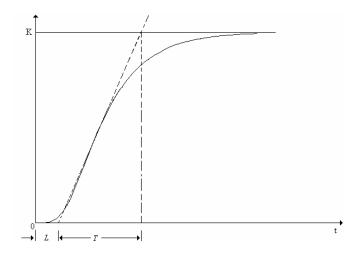

| Figura 4.13: Método de CHR - obtenção da resposta temporal a uma entrada degrau | 83  |

| Figura 4.14: Curva resposta temporal utilizada no método CHR                    | 84  |

| Figura 4.15: Escolha do tipo de Controlador utilizando o método de CHR.         | 84  |

| Figura 4.16: Cálculo dos Ganhos do Controlador utilizando o método de CHR       | 85  |

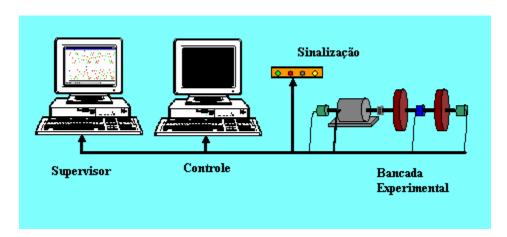

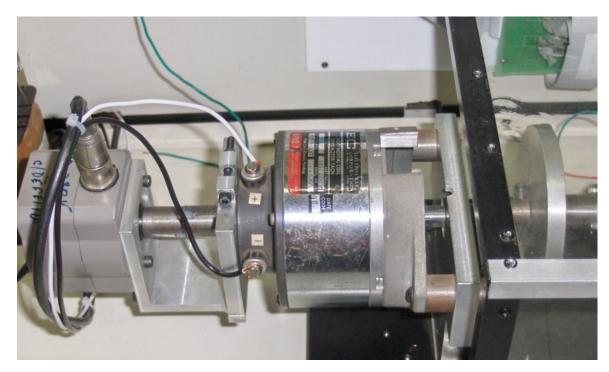

| Figura 5.1: Bancada experimental                                                | 88  |

| Figura 5.2 – Sistema de supervisão e controle.                                  | 91  |

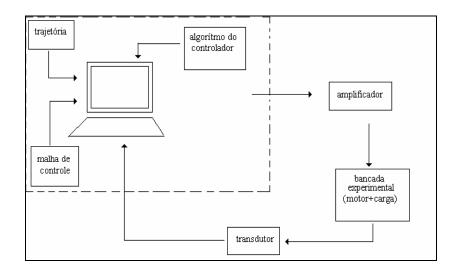

| Figura 5.3: Esquema representativo do Sistema de aquisição e controle           | 92  |

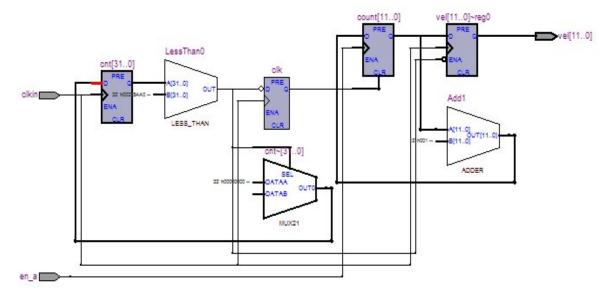

| Figura 5.4: Sistema de medição de posição e velocidade.                         | 93  |

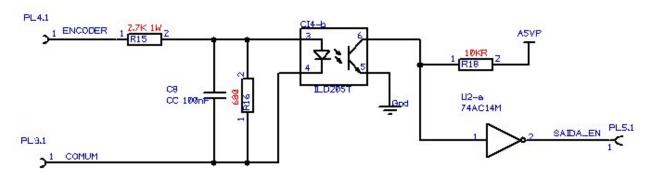

| Figura 5.5: Circuito interface com encoder.                                     | 94  |

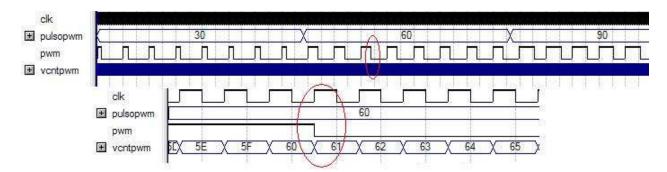

| Figura 5.6: Geração da saída PWM                                                | 95  |

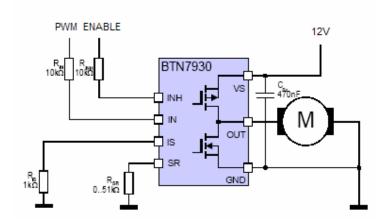

| Figura 5.7: Circuito de potência para acionamento do Motor CC.                  | 95  |

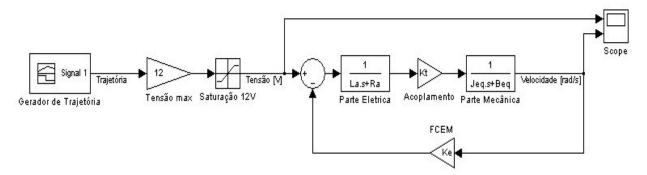

| Figura 5.8: Modelo motor CC.                                                    | 96  |

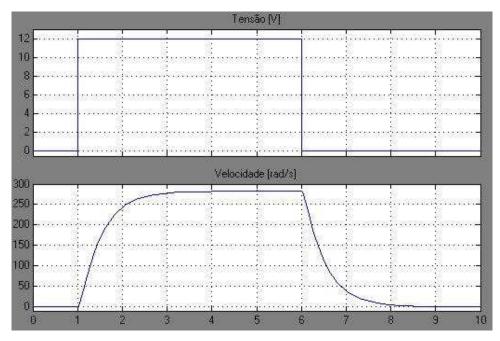

| Figura 5.9: Resposta motor CC com carga                                         | 97  |

| Figura 5.10: Implementação Controlador PID na forma RST.                        | 98  |

| Figura 5.11: Estrutura de controlador na forma RST.                             | 99  |

| Figura 5.12: Estrutura controlador RST.                                         | 100 |

| Figura 5.13: Controlador RST em Simulink®.                                    | 102 |

|-------------------------------------------------------------------------------|-----|

| Figura 5.14: Controlador RST: Implementação em Simulink® e Resultados obtidos | 103 |

| Figura 5.15: Filtro FIR.                                                      | 104 |

| Figura 5.16: Filtro IIR.                                                      | 105 |

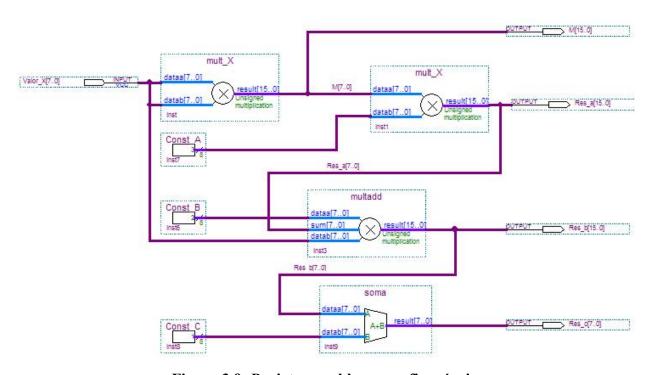

| Figura 5.17: Implementação do controlador                                     | 106 |

| Figura 5.18: Controle com RST – Simulink®.                                    | 107 |

| Figura 5.19: Implementação do Controlador RST – DSP Builder                   | 108 |

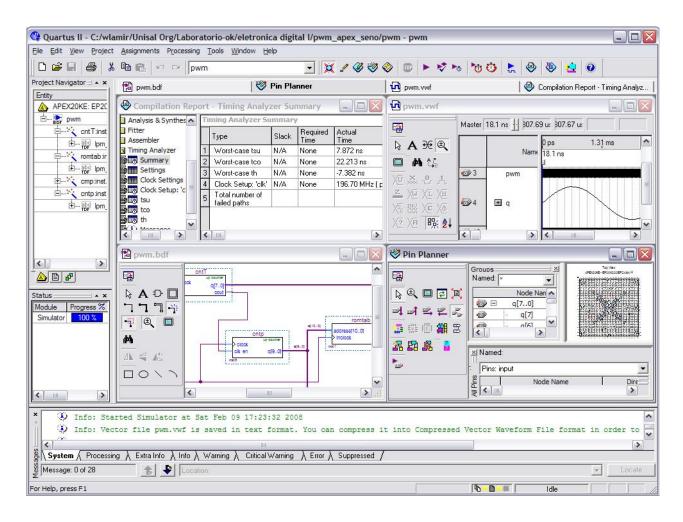

| Figura 5.20: Tela de geração do DSP Builder                                   | 109 |

| Figura 5.21: Relatório de compilação Quartus                                  | 110 |

| Figura 5.22: Relatório de compilação Quartus II.                              | 111 |

| Figura 5.23 – Síntese do controlador                                          | 112 |

| Figura 5.24: Tela de geração do DSP Builder                                   | 113 |

| Figura 5.25: Implementação do Controlador RST – VHDL import.                  | 114 |

| Figura 5.26: Saída com controle RST – VHDL import.                            | 115 |

| Figura 5.27 – Tela de geração do HIL                                          | 116 |

| Figura 5.28 – Controle com RST - HIL                                          | 118 |

| Figura 5.29 – Saída controle com RST – HIL                                    | 119 |

| Figura 5.30 – Controle com RST DSP Builder - HIL                              | 120 |

| Figura 5.31 – Saída controle com RST DSP Builder - HIL                        | 121 |

| Figura 5.32 – Relatório de compilação Quartus II.                             | 122 |

| Figura 5.33 – Controle com RST – VHDL constantes                              | 122 |

| Figura 5.34 – Saída controle com RST - VHDL constantes                        | 123 |

| Figura 5.35 – Robô Móvel Autônomo                                             | 123 |

| Figura 5.36 –Controle Robô Móvel Autônomo                                     | 124 |

| Figura 5.37 – Sistema de controle com processador Nios II       | 125 |

|-----------------------------------------------------------------|-----|

| Figura 5.38 – Teste do sistema controle com processador Nios II | 126 |

| Figura 5.39 – Kit Altera com interface Encoder e Motor          | 126 |

| Figura 5.40 – Bancada Implementada com Encoder, Motor e Inércia | 127 |

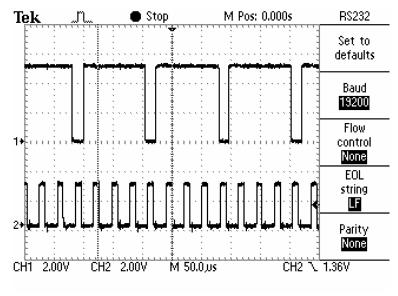

| Figura 5.41 – Formas de Onda do Encoder e PWM.                  | 127 |

## Lista de Tabelas

Tabela 5.1: Parâmetros do sistema de acionamento e controle da plataforma experimental.

91

## **Nomenclatura**

## Abreviações

AHDL - Altera Hardware Description Language

**ALM** - Adaptive Logic Modules

**API** – Application Program Interface

**ASIC** - Application Specific Integrated Circuits

**CAD** - Computer Aid Design

**CCM** - Custom Computing Machines

**CPLD -** Complex Programmable Logic Devices

**DBF** - Block Design File

**DFGA** - Dinamically Field Programmable Gate Array

**DSP** – Digital Signal Processor

**EPLD** – Erasable Programmable Logic Device

**FCCM** – FPGA based Custom Computing Machines

**FFT** – Fast Fourier Transform

**FIR** – Finite Impulse Response

**FPGA** - Field Programmable Gate Array

**GAL** - Generic array logic

HIL - Hardware In-the-Loop

**IEEE** - Institute of Electrical and Electronics Engineers, Inc.

**IIR** – Infinite Impulse Response

IP-CORE – Intellectual Property Core

JTAG - Joint Test Action Group

PAL - Programmable array logic

**PID** – Proporcional Integral Derivativo

**PLDs** - Programmable Logic Devices

**PLL** – Phase-Locked Loops

**PWM** - Pulse-Width Modulation

**SOPC** - System On Programmable Chip

**VHDL** - VHSIC Hardware Description Language

## Capítulo 1

## Introdução

O desenvolvimento de protótipos de sistemas embarcados tem sido alvo de inúmeros trabalhos na área de Controle e Automação. Dentre as inúmeras aplicações de sistemas embarcados ou que utilizam sistemas embarcados, podemos destacar diferentes dispositivos que integram sensores e atuadores para a execução de alguma tarefa e que exigem maior ou menor capacidade de controle como: impressoras e periféricos de computadores, automóveis, robôs industriais, robôs móveis, aparelhos de telefonia, cadeiras de rodas, próteses antropomórficas, etc. Nesses sistemas são geralmente utilizados microcontroladores com algoritmos desenvolvidos em várias linguagens de software para realizar o controle destes dispositivos. Mais recentemente, alguns destes algoritmos foram também desenvolvidos em trabalhos associados com computação reconfigurável, que apresentam vantagens em termos de desempenho.

Entre todos os campos associados com projeto de sistemas embarcados, as tecnologias de *software* e *hardware* são as que têm experimentado a mais rápida evolução. É muito grande a quantidade de novos microprocessadores, interfaces de comunicação, interfaces de potência, sensores, compiladores, sistemas operacionais e ambientes de desenvolvimento disponibilizados no mercado. Em função desta acelerada evolução tecnológica, a idéia de se utilizar estruturas abertas e reconfiguráveis, que possam adaptar-se a novas demandas, torna-se muito atraente, sendo mesmo um pré-requisito na consideração de um projeto de um sistema embarcado.

O conceito de sistemas abertos tem sido estudado nos últimos anos por várias instituições no campo de máquinas ferramentas e engenharia de produção, focalizando os aspectos de modularidade, os efeitos da arquitetura de controle e da rede de comunicação no desempenho do sistema.

O objetivo deste conceito aplicado à arquitetura reconfigurável é permitir uma fácil e rápida adaptação de dispositivos embarcados a novas evoluções tecnológicas, para uma melhor portabilidade e capacidade de intercâmbio para o sistema final. A divisão da estrutura em pequenos blocos funcionais, com interfaces bem especificadas, permite uma melhor definição das tarefas de uma equipe de projeto multidisciplinar, bem como a rápida adaptação de um determinado bloco a uma nova evolução tecnológica. Este tipo de solução não pode ser realizado em muitos dos sistemas comerciais disponíveis, pois estes não fornecem informações ou não apresentam recursos para permitir este tipo de manipulação.

Este trabalho tem como objetivo a utilização de ferramentas para implementação de novas arquiteturas de controle para sistemas mecatrônicos a fim de torná-los mais precisos e eficientes na execução de tarefas, aliando conceitos de prototipagem rápida para a implementação de controladores, a partir da apresentação de proposta de ambiente baseado em computação reconfigurável para implementação em protótipos de sistemas embarcados. As novas tecnologias envolvendo a concepção de microprocessadores, interfaces de potência e comunicação, aliados ao conceito de prototipagem rápida possibilitam pesquisas científicas, onde a implementação de controladores requer menores custos.

Dentro do contexto proposto para desenvolvimento dessa Dissertação de Mestrado são considerados aspectos de hardware e software, e a principal motivação deste trabalho é propiciar um ambiente que facilite o desenvolvimento de protótipos de sistemas embarcados, enfatizando o desenvolvimento de ferramentas simples que permitam o controle e a monitoração dos diferentes sensores e atuadores nesta categoria de projeto. Como consequência, é proposto o

desenvolvimento de pequenos módulos independentes com interfaces de comunicação bem definidas como parte de uma estrutura orientada a uma arquitetura aberta.

Neste capitulo apresentaremos um panorama geral do trabalho desenvolvido, sendo apresentado um estado da arte do conceito de lógica Reconfigurável, justificando o desenvolvimento desse projeto de pesquisa, seus objetivos gerais e específicos, a necessidade de capacitação nesta importante área e a forma como foi delimitada esta questão, além da estrutura geral dos capítulos da tese.

### 1.1 Apresentação do Problema

A Mecatrônica integra conhecimentos nas diferentes áreas de engenharia, matemática, computação, permitindo o desenvolvimento com maior rapidez de sistemas compostos de uma estrutura mecânica complexa, geralmente composta por atuadores, sensores de posicionamento e um sistema de acionamento e controle, inserindo dentro desse contexto a Robótica.

Robôs são encontrados nos diversos meios, desenvolvendo as mais diversas funções, em atividades insalubres, educacional, ou simplesmente em trabalhos que requerem força e agilidade. Cada grau de liberdade é geralmente composto por atuadores, sensores de posicionamento e pelo sistema de acionamento e controle.

Os elementos básicos do manipulador como estrutura, eixos, mancais, transmissão, devem ser dimensionados do ponto de vista de resistência e rigidez, com o objetivo de atingir um volume de trabalho e precisão mecânica exigidos numa operação automatizada. Os sensores de posição não são capazes de medir possíveis deformações estruturais, como também atritos e folgas nas juntas.

A robótica industrial possibilita que produtos sejam realizados de maneira mais rápida e eficiente do que no passado. Para isso, o desenvolvimento da mecânica de precisão quanto da eletrônica foi indispensável para que isso ocorresse. Mas isso pode ser melhorado, principalmente

no que se refere ao tempo de execução de diferentes tarefas, para tal, a melhoria do controle de robô com as grandes possibilidades de interações que um ambiente automatizado pode oferecer.

Dentre os sistemas embarcados, os robôs móveis têm-se apresentado como plataformas para consolidação de conhecimento em diversas áreas de pesquisa, como modelagem, controle, automação, sistemas de potência, sensores, transmissão de dados, eletrônica embarcada e engenharia de *software*, sendo cada vez mais usadas em instituições de ensino e pesquisa.

O estudo de novas arquiteturas de controle torna-se muito importante para que haja uma melhoraria no desempenho de robôs industriais face às mudanças bruscas de parâmetros associados à posição, velocidade e aceleração, durante a realização de uma determinada trajetória. A Automação Flexível possibilita que robôs sejam cada vez mais rápidos podendo interferir em um grande volume de trabalho, dessa forma, novas técnicas de controle são estudadas com a finalidade de torná-los mais eficientes.

Mais especificamente na área de controle, se faz necessária uma ferramenta que possibilite a simulação e a rápida implementação da metodologia aplicada, validando assim o projeto na prática. Esse tipo de ferramenta pode ser extremamente útil na área de desenvolvimento industrial para a validação de estudos e comprovação de sua eficiência.

As validações dos conceitos e ferramentas de prototipagem rápida direcionada a Conceitos de sistemas embarcados baseadas em lógica reconfigurável desenvolvidos nos capítulos desta dissertação de mestrado foram realizadas no Laboratório de Automação Integrada e Robótica da UNICAMP através da prototipagem de um controlador de junta robótica.

#### 1.2 Motivação

Considerando-se o atual cenário tecnológico e o alto desenvolvimento de soluções cada vez mais integradas para concepção e validação de dispositivos mecatrônicos, a utilização de ferramentas de prototipagem rápida para concepção do sistema de controle torna-se uma indispensável opção para agilizar e facilitar a implementação de diferentes arquiteturas de controle, possibilitando assim a redução do tempo de finalização de um projeto e ou estudo científico, atendendo uma eficiência desejada.

A principal a motivação para o desenvolvimento desta dissertação de mestrado deve-se ao fato da necessidade de uma metodologia para a concepção e implementação de projetos na área de mecatrônica, visando permitir de forma mais rápida e com significativa redução de custos, a utilização mais adequada das tecnologias que compõem a área.

### 1.3 Objetivos do Trabalho

Considerando-se que a implementação de um sistema de controle, envolvendo o gerenciamento de entradas e de saídas, envolve muito tempo de concepção e alto custo de implementação. Neste trabalho de pesquisa são apresentadas ferramentas para concepção de controladores de juntas robóticas utilizando-se o conceito de prototipagem rápida. Conseqüentemente, o principal objetivo desta dissertação de mestrado é a apresentação de metodologias de Prototipagem Rápida de Controladores de juntas robóticas baseadas em lógica reconfigurável, através de ambiente voltado à capacitação e desenvolvimento de projetos na área de controle e automação industrial, onde os principais conceitos possam ser verificados e posteriormente implementados e validados na prática, fornecendo subsídios para a análise e estratégias para estas aplicações.

A utilização destas ferramentas possibilita a implementação, validação e testes de diferentes técnicas de controle baseadas no conhecimento, permitindo verificar rapidamente sua eficiência e desempenho com diferentes variações de parâmetros de controle. Esses procedimentos de

prototipagem rápida para a concepção de controladores de juntas robóticas permitem a realização de grande parte do projeto dentro de um ambiente de simulação, diminuindo tempo de projeto e custos envolvidos durante a sua fase de concepção.

#### 1.4 Delineamento do trabalho

A busca do conhecimento tecnológico necessário para o profissional do mundo atual, deve ser levada em consideração ao elaborar uma proposta de metodologia educacional. Para conseguir estes objetivos tem-se que, necessariamente, considerar novos conceitos e diferentes técnicas de abordagens que possam ser aplicadas, tanto para a área educacional como para a área tecnológica, além, evidentemente, do aproveitamento eficiente e efetivo dos recursos tecnológicos disponíveis.

A prototipagem rápida, que pode ser feita em vários níveis de abstração, três fases se apresentam como representantes deste ciclo integrado:

- a) Modelagem do sistema físico,

- b) Visualização do modelo funcional

- c) Descrição do software/hardware a ser implementado em dispositivos lógicos ou microcontroladores.

Estas três fases constituem o que se chama prototipagem rápida e estão associadas a um ambiente gráfico interativo e à utilização de um conjunto de bibliotecas e blocos personalizados.

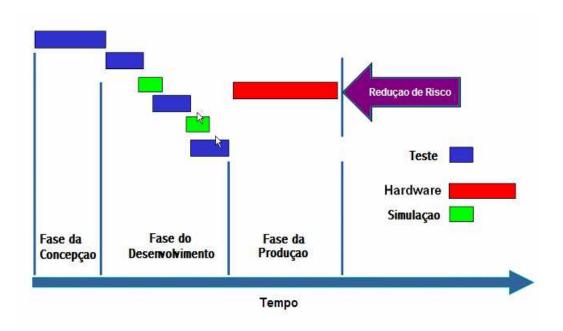

A figura 1.1 apresenta um cronograma das diferentes fases do ciclo de concepção de um produto enfatizando a diminuição das fases de seu desenvolvimento através da utilização de prototipagem rápida.

Figura 1.1: Ciclo de concepção de um produto através da prototipagem rápida.

Dentre as principais vantagens da utilização de Sistemas de Prototipagem Rápida em Mecatrônica podemos citar as seguintes:

- Detecção mais rápida de possíveis erros decorrentes da fase de implementação de um projeto, acarretando um menor custo de correção e/ou modificação do projeto,

- Concepção dentro de um ambiente de simulação e prototipagem comum, acarretando de tal modo na economia no desenvolvimento do projeto atual e de futuros projetos,

- Ambiente apropriado para Engenharia Colaborativa, com forte integração e conceito de equipe de trabalho.

Atualmente, os principais softwares tradicionais de modelagem e simulação de sistemas mecânicos e/ou eletrônicos direcionaram á área de prototipagem rápida em mecatrônica, com módulos e bibliotecas voltadas a aplicações no campo automobilístico, indústria aeronáutica e aeroespacial, etc. Esses ambientes de prototipagem rápida permitem a simulação, implementação e testes num ambiente cooperativo integrado. Dentre os principais aplicativos utilizados na

indústria, podemos destacar dentre os mais utilizados os seguintes: Labview da NI - National Instruments, DSpace, AMESim, Mathworks (Matlab-Simulink®), Altera e Xilinx.

O desenvolvimento deste trabalho de pesquisa envolve atividades de cooperação cientifica desenvolvida no Laboratório de Automação Integrada e Robótica (LAR) do DPM/FEM/UNICAMP e Departamento de Engenharia de Controle e Automação da SUPELEC, França, onde foram realizados ao longo dos últimos anos inúmeros projetos de parceria na área de controle de juntas robóticas de dispositivos mecatrônicos utilizando conceitos de prototipagem rápida associadas a uma metodologia para a organização de projetos que pode ser resumida em três etapas de desenvolvimento:

- 1) Elaboração e desenvolvimento da solução.

- 2) Simulação e Prototipagem.

- 3) Implementação e validação.

A partir da realização deste projeto de Pesquisa torna-se possível o desenvolvimento de projetos na área de Mecatrônica, utilizando conceitos de Prototipagem Rápida, permitindo assim a simulação de implementação de plantas industriais mecatrônicas, próximas a realidade do mercado.

### 1.5 Organização do trabalho

Esta dissertação de mestrado tem como principal proposta a apresentação e validação de ferramentas que permitam a rápida implementação de dispositivos de controle de juntas robóticas. O trabalho foi dividido nas seguintes etapas:

No Capítulo 2 desta dissertação é realizado um trabalho de revisão bibliográfica aprofundada abrangendo o estado da arte na área de prototipagem rápida de sistemas mecatrônicos e lógica reconfigurável utilizada para implementação de controladores de juntas robóticas. Assim, é mostrado o conceito de prototipagem rápida em mecatrônica bem como as

principais etapas que envolvem este importante conceito para o desenvolvimento de arquiteturas de controle mais eficientes, apresentando custo e tempo de implementação reduzido. Ainda neste capitulo são apresentados algumas justificativas que levaram a escolha dos ambientes Matlab/Simulink® e ALTERA como ferramenta de trabalho.

No Capitulo 3 deste trabalho são apresentados ambientes para prototipagem rápida e concepção de sistemas embarcados, onde são apresentados objetivos e propriedades destes sistemas, com ênfase nos aspectos de implementação de *hardware* e *software*, sendo também proposto neste capítulo uma estrutura mínima necessária para o funcionamento desse ambiente. Ainda neste capítulo, são descritas ferramentas para implementação, validação e testes desses controladores, além de outros tipos de interação possíveis com o sistema em estudo utilizando o ambiente Matlab Simulink®, e ALTERA como ferramenta para prototipagem de dispositivos mecatrônicos.

No Capítulo 4 é direcionada a modelagem de um sistema de acionamento e controle de uma junta robótica a partir da implementação de controladores PID expressos na forma genérica RST para posterior implementação em lógica reconfigurável, através da utilização de linguagem gráfica e linguagem VHDL.

No capitulo 5 concerne à etapa de validação e implementação experimental dos conceitos apresentados nos capítulos anteriores deste trabalho, através de um exemplo experimental implementado no Laboratório de Automação Integrada e Robótica da UNICAMP, para prototipagem de um controlador de posição de uma junta robótica baseado no conceito de *Hardware In-the-Loop* (HIL), demonstrando pelos resultados obtidos que o ambiente escolhido é eficaz e eficiente para a solução proposta.

Finalizando, no último capítulo deste trabalho, são apresentadas as conclusões finais e perspectivas futuras pertinentes ao desenvolvimento deste trabalho, bem como o uso e a escolha dessas novas ferramentas para soluções com prototipagem rápida.

Nos anexos são apresentados detalhadamente telas gráficas, programas implementados e resultados que não se encontram no corpo da tese, mas que permitem uma melhor compreensão por parte do leitor.

## Capítulo 2

# Prototipagem Rápida de Sistemas Mecatrônicos e Computação Reconfigurável - Revisão de Literatura

Dentre os novos modelos da mecatrônica podemos destacar que além da integração entre os diversos ramos das Engenharias Eletrônica, Mecânica e Computação podemos notar cada vez mais que a ênfase da mecatrônica é direcionada a integração de subsistemas mecânicos e eletrônicos com controle baseado em software, sendo que um dos principais objetivos dessa linha de pesquisa é estudar a integração no processo de *design* de ferramentas computacionais e métodos que permitam explorar cooperativamente as técnicas da mecatrônica em uma abordagem de Integração de Sistemas.

O conjunto de aplicações típicas para este estudo compreende os projetos de grande porte sejam acadêmicos ou desenvolvimentos industriais, onde se tem a necessidade de conceber e validar um conjunto grande de componentes, cujas características amparam decisões de projeto e de um comportamento coletivo.

#### 2.1 Introdução

Nos dias atuais, a evolução tecnológica está direcionando uma grande gama de produtos na área de engenharia, acarretando em alterações drásticas na concepção de um projeto de um sistema mecatrônico no que diz respeito às evoluções do projeto e concepção mecânica, sistema de acionamento e de controle. Estes novos produtos mecatrônicos emergem da combinação

apropriada dos sistemas mecânicos, da eletrônica e do processamento em tempo real dos sistemas de controle e tratamento de informações através da implementação de diversificadas funções de controle embarcadas e integradas ao sistema. Como exemplos, podemos citar a intensidade crescente de componentes eletromecânicos inteligentes, de máquinas automatizadas, de veículos com grande número de sensores e eletrônica embarcada e de dispositivos mecânicos de precisão.

Um fator de grande importância industrial consiste na redução de tempo de desenvolvimento de um produto com a diminuição do número de etapas, gerando a produção de novos e diferenciados produtos. Isso é indispensável no mundo globalizado e particularmente necessário nas indústrias de alta tecnologia, como por exemplo, no que diz respeito à implementação de controladores cada vez mais rápidos e eficientes.

Muitos processos e produtos técnicos nas diferentes áreas da engenharia, principalmente na engenharia mecânica e elétrica, apresentam uma integração crescente dos sistemas mecânicos com processamento da eletrônica digital e de informação. O seu desenvolvimento envolve a busca de uma solução otimizada entre a estrutura mecânica básica, o sistema de sensoriamento e o elemento de atuação e controle, através do processamento automatizado de informações e controle global do sistema.

Tudo isso acarretará no desenvolvimento e utilização de ferramentas para o projeto simultâneo dos sistemas mecânicos e hardware de acionamento e controle, através da implementação do software e funções de controle embarcadas dentro de um ambiente de simulação, tendo como resultado e principal objetivo a eliminação da totalidade ou parte de protótipos intermediários e a geração de um componente ou um sistema integrado de controle. Para tal propósito descrito existe um conceito atual denominado prototipagem rápida de sistemas mecatrônicos.

A prototipagem rápida é uma ferramenta que permite a construção de protótipos de uma maneira econômica e segura. Esse conceito era muito utilizado anteriormente para a construção de protótipos de peças mecânicas a partir de um projeto desenvolvido em CAD (*Computer Aided Design*) ou da implementação de componentes eletrônicos em FPGA's a partir de um CAD de eletrônica. Mais recentemente, esse conceito é utilizado de forma mais ampla, envolvendo a concepção de todo um projeto de um sistema mecatrônico desde as fases de modelagem, simulação e arquitetura de controlador até a sua implementação final em hardware dedicado.

Consequentemente, a prototipagem rápida tem como objetivo a geração automática do código equivalente ao controlador para testar os sistemas reais, resultando em diminuição nos custos de implementação de um controlador, principalmente se esse for desenvolvido para um projeto específico, ou seja, a prototipagem rápida é uma ferramenta que possibilita a construção de protótipos de uma maneira econômica e segura, onde hardware pode ser implementado num sistema embarcado (*embedded system*) a partir de componentes virtuais.

Durante a implementação deste projeto de pesquisa, abordaremos conceitos de prototipagem rápida num contexto mais aberto, que inclui a implementação em ambiente virtual do modelo de um sistema mecatrônico (modelagem cinemática e dinâmica), simulação e hardware de supervisão e controle.

#### 2.2 Estado da Arte

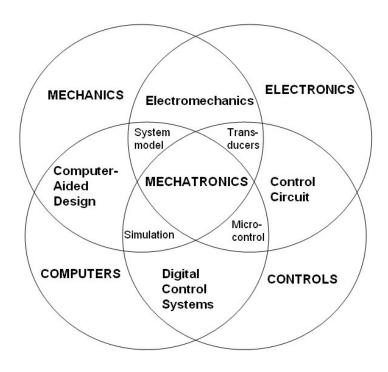

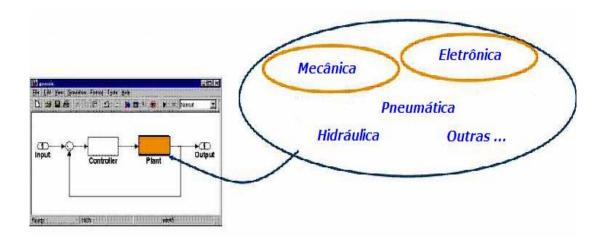

A Mecatrônica pode ser definida como um conjunto das técnicas que agregam inteligência a um sistema ou a uma máquina, através da integração entre a eletrônica e a tecnologia da informática com os sistemas mecânicos. Os principais domínios de aplicação são: os sistemas elétricos, eletromecânicos, os autômatos finitos programáveis, a pneumática, a hidráulica, os sensores e a domótica. Um sistema mecatrônico deve integrar a mecânica, circuitos analógicos, digitais, microprocessadores e computadores, sensores e atuadores além de algoritmos de comando e tecnologias da informação (figura 2.1).

Figura 2.1 : Definição do domínio da Mecatrônica (IFAC 2005).

Dado que o ciclo de vida do processo de *design*, arregimentando várias disciplinas é o verdadeiro núcleo da Mecatrônica, o controle sobre o processo de *design* é de fundamental importância. A validação de requisitos dentro deste processo é muito discutida em várias comunidades acadêmicas (Ciência da Computação e Engenharias Civil, Elétrica e Eletrônica, Controle e Automação, Térmica, e outras) e representa um desafio especial, dado que a viabilidade da automação de um determinado processo é parte deste ciclo. Por exemplo, para a automação de processos cirúrgicos, ferramentas dedicadas devem ser validadas antes mesmo de se pensar no *design* destas ferramentas ou mesmo da composição de um robô para este fim. Entretanto, a fase inicial do ciclo de vida, que compreende o ciclo informal de iniciação de requisitos e formulação das especificações, não tem dados suficientes para se entrar em cálculo de cinemática e dinâmica ou design mecânico de um dispositivo robótico.

Genericamente, os conceitos oriundos da eletrônica, do controle, do fluxo de informação ou da interação direta com usuário, utilizados para o *design* de qualquer sistema mecatrônico, aplicado a qualquer área, precisam ser investigados a fundo e ferramentas de apoio ao *design* destes processos colocados a disposição do setor de engenharia responsável por eles.

O aspecto colaborativo é essencial dado que qualquer abordagem Taylorista redundaria em entrave ao processo de projeto. O desenvolvimento dos prédios inteligentes e os obstáculos para a integração do projeto civil com o projeto de automação são responsáveis por redundâncias de instalação, custos muito superiores ao esperado e decepção com os resultados, para citar outro exemplo.

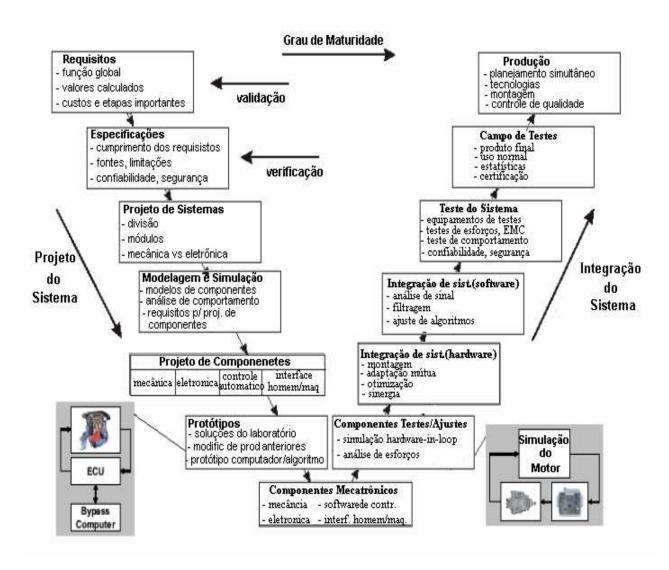

O ciclo de vida de um produto mecatrônico apresenta a integração entre a modelagem, controle e a realimentação, pensando em sistemas de malha fechada. A figura 2.2 mostra detalhadamente a base desta integração que pode ser fundamentada em ferramentas específicas (ou em um conjunto delas).

Figura 2.2: Ciclo em V – Metodologia para Concepção e Desenvolvimento para sistemas Mecatrônicos (Isermann, 2005).

O ciclo em V (Isermann, 2005), sintetiza as diferentes etapas associadas à concepção de um Produto, onde pode ser visto uma fase inicial de Projeto e Concepção (abrangendo fase de requisitos, especificações, modelo, componentes e prototipagem) e uma segunda fase de implementação final associada à Integração de Sistemas (abrangendo a integração final de hardware e de software, testes e certificações, produção e supervisão).

Os produtos mecatrônicos que queremos projetar têm dois aspectos fundamentais: possuem um grau de autonomia que pode variar desde um dispositivo comandado interativamente até um robô autônomo; tem características funcionais de um sistema dinâmico discreto ou híbrido, seja de maneira direta ou aproximada. Portanto, para ter um ciclo coerente para estes sistemas (que resultará em melhores produtos e em um *design* de menor custo) devemos tratar estes dois aspectos desde a fase inicial do ciclo, isto é, requisitos funcionais coerentes e válidos, chegando ao conceito de prototipagem rápida de sistemas mecatrônicos. A figura 2.3 apresenta o conceito de produto inteligente.

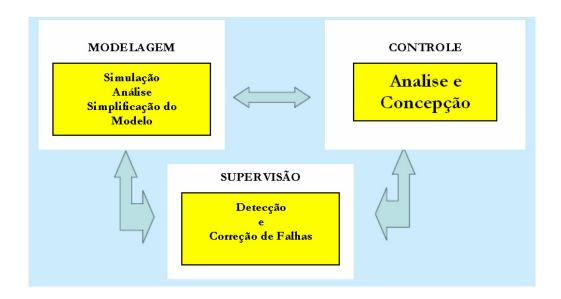

Figura 2.3: Concepção Integrada de um "Produto Inteligente"

## 2.3 O conceito de Prototipagem Rápida na Concepção de Sistemas Mecatrônicos

A prototipagem rápida, pode ser realizada em vários níveis de abstração, sendo a espinha dorsal do processo de concepção, onde os elementos de integração e de autonomia devem ser verificados a cada passo através de três etapas associadas a um ambiente gráfico interativo e à utilização de um conjunto de bibliotecas e blocos personalizados: modelagem do sistema físico,

visualização do modelo funcional e descrição do *software* a ser implementado em dispositivos eletrônicos ou microcontroladores.

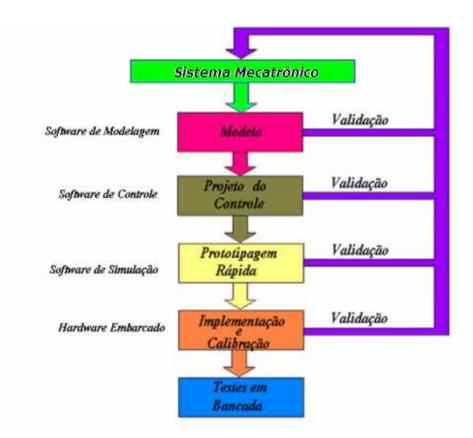

Figura 2.4: Fluxograma das diferentes fases de implementação de um sistema mecatrônico.

A figura 2.4 apresenta, sob forma de fluxograma, as diferentes fases de implementação de um dispositivo mecatrônico a partir de um modelo. Podemos observar a existência de várias etapas para a concepção de um sistema de controle utilizando a técnica de prototipagem rápida. Para a diminuição de custos, a maior parte da concepção resulta de simulações antes da implementação real. Deste modo, o desenvolvimento de um ambiente virtual que permita analisar o melhor desempenho do algoritmo de controle a ser implementado se faz necessário.

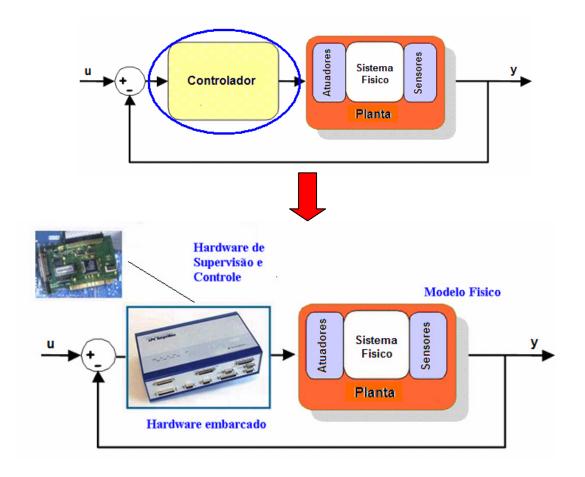

Figura 2.5: Princípio da Prototipagem Rápida de Sistemas Mecatrônicos.

A figura 2.5 exemplifica as diferentes fases da concepção de um sistema mecatrônico através do exemplo de prototipagem rápida de um controlador de juntas de um robô industrial com seis graus de liberdade. Neste exemplo, pode-se observar uma fase inicial referente à simulação do movimento cinemático dos diferentes graus de liberdade do robô e o projeto do sistema de controle referente a cada junta robótica, sendo considerados os acoplamentos dinâmicos entre as juntas implementados em simulador, para posterior prototipagem do sistema de controle através de hardware embarcado.

Em Ollero et al, 2005, é mostrada uma análise no desenvolvimento e concepção de sistemas mecatrônicos com o progresso tecnológico dos últimos anos, tais como a inovação na área de componentes, bem como a melhoria de softwares para aplicação na solução de sistemas embarcados, com a sinergia de várias de áreas de conhecimentos.

## 2.4 Modelagem de Sistemas Físicos

A fase de modelagem e controle de sistemas físicos exige a utilização de um conjunto de ferramentas para modelagem intuitiva e de fácil utilização, a partir de um ambiente virtual de simulação de sistemas físicos. Estas ferramentas direcionadas a engenheiros de concepção e análise de sistemas físicos deverão possibilitar a concepção de um modelo físico simplificado, próximo ao modelo real, permitindo a sua implementação em tempo real e atendendo os níveis de precisão exigidos para o desenvolvimento do modelo.

A modelagem de sistemas físicos necessita de ferramentas que facilitem a implementação do modelo de sistemas associado a sua arquitetura de controle de maneira rápida e precisa, acarretando a diminuição do tempo relativo às fases de implementação e testes, como também uma maior precisão na formulação e implementação de modelos de planta mais realísticos.

Estas ferramentas deverão dar suporte, através de bibliotecas de blocos hierarquizados, a funções dedicadas à mecânica, sensores, atuadores e outros elementos, que permitirão a modelagem de componentes mecatrônicos de corpos rígidos e seus acoplamentos dinâmicos,

sistemas de coordenadas, análise de parâmetros físicos: posição, força, análise cinemática e dinâmica dos sistemas mecânicos (fígura. 2.6).

A partir da modelagem completa do sistema mecânico que se deseja controlar, faz-se o projeto do controlador utilizando a técnica de controle que melhor se adapte à estrutura estudada ou qualquer método que se pretenda utilizar. Dessa forma, o modelo acentua a concepção do sistema, tornando possível a validação da lei de controle em ambiente de simulação próximo ao real, suportando a concepção e integração do controlador para sistema físico, com a associação de um componente a outro.

Figura 2.6: Conceitos a serem implementados na planta baseados na modelagem de sistemas físicos.

Dentre os aplicativos comerciais, podemos citar a MathWorks® que elaborou ferramentas com esta capacidade, de modo a permitir o desenvolvimento completo de um sistema mecatrônico dentro do SIMULINK®. Estas ferramentas permitem a modelagem dos componentes mecânicos, simulação dos movimentos e análise direta dos resultados sem ter que derivar as equações do sistema e ainda realiza a modelagem das montagens mecânicas e seus controladores dentro de um mesmo ambiente SIMULINK®, ou seja, eliminam as interfaces "pesadas", diminuem o ciclo de concepção e proporcionam criação de algoritmos de controle mais convenientes. As principais funcionalidades são as seguintes:

- Implementação de diagrama de blocos equivalentes às equações diferenciais que descrevem os sistemas físicos ou blocos dedicados.

- Modelagem de bibliotecas utilizando outras ferramentas de concepção já existentes no mercado (ADAMS®, PRO-ENGINEER®, AMESIM®, etc.).

## 2.5 Implementação do Sistema de Controle

Com o rápido desenvolvimento de novas tecnologias, sobretudo no que concerne à informática e à eletrônica, pode-se aprimorar a pesquisa científica e tecnológica na área da engenharia mecatrônica. Entretanto, a implementação de robôs para aplicações específicas requer normalmente um elevado custo investimento financeiro até chegar ao desempenho apresentado pelos fabricantes, sendo que os equipamentos acabam tornando obsoletos e com uma grande depreciação. O desempenho de um controlador exige que sua concepção esteja fortemente ligado ao modelo físico da planta associada, exigindo constantes atualizações de seu controlador (hardware/software) e aquisição de dispositivos externos a serem integrados no controlador do robô, nem sempre possíveis de serem realizadas pelo usuário.

Com isso, torna-se imprescindível o estudo e aprimoramento de técnicas de controle de sistemas mecatrônicos, com ênfase na sua implementação em tempo real a partir de microprocessadores e microcontroladores industriais. Assim, dentro do estudo da prototipagem rápida, os seguintes aspectos deverão ser implementados:

- Ambiente de prototipagem que represente um modelo muito próximo ao modelo real,

ocasionando um menor tempo de execução e com custos relativamente mais baixos.

- Desenvolvimento de algoritmos de controle que admitam algoritmos complexos e inteligentes para serem processados num tempo mínimo.

- Ferramentas inteligentes para auxiliar o modelamento e que sejam de fácil utilização.

- Integração e concepção do sistema, implementação e validação de algoritmos de controle/comando,

Arquitetura modular, através de blocos de funções de transferência, de modo a associar um componente aos outros e que sejam facilmente reconfigurável.

Portanto, a utilização de um ambiente único para cálculo científico, análise de dados e visualização, modelagem de sistemas e simulação; implementação de lógica embarcada em tempo real através da implementação de um sistema completo da fase de concepção até a eletrônica embarcada, pode ser realizada pelo Matlab/Simulink®, que facilita o trabalho em grupo dos projetistas de controle.

A implementação de um controlador de um sistema mecatrônico através de prototipagem rápida apresenta inúmeras vantagens, dentre elas o fato dos circuitos eletrônicos serem programados de maneira rápida, segura e otimizada, e ainda, de maneira personalizada: Simulação *Hardware In the Loop* (HIL).

Uma das principais vantagens dos sistemas de prototipagem rápida é que após a simulação do modelo virtual do sistema, o sistema total ou partes desse modelo poderão ser facilmente trocados pelo *hardware* de controle real para validação e testes do modelo, de modo que o protótipo virtual se transformará num produto muito próximo do real, simplificando etapas de concepção, validação e testes. Conseqüentemente, após a fase de simulação do sistema, que deverá incluir o modelo virtual do *hardware*, esta parte do modelo poderá ser trocada pelo *hardware* real, similar ao modelo virtual, fazendo que o *hardware* passa ser integrado no modelo de simulação virtual e possibilitando o estudo do comportamento do novo componente com o resto do sistema, em particular o estudo do comportamento global do sistema.

Essa fase de testes é chamada de *Hardware In the Loop* (HIL), que deverá permitir a integração do hardware físico dentro do ambiente de simulação. As principais ferramentas necessárias para realização desse procedimento são as seguintes:

• Ferramentas de programação e hardware aberto para implementação do protótipo;

- Unidade de cálculo que permita assegurar a comunicação com o hardware e a área de trabalho, que deverá comportar: portas de entradas e saídas, conversores analógico/digital e digital/analógico.

- Implementação de programa que permita a importação de modelos representando o sistema e que seja capaz de gerar as entradas e programável por blocos.

As aplicações do HIL são utilizadas para avaliar e validar os elementos desenvolvidos por um novo sistema. Elas consistem em testar esses elementos, antes de concretizar o sistema real, a partir unicamente da simulação do resto do sistema. Os componentes do hardware testados respondem aos sinais enviados pelo computador e simulam o resto do sistema, como se encontrassem dentro de um sistema real.

Atualmente existem várias empresas que oferecem soluções que realizam o *hardware in loop* (HIL), como por exemplo: dSPACE®, National Instruments® (NI), Altera® e Opal-RT® que apresentam produtos dedicados a prototipagem rápida.

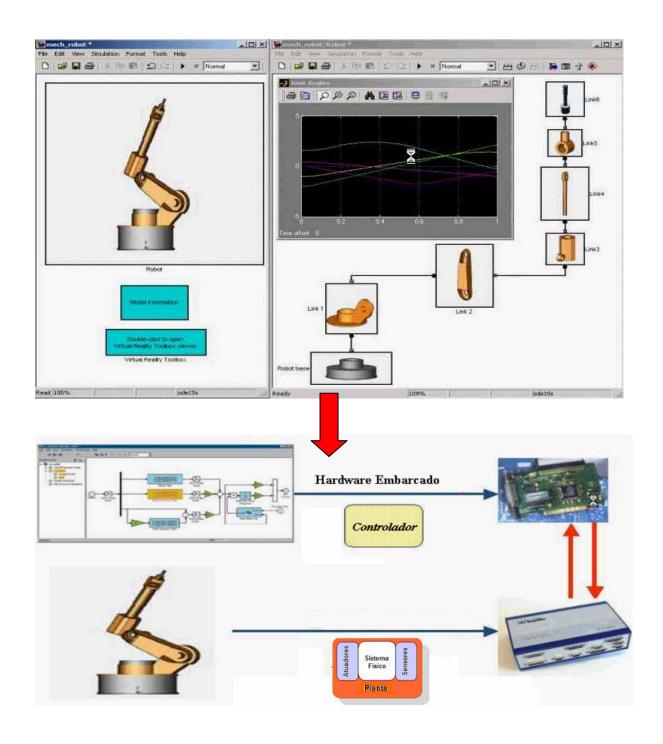

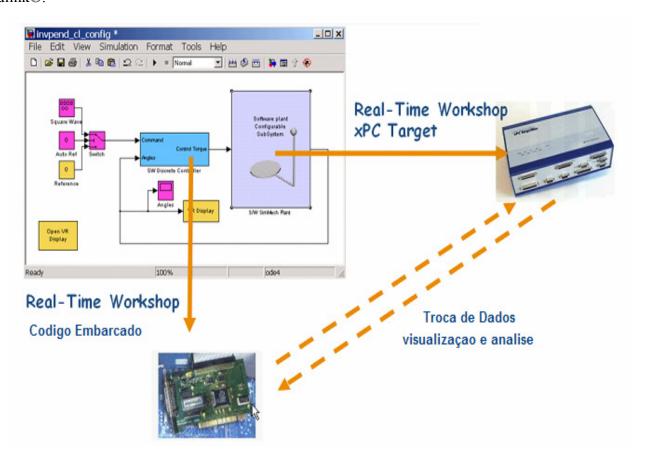

A figura 2.7 apresenta esquematicamente um exemplo de implementação através do ambiente MathWorks® utilizando HIL. Neste exemplo, observa-se que a partir do ambiente de simulação utilizado para validação e testes do modelo físico implementado, o hardware de controle poderá ser gerado e incorporado dentro do simulador, para validação e testes dentro desse mesmo ambiente de prototipagem.

Figura 2.7: Hardware In the Loop através do Mathworks®.

As principais etapas a serem implementas no HIL são as seguintes:

- Desenvolvimento de um programa de simulação usando ambiente tal como o Matlab/Simulink®;

- Configuração das entradas e saídas necessárias para o funcionamento do sistema simulado com o elemento hardware;

- Geração automática do código (com possibilidade de troca de parâmetros em tempo real e iniciação imediata da simulação em HIL);

- Visualização dos resultados em tempo real.

Dentre as principais dificuldades na utilização do HIL podemos destacar:

- Nível de integração de plataformas e interfaces utilizadas;

- Simulação diferenciada: sincronização e tempo de simulação;

- Atualização constante de diferentes softwares e compatibilidade;

- Utilização frequente;

- Criação de interfaces com ferramentas do mercado existentes nem sempre é evidente.

A figura 2.8 apresenta um exemplo completo de implementação *Hardware in Loop* (HIL) para um sistema mecatrônico, onde partes do modelo físico são geradas no ambiente Matlab-Simulink®.

Figura 2.8: Esquema de prototipagem do controlador.

#### 2.6 Simulador Virtual

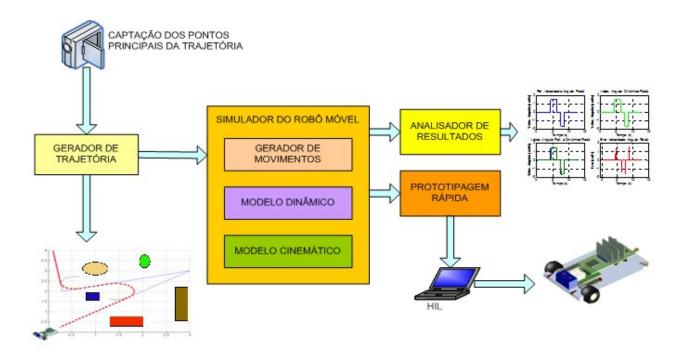

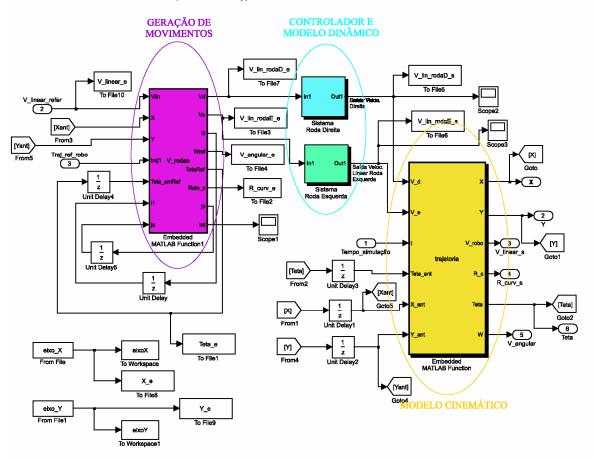

Como exemplo de desenvolvimento de um Simulador Virtual para Prototipagem de um sistema de controle de dispositivos mecatrônicos pode citar o trabalho de Melo, 2007, utilizou os conceitos de prototipagem rápida para implementação de um ambiente virtual para simulação de um sistema de supervisão e controle para robôs móveis capazes de operar e de se adaptar a diferentes ambientes e condições de trabalho.

A implementação desse simulador considerou aspectos relacionados à modelagem cinemática e dinâmica e controle de sistemas robóticos móveis, que permitiu a escolha de um modelo, considerando suas capacidades e limitações, possibilitando ainda uma proposta de arquitetura aberta de supervisão e controle que integre as melhores características das técnicas que existem atualmente.

A figura 2.9 apresenta as diferentes fases de implementação de um projeto a partir da concepção de um modelo físico utilizando o conceito de prototipagem rápida. Através de um simulador virtual é executada a simulação de hardware e software do sistema mecatrônico em estudo. Este procedimento deverá acarretar uma diminuição de tempo de desenvolvimento do produto e de seu custo, resultando em testes relevantes durante a fase de validação e conseqüente diminuição de possíveis erros que ocorrem durante o processo de implementação e testes.

Figura 2.9: Simulador Virtual dentro do processo de Prototipagem Rápida.

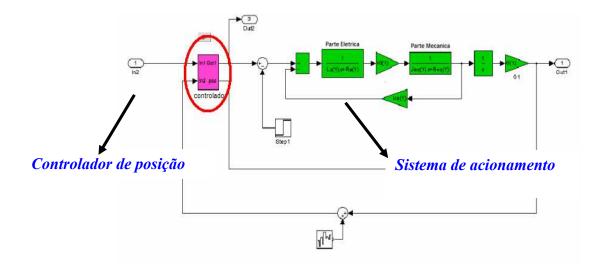

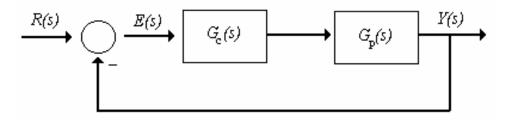

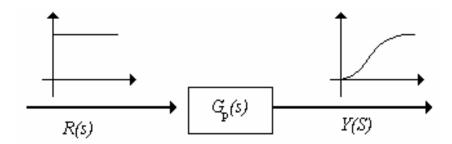

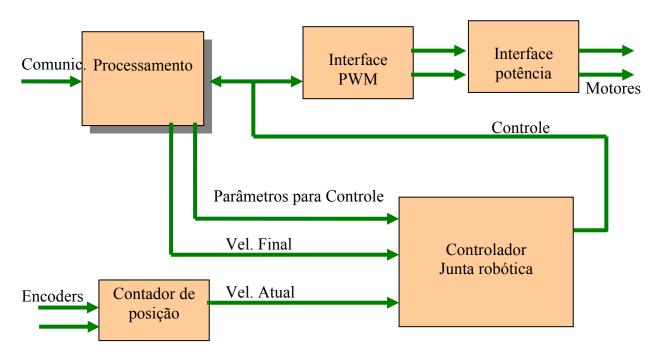

O sistema de controle, que consiste em malha de controle em cascata para cada grau de liberdade do sistema mecatrônico, será ser implementado em blocos do Simulink®. O conjunto de malhas de controle de posição, velocidade e torque podem fazer parte do modelo do sistema de acionamento e controle de uma junta robótica. O controle de posição de cada grau de liberdade do dispositivo será implementado através de realimentação para cada junta isolada, requerendo o modelo dinâmico de cada junta.

Durante o desenvolvimento desse projeto de pesquisa será implementada a malha de controle de posição acoplada ao modelo completo de uma junta robótica, conforme mostra a figura. 2.10, utilizando arquitetura aberta, de modo à facilmente serem implementados diferentes estratégias de controle, para posterior simulação, análise e comparação de desempenhos.

Figura 2.10: Malha de acionamento e controle de posição de uma junta.

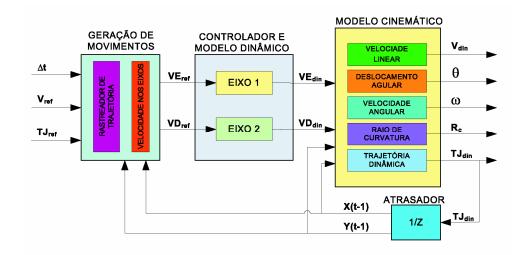

Outros elementos do sistema mecatrônico (incluindo possíveis cargas externas) serão representados por modelos não-lineares, um para cada acionador. A figura 2.11 apresenta a proposta de simulador implementado no trabalho Melo, 2007. Este simulador possui os seguintes módulos:

- Geração de trajetórias: geração de sinais de referência das juntas para cada controlador.

- Sistema de Acionamento: modelo eletro-mecânico do dispositivo e projeto do controlador de posição.

- Cinemático: modelo do sistema mecatrônico em estudo foi implementado utilizando funções "S-function", dentro do ambiente Matlab® integrados nos blocos do Simulink®.

- Interface Gráfica: visualização temporal das saídas e entradas do sistema em estudo.

Para melhor compreender e analisar o comportamento espacial do sistema torna-se imprescindível a implementação de um simulador gráfico de movimentos espaciais, mostrando resultados dos movimentos obtidos através de trajetórias de referência.

## a) Diagrama de Blocos Funcionais

b) Implementação em Ambiente Matlab-Simulink®.

Figura 2.11: Simulador de um Robô Móvel.

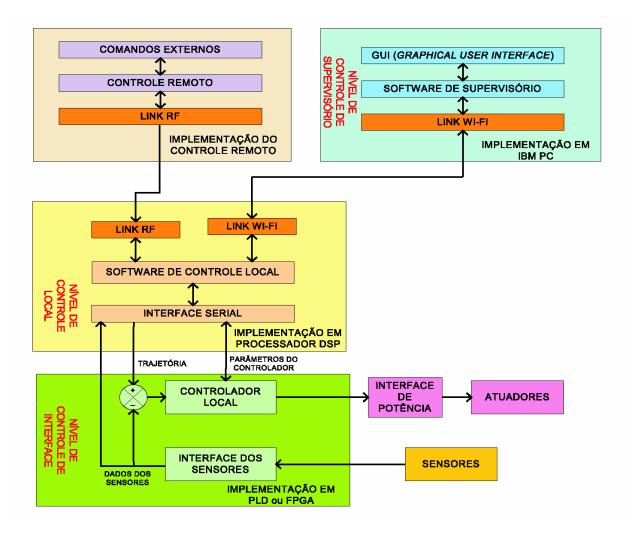

## 2.7 Sistema de Supervisão e Controle

O ambiente gráfico LabVIEW<sup>TM</sup> é muito utilizado industrialmente em projetos de dispositivos relacionados as áreas de medição e controle, possibilitando assim a criação de aplicações personalizadas que rodam em plataformas NI (National Instruments) com E/S reconfiguráveis baseadas em FPGAs. Juntos, o LabVIEW<sup>TM</sup> FPGA e o hardware NI, permitem a criação de uma plataforma flexível para o desenvolvimento de sistemas sofisticados que antes somente eram possíveis com hardware projetado de forma dedicada.

O software LabVIEW<sup>TM</sup> pode ser usado para implementação do sistema de supervisão e controle de movimentos, residente num computador e responsável pelo gerenciamento e controle das informações provenientes de sensores e atuadores do sistema.

A figura 2.12, apresenta uma proposta de interface de visualização para sistemas robóticos móveis, implementada em ambiente gráfico, possuindo telas de supervisão que coletam as informações dos sensores, dos programas de tratamento matemático (modelagem cinemática) e as informações sobre o sistema (inicialização, velocidade, parâmetros do regulador, números de pontos da trajetória, etc).

Figura 2.12: Proposta de interface de visualização para sistemas robóticos móveis.

## 2.8 Sistemas Reconfiguráveis

Sistemas reconfiguráveis são sistemas que têm como principal característica a capacidade de adaptar-se a tarefas específicas através da substituição de parte de seu software ou hardware, possibilitando assim obtermos alto desempenho com baixo custo de produção, sendo uma alternativa às máquinas de Von Neumman implementadas nos sistemas com microprocessadores. Sistemas reconfiguráveis por *software* são bastante comuns, sendo exemplos os sistemas embarcados em automóveis, eletrodomésticos, vídeo games dentre outros. Nestes sistemas, a

mudança de uma ROM ou de um CD-ROM leva à reconfiguração de funções responsáveis pela operação dos mesmos [Miyazaki 1998].

Sistemas com hardware reconfigurável são mais recentes e estão associados ao aparecimento das FPGA (*Field Programmable Gate Array*) na década de 90. No trabalho de Page, [Page, 1996] é proposta a união em um único circuito integrado de um microprocessador e uma FPGA para atender dinamicamente novas aplicações.

Comparados aos sistemas de software reconfiguráveis os sistemas de hardware reconfiguráveis apresentam um maior potencial em termos de desempenho e adaptabilidade. Outras siglas estão associadas aos sistemas de *hardware* reconfigurável: CCM (*Custom Computing Machines*) ou FCCM (*FPGA-based Custom Computing Machines*). As expressões computação reconfigurável e lógica reconfigurável também estão associadas a sistemas de hardware reconfiguráveis.

Tradicionalmente, a execução de um algoritmo na computação convencional pode seguir dois métodos de utilização:

- a) Tecnologia de hardware, a exemplo de ASICs (*Application Specific Integrated Circuits*) ou de placas de circuito impresso; apresenta como vantagem altas velocidades de execução, mas pouca flexibilidade a modificações;

- b) Microprocessadores programáveis por *software*: apresenta alta flexibilidade para modificações, mas não é executado com a mesma velocidade dos algoritmos programados em hardware [Compton, 2002]

O fato dos microprocessadores executarem de forma sequencial suas tarefas (máquina de Von Neumann) faz com que os algoritmos programados por *software* tenham tempos de processamento que não são aceitáveis para muitas aplicações [Pimentel e Le-Huy, 2000, Dido et al., 2002].

A computação reconfigurável tem por objetivo suprir a lacuna entre a solução por *software* e a solução por *hardware*, atingindo desempenhos muito superiores aos desempenhos obtidos por *software*, mas obtendo uma flexibilidade muito maior que a flexibilidade obtida com uma solução por *hardware* [Chen et al., 2000, Compton, 2002 e Coric et al., 2002].

Os sistemas embarcados estão sujeitos a grandes variações tecnológicas num curto espaço de tempo, ocasionada pela demanda de novas tarefas e desempenhos, e disponibilidade de novas tecnologias de sensores e atuadores, sendo comum para estas aplicações a utilização de blocos funcionais de software testados e validados, reduzindo assim, o tempo de projeto de um sistema (API – *Application Program Interface*).

No que concerne a implementação através de hardware existem blocos funcionais que podem assumir a mesma função. Estes blocos podem ser combinados com outros circuitos para programar um determinado algoritmo. Este aspecto modular permite facilitar a manutenção e a atualização de projetos [Compton, 2002, Renner et al., 2002 e Coric et al., 2002]. A utilização de IP-CORE (*Intellectual Property Cores*), permite a integração de soluções já desenvolvidas por diversos fornecedores para minimizar o tempo de projeto. Como exemplos de IP-CORE disponíveis [Ito e Carro, 2000, Kean,2000 e Diniz e Park, 2002] podem destacar os barramentos PCI, interfaces de comunicação, e funções de processamento de sinal, como FFT (*Fast Fourier Transform*), codificação e decodificação de imagens digitais e mesmo Microprocessadores e DSPs.

As PLDs (*Programmable Logic Devices*), também chamadas de EPLD (*Erasable Programmable Logic Devices*), ou ainda CPLD (*Complex Programmable Logic Devices*), e as FPGA (*Field Programmable Gate Array*) ou DFGA (*Dinamically Field Programmable Gate Array*) são dispositivos que permitem a execução de algoritmos diretamente em hardware. Com estes dispositivos programáveis é possível executar os algoritmos explorando o paralelismo inerente da solução por hardware, executando-os muito mais rápido do que se os mesmos algoritmos fossem executados de forma seqüencial por microcontroladores ou por DSPs, sujeitos ao modelo de Von Neumann. As PLDs e FPGAs apresentam diferenças quanto à aplicação e

quanto à estrutura interna. As FPGA são geralmente aplicadas em sistema com menor sensibilidade ao custo e de maior complexidade. [Miyazaki 1998, Pimentel e Le-Huy, 2000]. Miyazaki apresentada uma notação para classificação dos tipos de dispositivos lógicos:

- Lógica configurável: dispositivos lógicos que podem ser "customizados" uma única vez.

- Lógica reconfigurável: dispositivos que podem ser customizados mais de uma vez, que adotam tecnologias EPROM, EEPROM ou FLASH e podem ser reprogramados após serem montados em uma placa de circuito impresso.

- Lógica dinamicamente reconfigurável: dispositivos que permitem sua reprogramação durante a operação, mesmo após a montagem em uma placa de circuito impresso. Esta propriedade é chamada de reconfiguração *in-circuit*.

- Interconexão dinamicamente reconfigurável: expressão para dispositivos interconectados que podem ser programados por conexões pino a pino após a montagem em placa de circuito impresso.

- Lógica virtual: dispositivos dinamicamente reconfiguráveis que apresentam uma capacidade parcial de reconfiguração, onde apenas parte do dispositivo pode ser reprogramado enquanto a outra parte do dispositivo executa alguma função definida, ou seja, diferentes circuitos lógicos podem compartilhar ao longo do tempo uma mesma parte do dispositivo. São também chamados de dispositivos de lógica adaptativa ou dispositivos de lógica compartilhada.

Dentre as principais vantagens dos dispositivos lógicos estão o paralelismo, velocidade [Aporntewan e Chongstitvatana, 2001], capacidade de atualização, padronização de plataformas, amortização do custo de desenvolvimento e alto desempenho. Dentre as poucas desvantagens estão em ambientes de desenvolvimento pobres se comparados com os ambientes de desenvolvimento de processadores.

Paralelamente ao desenvolvimento de dispositivos que permitiram a implementação da computação reconfigurável, ambientes de projeto, depuração, simulação e testes foram desenvolvidos pelos diversos fabricantes. Estes ambientes permitem a criação de módulos desenvolvidos com linguagens de alto nível de abstração, chamadas linguagens de descrição de hardware, a exemplo de VHDL (VHSIC Hardware Description Language), Verilog e AHDL (Altera Hardware Description Language).

A linguagem VHDL é padrão IEEE (std 1076) para descrição de hardware, a qual propicia um ambiente integrado que possibilita o projeto, a simulação, o teste e a documentação de circuitos digitais, ou seja através da mesma podemos implementar blocos com representações de mais baixo nível de abstração, a exemplo de esquemáticos (linguagem gráfica).

A integração de blocos criados com diferentes linguagens permite a criação de projetos de forma bastante flexível, facilitando a interação entre os membros de uma equipe de trabalho. A síntese dos circuitos lógicos em FPGA é feita através de sistemas CAD (*Computer Aided Design*), permitindo a utilização de diferentes interfaces de projeto. Dentre as principais vantagens da metodologia de projeto baseado em FPGA e VHDL podemos destacar:

- Maior facilidade na interação de uma equipe de trabalho.

- Diminuição do tempo de projeto, com possibilidades de eventuais correções e de integração de novas versões.

- Opera de forma paralela, que pode ser considerada como a característica mais vantajosa em relação aos microprocessadores. Não obedece ao modelo de Von Neumann.

- Permite o desenvolvimento modular e hierárquico de um projeto.

- Existência diversas interfaces de desenvolvimento, baseadas em linguagens gráficas (esquemáticos) ou em linguagens de descrição de hardware (VHDL, Verilog, AHDL).

- Permite as abordagens de projeto *top-down* e *bottom-up*.

Permite a utilização de funções pré-testadas (IP-CORE), diminuindo o tempo de projeto.

Diversos fabricantes de sistemas de desenvolvimento e de dispositivos lógicos reconfiguráveis disputam o mercado mundial. Entre os fabricantes de *Hardware* destacam-se Altera, Xilinx, Atmel, Triscend e Actel, e desenvolvedores de *software* apresentam produtos CAD de suporte ao desenvolvimento de projetos: Mentor Graphics, Synopsys e Accolade.

## 2.9 Exemplos de Aplicações de Sistemas Reconfiguráveis

A seguir apresentaremos diversas aplicações utilizando computação reconfigurável nas mais diversas áreas da Engenharia, dentre as quais: Sistemas de Comunicação, Controle, Manipulação Matemática, Tolerância a falhas, Criptografía:

- a) Projeto do sistema de controle do veículo *Pathfinder*, enviado ao planeta Marte pela NASA (Woerner e Lehman, 1995);

- a) Controle de inversores de potência utilizando FPGA (De Pablo et al., 1997).

- b) Implementação do sistema de controle para um motor de indução usando linguagem VHDL (Empringham et al., 2000, Cirstea et al., 2000, 2001);

- c) Controle adaptativo fuzzy de motor utilizando linguagem VHDL (Changuel et al., 1996);

- d) Projeto de um sistema de controle digital utilizando FPGA para uma cadeira de rodas (Chen et al., 2000, Lima, 2003);

- e) Implementação de algoritmos em *hardware* para acelerar o processamento de imagens médicas para tomografia computadorizada (Coric et al., 2002);

- f) Implementação de algoritmos de controle de aceleração e frenagem para motores de CNC e robôs industriais usando VHDL (Endemano, 2002, Jeon et al., 2002);

- g) Controladores de motor AC usando FPGA (Kharrat et al., 1998).

- h) Sistema de análise de tolerância às falhas baseado em ferramentas implementadas em VHDL (Baraza et al., 2002);

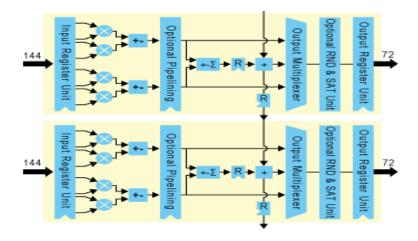

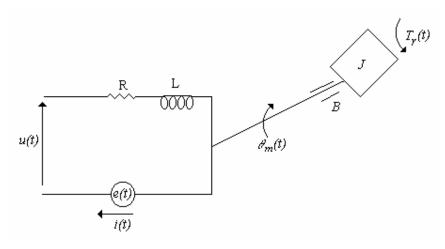

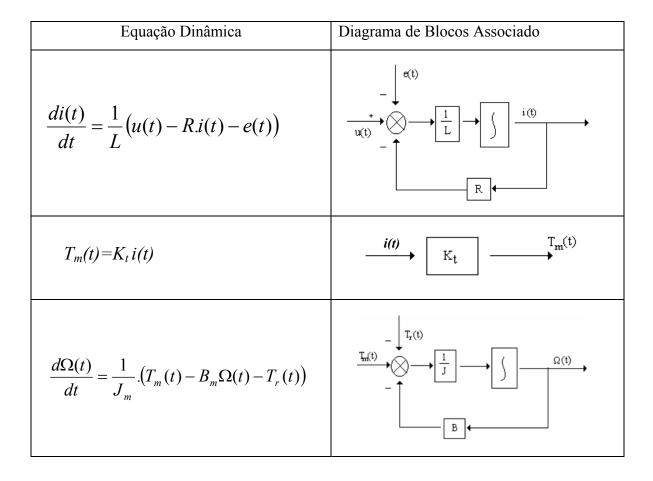

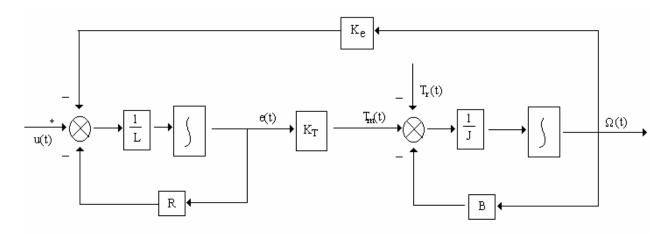

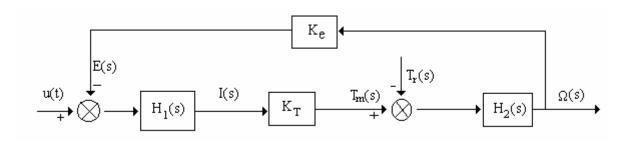

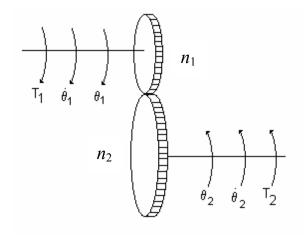

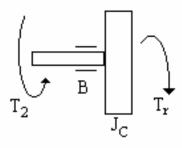

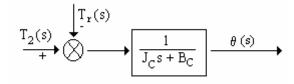

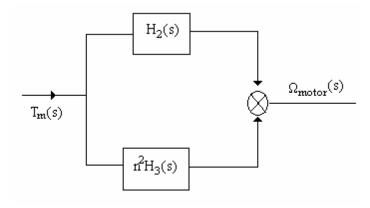

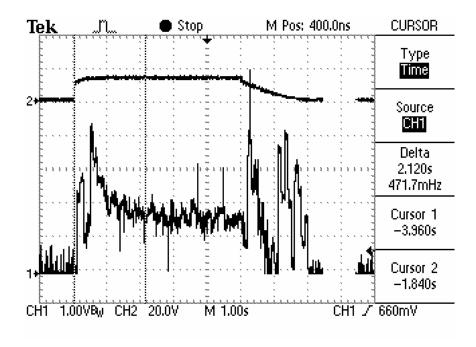

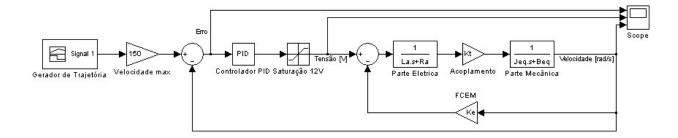

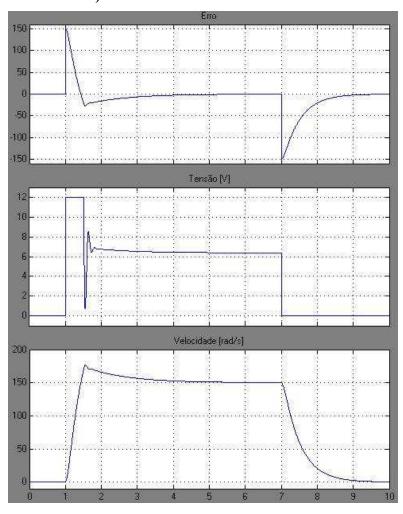

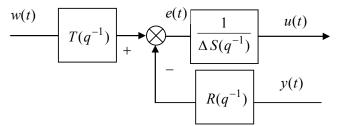

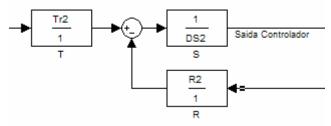

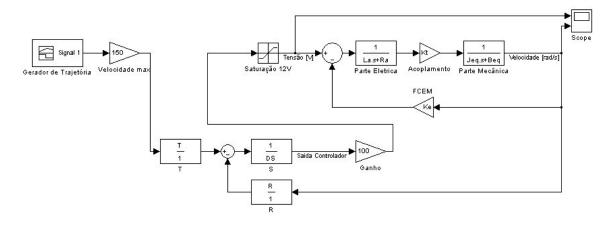

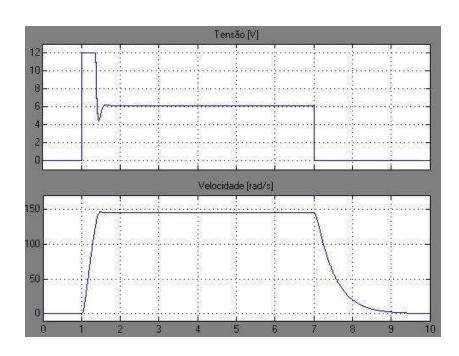

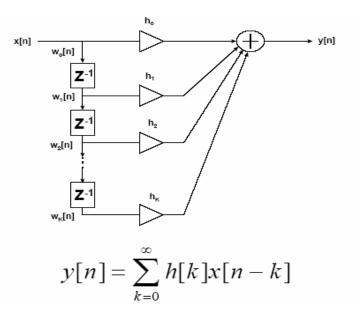

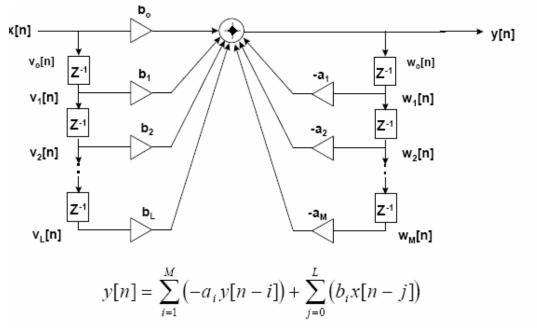

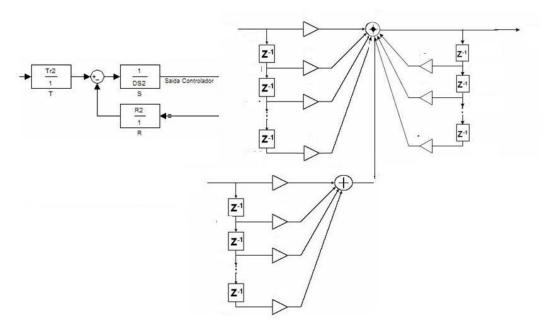

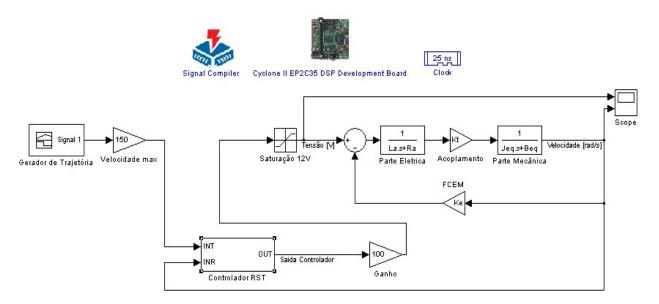

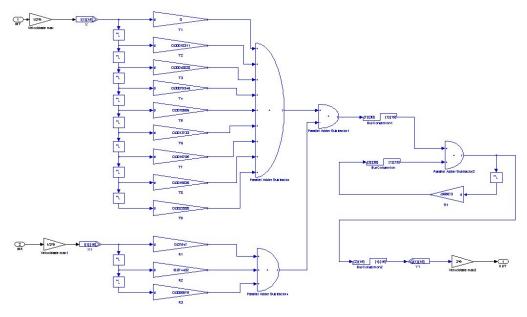

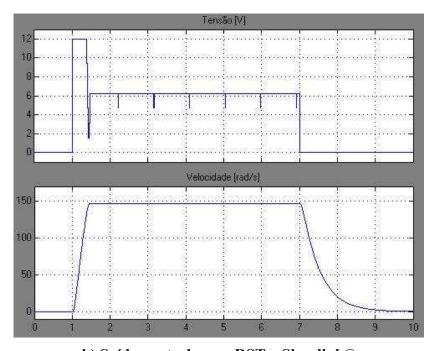

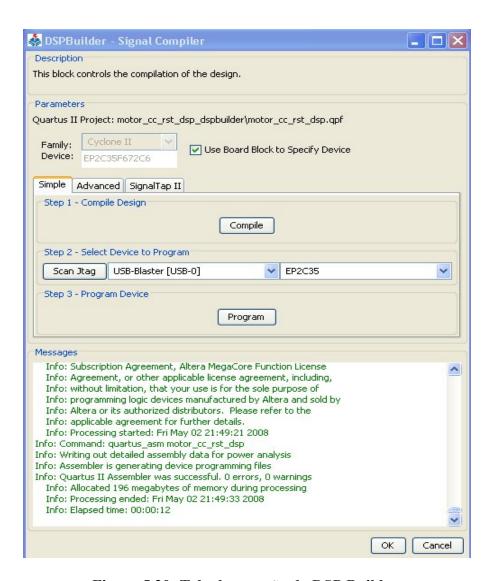

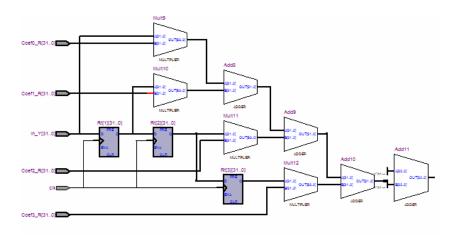

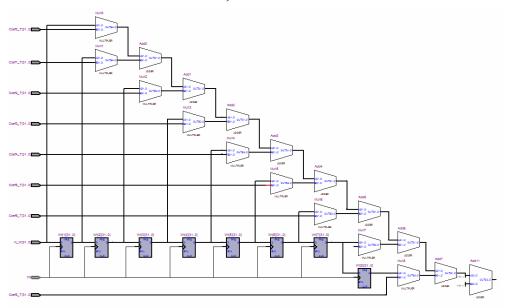

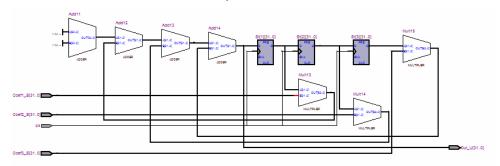

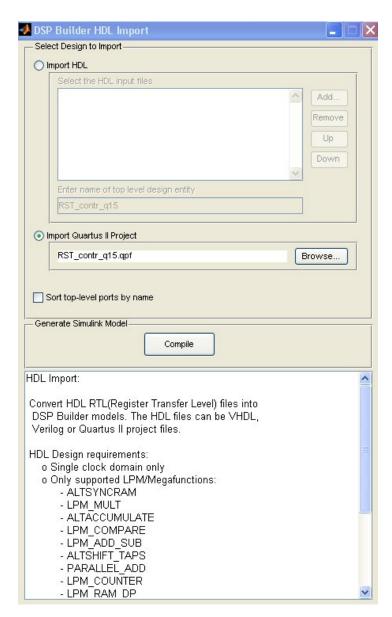

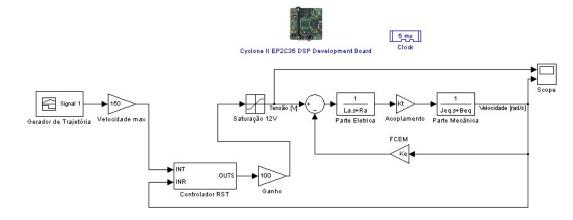

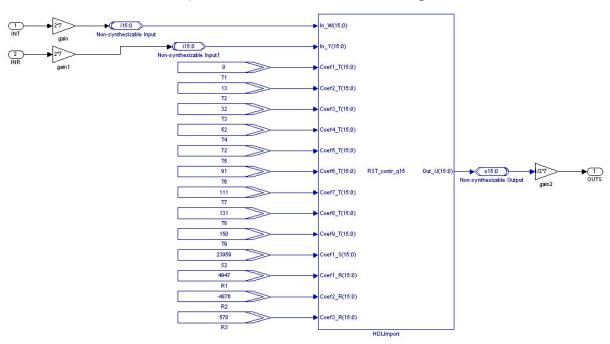

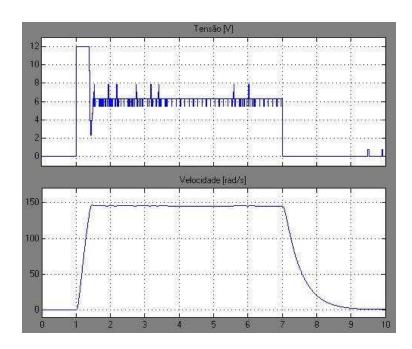

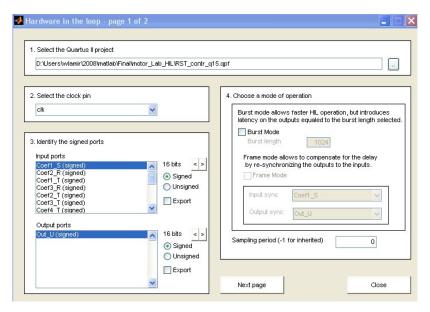

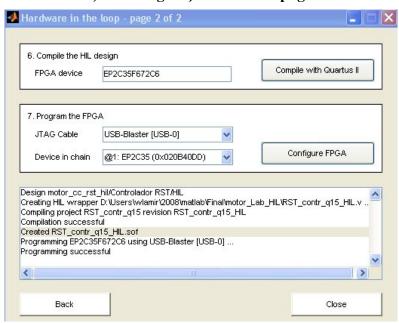

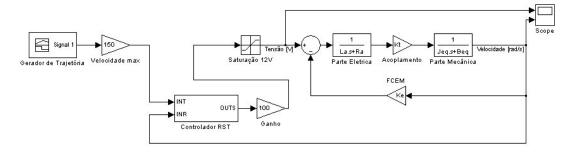

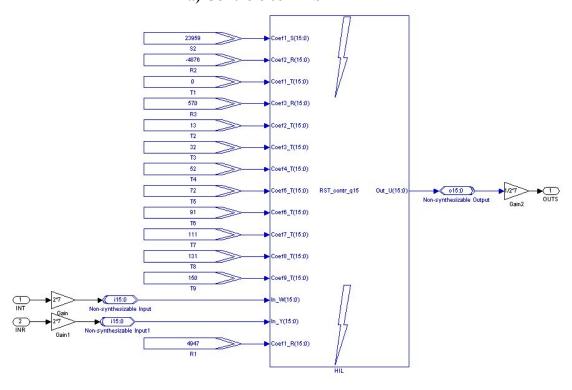

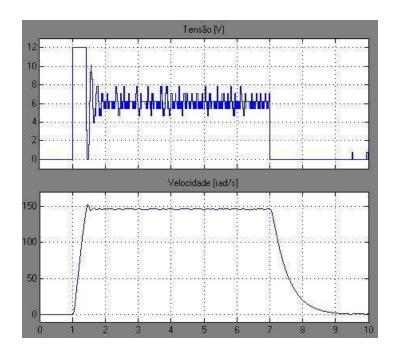

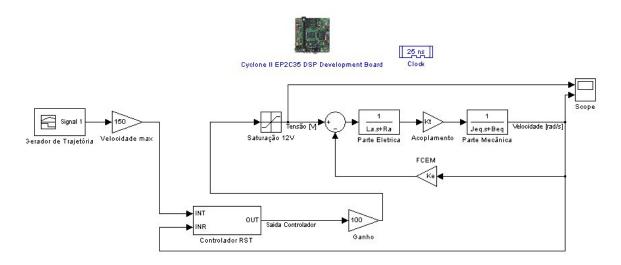

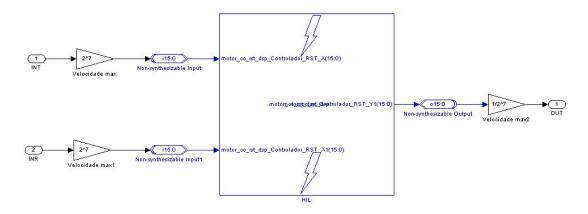

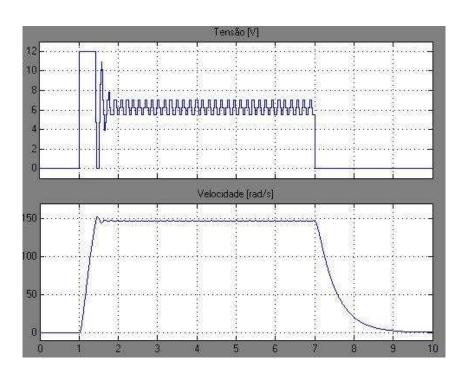

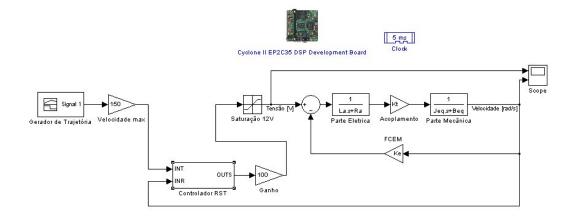

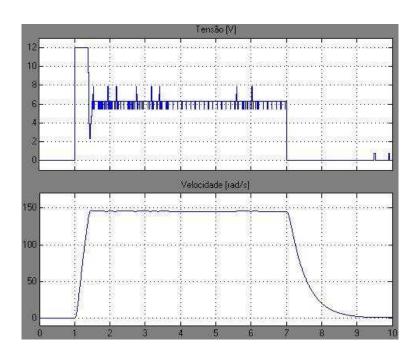

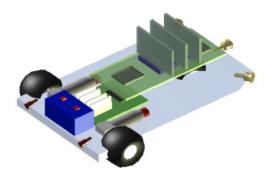

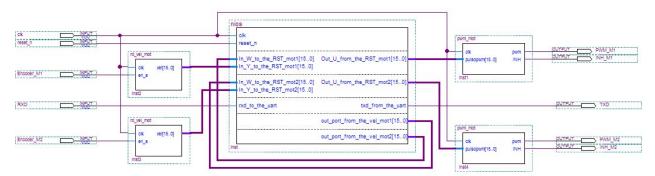

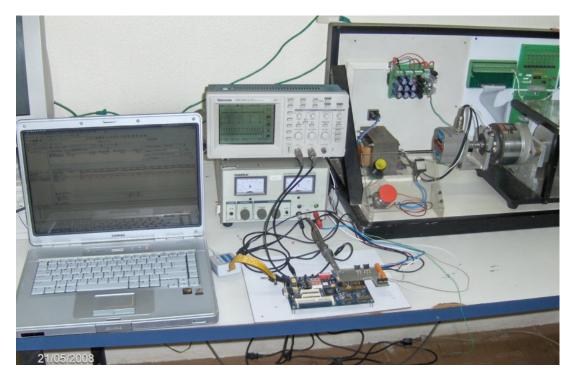

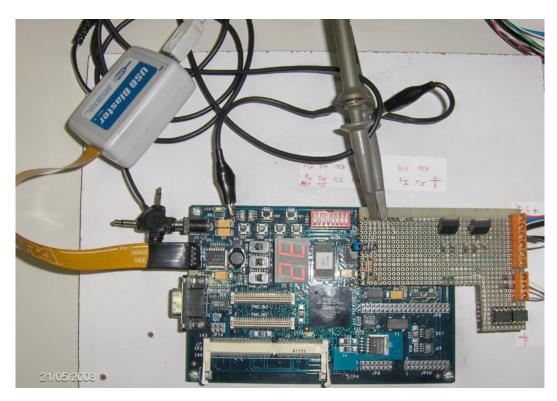

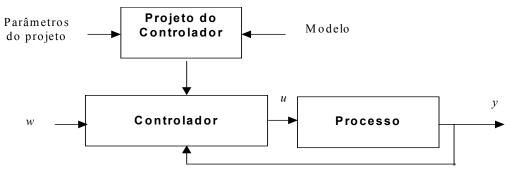

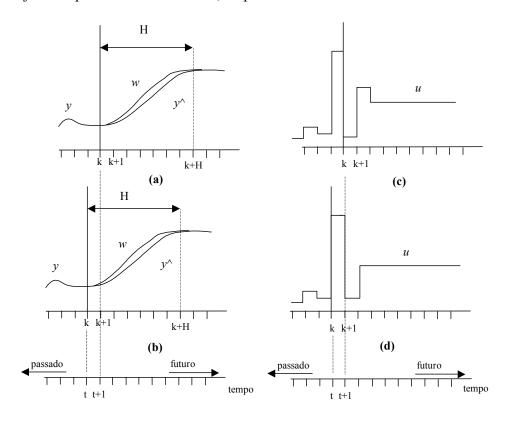

- Algoritmos de processamento de sinal de vídeo de alta resolução (HDTV) (Dido et al., 2002);