## Alessandra Leonhardt

# FinFET Prototype Fabrication Using Alternative Methods

Fabricação de Protótipos de FinFETs Usando Métodos Alternativos

Campinas

#### Alessandra Leonhardt

# FinFET Prototype Fabrication Using Alternative Methods

# Fabricação de Protótipos de FinFETs Usando Métodos Alternativos

Dissertação apresentada à Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas como parte dos requisitos exigidos para a obtenção do título de Mestra em Engenharia Elétrica, na área de Eletrônica, Microelectrônica e Optoeletrônica.

Supervisor: Prof. Dr. Leandro Tiago Manera

Co-supervisor: Prof. Dr. José Alexandre Diniz

Este exemplar corresponde à versão final da tese defendida pela aluna Alessandra Leonhardt, e orientada pelo Prof. Dr. Leandro Tiago Manera

Campinas

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca da Área de Engenharia e Arquitetura Elizangela Aparecida dos Santos Souza - CRB 8/8098

Leonhardt, Alessandra, 1990-

L553f

FinFET prototype fabrication using alternative methods / Alessandra Leonhardt. – Campinas, SP: [s.n.], 2016.

Orientador: Leandro Tiago Manera. Coorientador: José Alexandre Diniz.

Dissertação (mestrado) – Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Transistores de efeito de campo. 2. Feixes de íons focalizados. 3. Microeletrônica. I. Manera, Leandro Tiago,1977-. II. Diniz, José Alexandre,1964-. III. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. IV. Título.

#### Informações para Biblioteca Digital

**Título em outro idioma:** Fabricação de protótipos de FinFETs usando métodos alternativos **Palavras-chave em inglês:**

Field effect transistors

Focused ion beam

Microelectronics

Área de concentração: Eletrônica, Microeletrônica e Optoeletrônica

Titulação: Mestra em Engenharia Elétrica

Banca examinadora:

Leandro Tiago Manera [Orientador] Stefan Jozef Emma Alfons De Gendt

Jacobus Willibrordus Swart **Data de defesa:** 12-07-2016

Programa de Pós-Graduação: Engenharia Elétrica

## COMISSÃO JULGADORA - DISSERTAÇÃO DE MESTRADO

Candidata: Alessandra Leonhardt RA: 162634

Data da Defesa: 12 de Julho de 2016

**Título da Tese:** FinFET Prototype Fabrication Using Alternative Methods (Fabricação de Protótipos de FinFETs Usando Métodos Alternativos)

Prof. Dr. Leandro Tiago Manera (FEEC/UNICAMP)

Prof. Dr. Stefan Jozef Emma Alfons De Gendt (IMEC and KU Leuven)

Prof. Dr. Jacobus Willibrordus Swart (FEEC/UNICAMP)

A ata de defesa, com as respectivas assinaturas dos membros da Comissão Julgadora, encontra-se no processo de vida acadêmica do aluno.

# Agradecimentos

Em primeiro lugar, gostaria de agradecer ao meu orientador, Leandro Tiago Manera, pelo apoio e confiança. Cuja motivação e entusiasmo foram essenciais no curso da pesquisa. Agradeço ao meu co-orientador, José Alexandre Diniz, pelas discussões muito prolíficas que ajudaram a dar forma a esse trabalho.

Agradeço ao CNPq pelo apoio financeiro e pelas políticas de incentivo à pesquisa, ao desenvolvimento e à inovação do governo brasileiro, que ainda não sendo ideais, já nos permitem mais do que haveria, se fosse de outra forma.

Aos grandes amigos e excelentes pesquisadores Lucas Petersen Barbosa Lima e Marcos Puyidinger dos Santos, que me ensinaram boa parte do que sei hoje e que me apoiaram sempre, e que acima de tudo me cobram sempre um trabalho sério. Que me ajudaram a sonhar mais alto e a buscar mais longe.

Agradeço aos meus amigos Jeckson Souza, Arthur Rauter, Gennaro Rodrigues, Luis Henrique Reinicke e Marcelo Brandalero, que tinham sempre uma piada guardada para os dias escuros e cuja amizade é muito valiosa.

Aos funcionários e colegas do CCSNano e do LPD/IFGW que me ajudaram em muitos momentos e me desafiaram a ser uma pessoa melhor em outros.

À minha esposa, Flávia Filippin, que foi sempre o mais importante suporte e incentivo em todos os momentos. Que é a motivação de todo o trabalho, de todo o esforço e empenho, e a razão de buscar ser sempre melhor do que se é.

Agradeço aos meus pais e irmãs, que possibilitaram minha caminhada, que torceram a cada conquista e que estenderam a mão a cada tropeço.

# **Abstract**

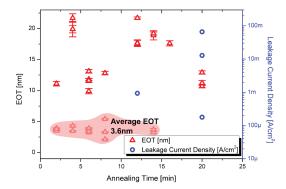

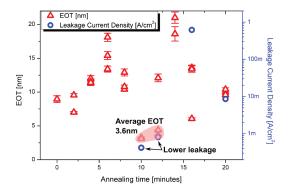

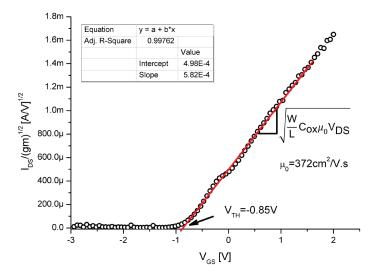

This work explores alternative methods for FinFET prototype fabrication. Different fin definition methods (Al hard mask FIB milling and Ga<sup>+</sup> FIB lithography) are explored, aiming for flexibility in defining the number of fins, as well as fin height. Alternative gate stacks are applied in the fabricated FinFETs, with two different dielectric materials (SiON and TiAlON) and two different methods for TiN gate electrode formation. The detailed fabrication process is provided and discussed, with special attention to difficulties and challenges faced. Fabrication steps are carefully evaluated, presenting details and parameters such as that the process could be replicated. Morphological and electrical characterizations are performed on the fabricated FinFETs. With the Ga<sup>+</sup> FIB lithography method, working FinFETs with nine parallel fins are fabricated, with fin width down to 87nm. Electrical parameters are extracted, such as V<sub>TH</sub>, subthreshold slope, leakage current, low field mobility, R<sub>SD</sub>, gate electrode work function, EOT, and others. Working FinFETs with sub-100nm fin width are presented, with subthreshold slope of 120mV/dec and low field mobility of 372cm<sup>2</sup>/v.s, results that show an improvement on previous works, but still leave room for optimizations. Discussions are performed, explaining the meaning of the extracted parameters, and ways to improve the results. The different gate stacks are evaluated regarding their parameter stability and leakage current density. An EOT of 3.6nm is achieved for the SiON dielectric, with leakage current density between 177µA/cm<sup>2</sup> and 0.61mA/cm<sup>2</sup>. Important developments have been made towards process integration and novel prototype fabrication methods. Future works include silicon-dielectric interface improvements and a self-aligned process to achieve increased transconductance and gate-to-channel coupling, and reduce the series resistance.

**Keywords**: FinFET; MOSFET; Nanotechnology; Prototype Fabrication; Focused Ion Beam; Metal Gate.

# Resumo

Este trabalho explora métodos alternativos para fabricação de protótipos de FinFETs. Diferentes métodos de definição de fin (fresagem de máscara de Al por feixe de íon focalizado e litografia por feixe focalizado de íons de gálio) são explorados, buscando flexibilidade na definição do número de fins, bem como a altura dos fins. Diferentes estruturas de porta são aplicados nos FinFETs fabricados, com dois materiais dielétricos diferentes (SiON e TiAlON) e dois métodos diferentes para a formação de TiN como eletrodo de porta. O processo de fabricação detalhado é fornecida e discutido, com especial atenção às dificuldades e desafios enfrentados. Etapas de fabricação são cuidadosamente avaliadas, apresentando detalhes e parâmetros de forma que o processo possa ser replicado. Caracterizações morfológicas e elétricas são realizadas nos FinFETs fabricadas. Com a litografia por feixe focalizado de íons de gálio, FinFETs com nove fins em paralelo são fabricados, com largura de fin até 87nm e comportamento elétrico de transistor. Parâmetros elétricos são extraídos, tais como V<sub>TH</sub>, inclinação de sublimiar, corrente de fuga, mobilidade de portadores, R<sub>SD</sub>, função trabalho do eletrodo de porta, EOT, e outros. FinFETs com largura fin abaixo de 100nm são apresentados, com inclinação de sublimiar de 120 mV/dec e moblidade de portadores de 372 cm<sup>2</sup>/V.s, resultados que mostram uma melhoria em relação a trabalhos anteriores, mas ainda deixam espaço para otimizações. Discussões são realizadas, explicando o significado dos parâmetros extraídos, e formas de melhorar os resultados. As diferentes estruturas de porta são avaliados quanto à estabilidade dos parâmetros e densidade de corrente de fuga. Um EOT de 3.6nm é alcançado para o dieléctrico SiON, com densidade de corrente de fuga entre 177µA/cm<sup>2</sup> e 0.61mA/cm<sup>2</sup>. Desenvolvimentos importantes são feitos no sentido da integração de processos e inovações em termos de métodos de fabricação de protótipos. Trabalhos futuros incluem melhorias na interface de silício-dielétrico e um processo de fabricação auto alinhado para alcançar uma maior transcondutância e acoplamento entre porta e canal, e reduzir a resistência série.

Palavras-chaves: FinFET; MOSFET; Nanotecnologia; Fabricação de Protótipos; Feixe de Íons Focalizado; Eletrodo Metálico de Porta.

# List of Figures

| Figure 1 –  | Evolution of different aspects of Intel integrated circuit fabrication.  From (IC INSIGHTS, 2015)                    | 19 |

|-------------|----------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 –  | Three dimensional schematic of a planar bulk MOSFET and a SOI                                                        | 10 |

|             | FinFET                                                                                                               | 19 |

| Figure 3 –  | Illustration of the operation of the MOS transistor in the subthreshold                                              |    |

|             | region (a), linear region (b) and saturation region (c)                                                              | 20 |

| Figure 4 -  | MOSFET typical electrical response presented using FinFETs with                                                      |    |

|             | 1μm gate length and 10nm fin width                                                                                   | 21 |

| Figure 5 -  | Simplified schematic of the FinFET fabrication flow, presenting the fin                                              |    |

|             | patterning (a), gate stack formation (b), source and drain implant (c)                                               |    |

|             | and interconnect deposition (d) $\hdots$                                                                             | 22 |

| Figure 6 –  | Schematic organization of the work and how this thesis will present it.                                              | 26 |

| Figure 7 –  | Schematic process for fin definition through spacer lithography                                                      | 30 |

| Figure 8 -  | Schematic process for FIB fin milling                                                                                | 31 |

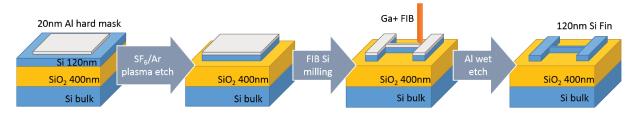

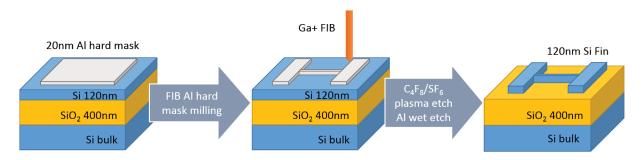

| Figure 9 –  | Schematic process for FIB Aluminium hard mask milling                                                                | 32 |

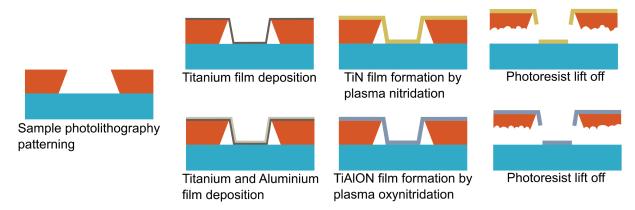

| Figure 10 – | Schematic process for Ga <sup>+</sup> FIB lithography                                                                | 33 |

| Figure 11 – | Schematic of the magnetron sputtering system                                                                         | 36 |

| Figure 12 – | Schematic of TiN and TiAlON thin film formation by PVD deposition                                                    |    |

|             | and plasma surface treatment                                                                                         | 38 |

| Figure 13 – | ECR plasma system used, with its parts indicated                                                                     | 39 |

| Figure 14 – | Gate stack materials evolution throughout the years and technology                                                   |    |

|             | nodes. A brief example of gate stack structure for future technology                                                 |    |

|             | nodes is also outlined                                                                                               | 40 |

| Figure 15 – | Alternative gate stacks used in this thesis                                                                          | 42 |

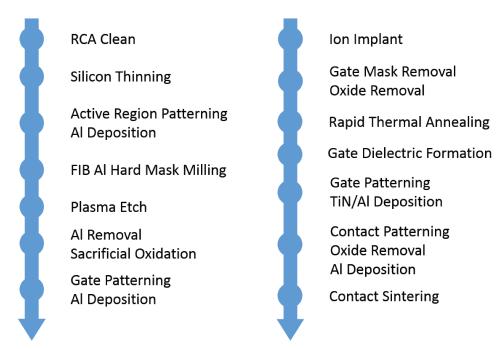

| _           | Summarized process steps for FinFET fabrication                                                                      | 43 |

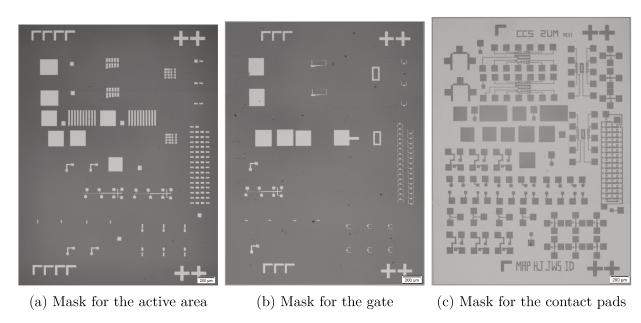

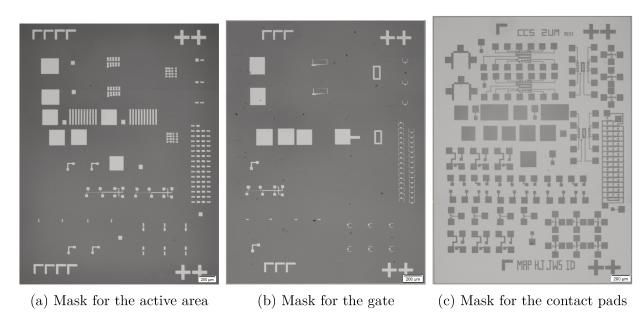

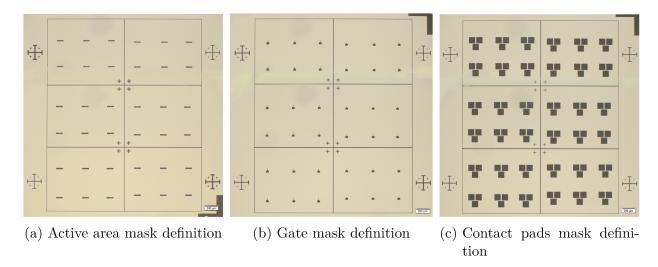

| Figure 17 – | Set of photomasks used for the FinFET fabrication                                                                    | 44 |

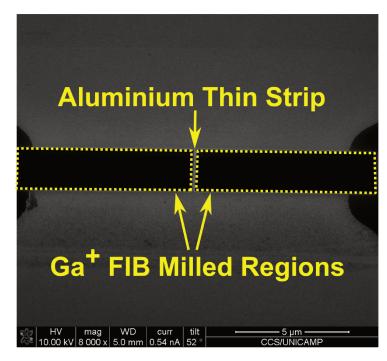

| Figure 18 – | Resulting etch mask after the milling                                                                                | 46 |

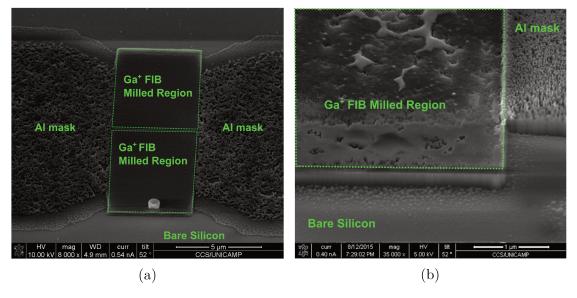

| Figure 19 – | a) Active region after $SF_6/Ar$ plasma etch. b) Active region after                                                 |    |

|             | C <sub>4</sub> F <sub>8</sub> /SF <sub>6</sub> plasma etch. In both cases the etch in the Ga <sup>+</sup> FIB milled |    |

|             | regions is different than on the bare silicon, as evidenced by the step                                              |    |

|             | on the edge                                                                                                          | 46 |

| Figure 20 – | EDS spectrum of the fin region, showing strong gallium incorporation                                                 |    |

|             | on the edge of the milled region and on the fin                                                                      | 47 |

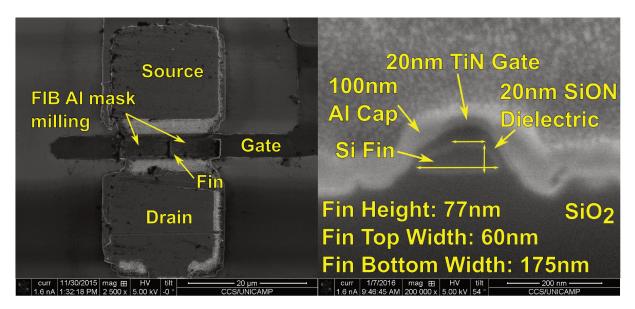

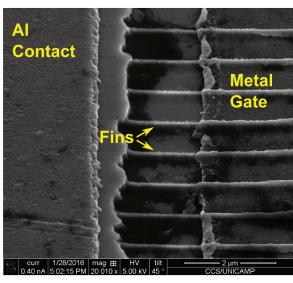

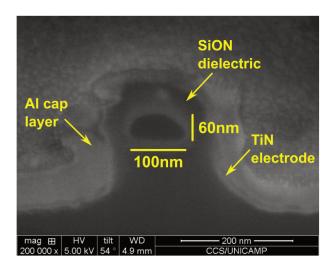

| Figure 21 – | Fabricated FinFET device, along with fin cross section presenting metal                                              |    |

|             | gate coverage of the fin                                                                                             | 48 |

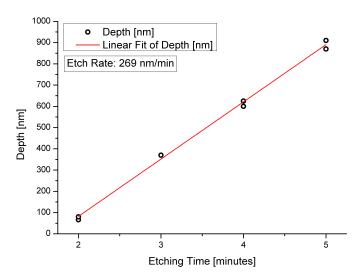

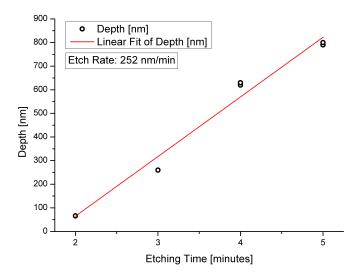

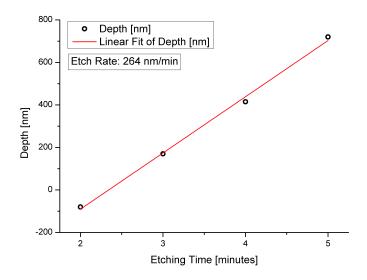

| Figure 22 – | Etching depth achieved in RIE with different etching times for crystalline control sample.                                                                                                                        | 49       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

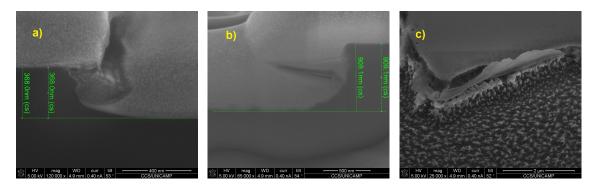

| Figure 23 – | Etching depth was measured from the step between the aluminium covered and bare silicon regions. Sidewall profile after 3 minutes of RIE (a) and 5 minutes of RIE (b). Silicon roughness after 5 minutes of RIE   |          |

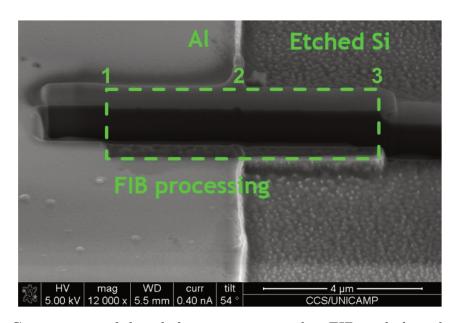

| Figure 24 – | (c)                                                                                                                                                                                                               | 50<br>50 |

| Figure 25 – | Cross section of the whole region processed in FIB, including the aluminium stripe and bare silicon region.                                                                                                       | 51       |

| Figure 26 – | Height difference between the FIB milled region and the bare silicon for the RIE with different etching times.                                                                                                    | 52       |

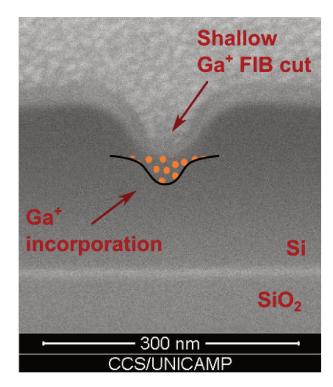

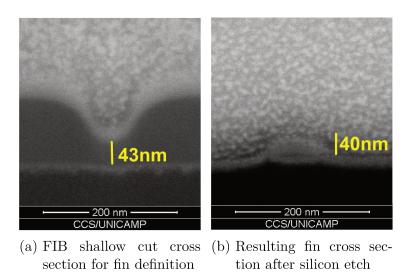

| Figure 27 – | Cross section presenting a shallow cut made with the Ga <sup>+</sup> FIB and indicating schematically the Ga <sup>+</sup> incorporation in the silicon layer                                                      | 53       |

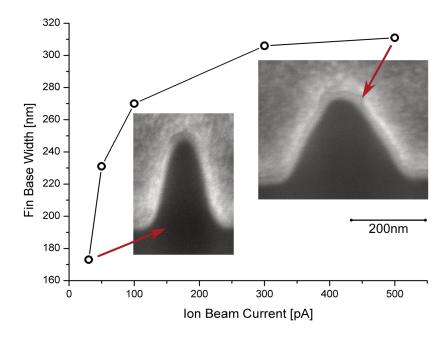

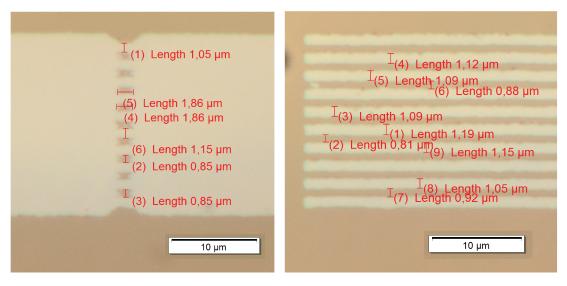

| Figure 28 – | Evaluation of fin width using different ion beam currents for the fin definition                                                                                                                                  | 54       |

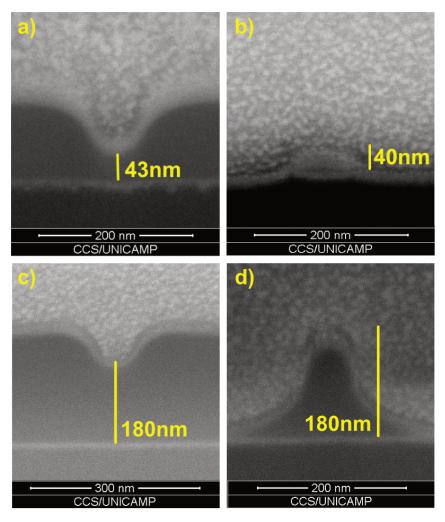

| Figure 29 – | Cross sections of FIB shallow cut for Ga incorporation (a)(c) and resulting fin after SF6/Ar plasma etch (b)(d), presenting the dependence between the fin height and remaining silicon layer beneath the shallow |          |

| _           | cut                                                                                                                                                                                                               | 55       |

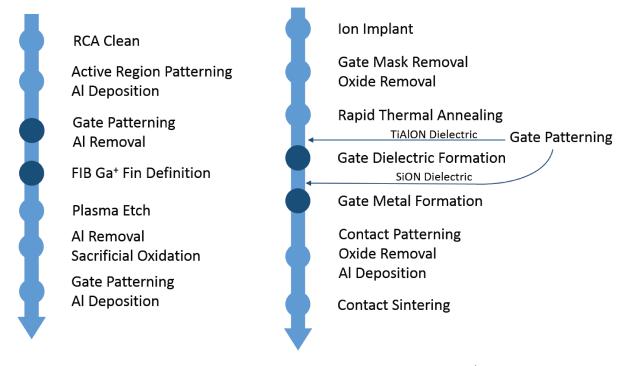

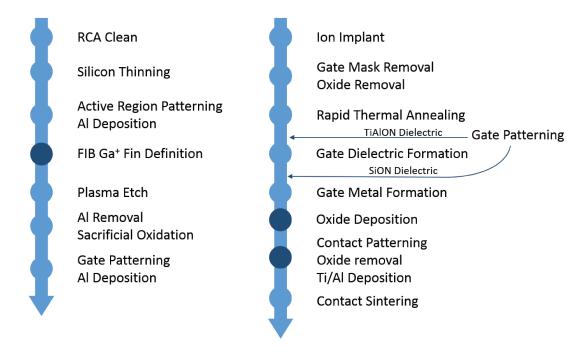

| _           | Process flow for the FinFET fabricated with Ga <sup>+</sup> Fin Definition                                                                                                                                        | 56       |

| _           | Set of photomasks used for the FinFET fabrication                                                                                                                                                                 | 57       |

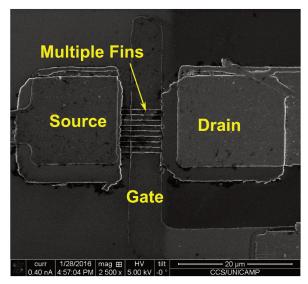

|             | Multiple fin FinFET prototype                                                                                                                                                                                     | 60       |

| Figure 33 – | Schematic of lithographic process to obtain negative angled walls using a dark field mask                                                                                                                         | 61       |

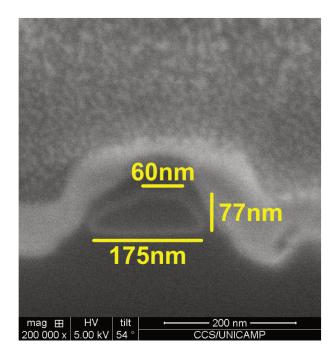

| Figure 34 – | Minimum obtained dimensions                                                                                                                                                                                       | 61       |

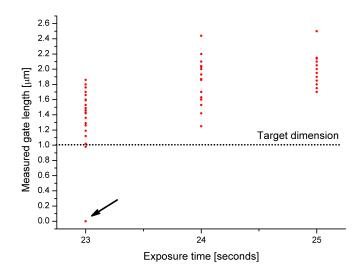

| Figure 35 – | Minimum obtained dimensions for the gate as a function of exposure time                                                                                                                                           | 63       |

| Figure 36 – | Set of photomasks used for the FinFET fabrication                                                                                                                                                                 | 64       |

| _           | Process flow for the FinFET fabricated with Ga <sup>+</sup> Fin Definition and the FinFET Mask                                                                                                                    | 65       |

| Figure 38 – | Sample before and after silicon etch, showing the close relation between<br>the silicon layer thickness beneath the FIB cut and resulting fin height                                                              | 65       |

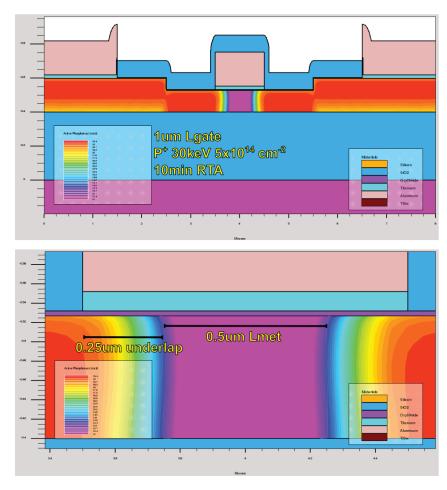

| Figure 39 – | SILVACO simulation of the complete device, presenting the doping pro-<br>file after 10 minutes thermal treatments                                                                                                 | 66       |

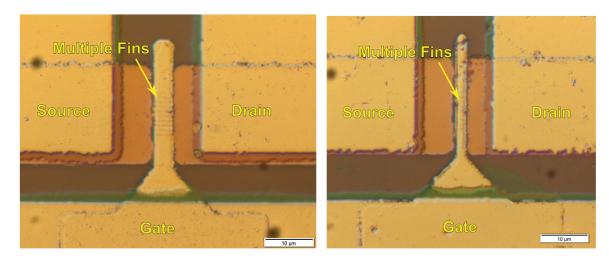

| Figure 40 – | Fabricated devices                                                                                                                                                                                                | 67       |

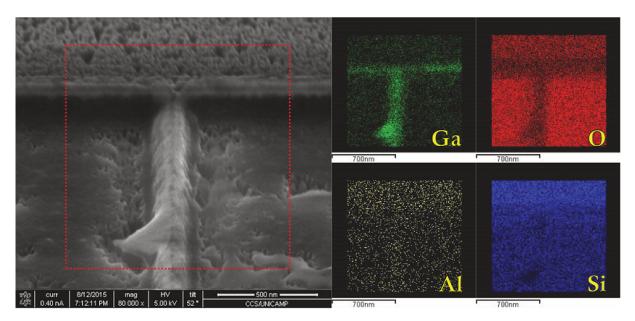

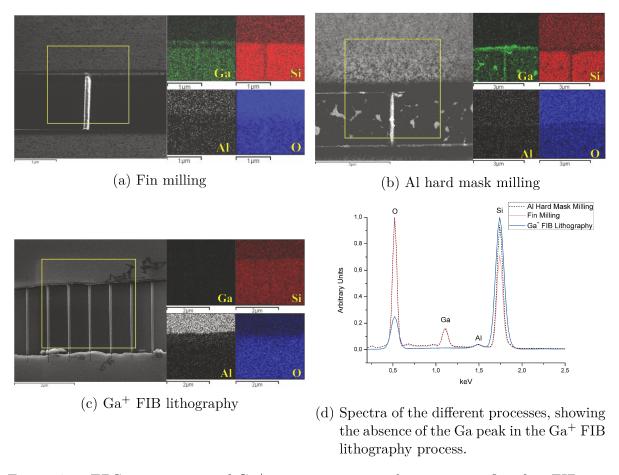

| 0           | EDS comparisons of Ga <sup>+</sup> incorporation in the transistor fin after FIB processing and plasma etching, for the different fin definition processes.                                                       | 69       |

|             |                                                                                                                                                                                                                   |          |

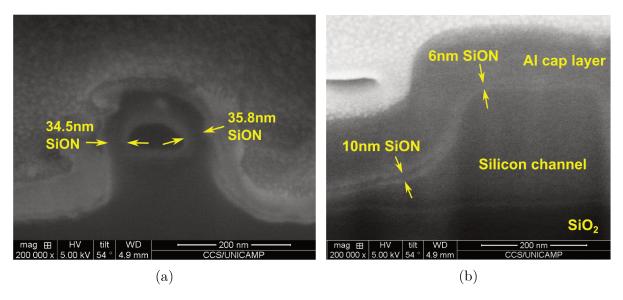

| Figure 42 – | Difference in SiON layer thickness grown in a FIB milled fin (a) and in           |    |

|-------------|-----------------------------------------------------------------------------------|----|

|             | a fin defined using $Ga^+$ FIB lithography                                        | 70 |

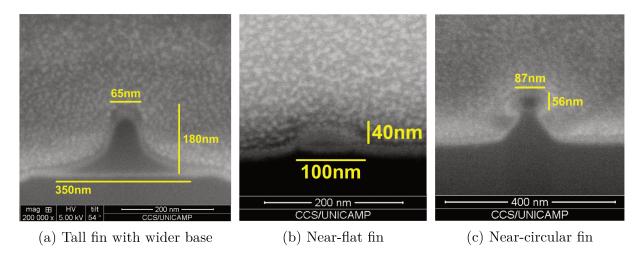

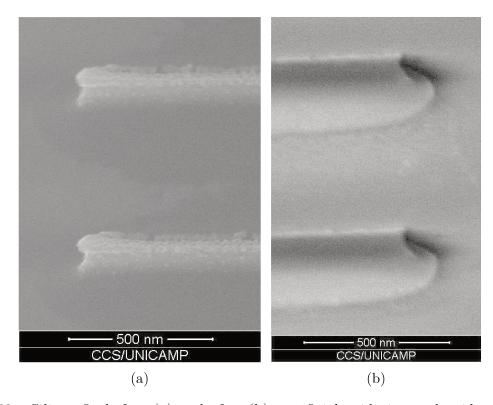

| Figure 43 – | Fin obtained using FIB silicon milling method                                     | 71 |

| Figure 44 – | Fin obtained using Al hard mask FIB milling method                                | 72 |

| Figure 45 – | Different fins obtained using $\mathrm{Ga^{+}}$ FIB lithography definition method | 73 |

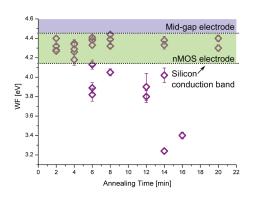

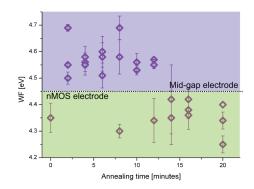

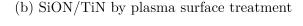

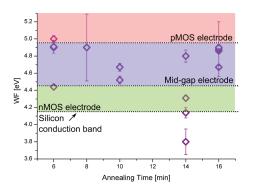

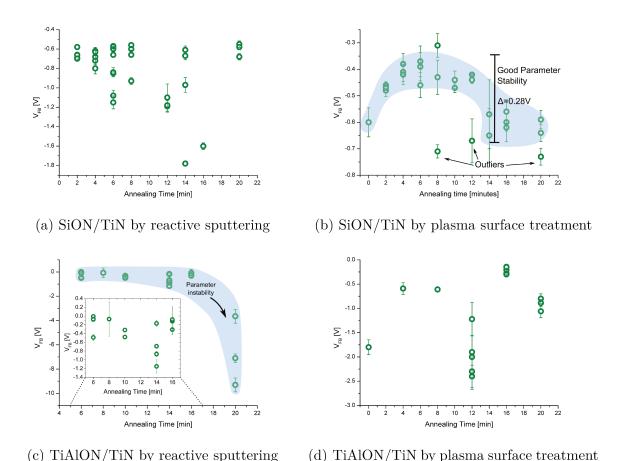

| Figure 46 – | Work function variation with 450°C annealing time for the different               |    |

|             | gate stack structures. The values are indicated whether they are more             |    |

|             | suitable for pMOS, nMOS or mid-gap electrodes                                     | 74 |

| Figure 47 – | Flat band voltage variation with 450°C annealing time extracted from              |    |

|             | capacitance-voltage measurements for the different gate stack struc-              |    |

|             | tures. Cases b and c present remarkable parameter stability or instability.       | 76 |

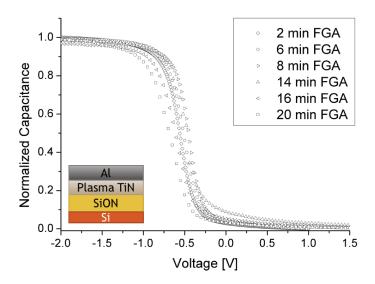

| Figure 48 – | C-V characteristics of SiON/TiN by plasma surface treatment gate                  |    |

|             | stack with different annealing times                                              | 77 |

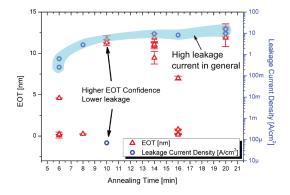

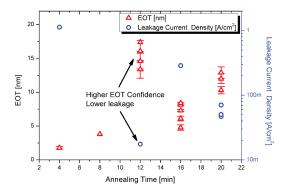

| Figure 49 – | Comparison between EOT and leakage current density between                        |    |

|             | TiAlON and SiON gate stack alternatives                                           | 78 |

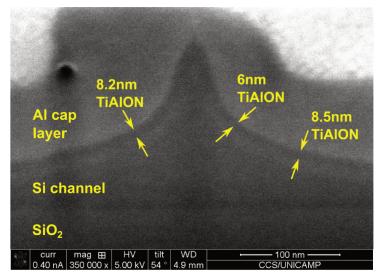

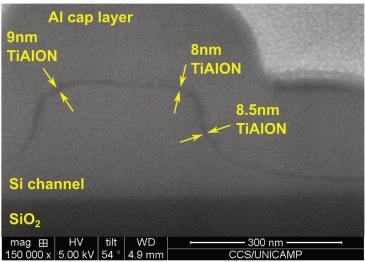

| Figure 50 – | Silicon fin with TiAlON dielectric completely covering it for two differ-         |    |

|             | ent TiN formation methods. Physical thickness of TiAlON estimated                 |    |

|             | around 8nm. Charging issues prevent observing the TiN layer in these              |    |

|             | SEM images                                                                        | 80 |

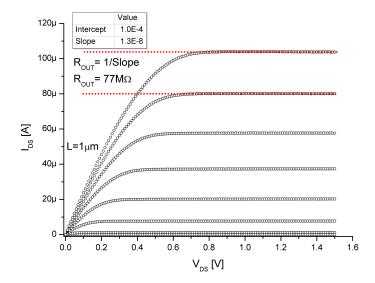

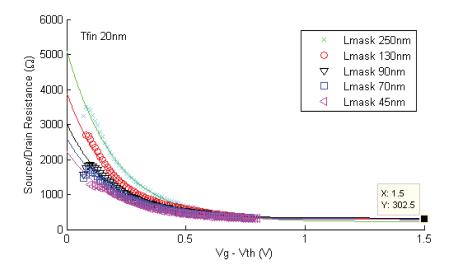

| Figure 51 – | $I_{DS}xV_{DS}$ of Al hard mask milled FinFET                                     | 82 |

| Figure 52 – | $R_{SD}$ of Al hard mask milled FinFET                                            | 82 |

| Figure 53 – | $I_{DS}xV_{GS}$ of Al hard mask milled FinFET                                     | 83 |

| Figure 54 – | $I_{DS}/\sqrt{gm}$ versus $V_{GS}$ showing the extraction procedure for the Y-    |    |

|             | Function method                                                                   | 83 |

| Figure 55 – | $I_{DS}/\sqrt{gm}$ versus $V_{GS}$ showing the extraction procedure for the Y-    |    |

|             | Function method for a different measurement, from the same FinFET                 |    |

|             | run                                                                               | 85 |

|             | Subthreshold characteristics of Al hard mask milled FinFET                        | 85 |

| Figure 57 – | $I_{DS}xV_{DS}$ of FinFET with TiAlON/TiN by reactive sputtering gate stack       | 87 |

| Figure 58 – | $I_{DS}xV_{GS}$ of above-threshold (a) and subthreshold (b) characteristics of    |    |

|             | FinFET with TiAlON/TiN by reactive sputtering gate stack                          | 87 |

| Figure 59 – | $I_{DS}/\sqrt{gm}$ versus $V_{GS}$ showing the extraction procedure for the Y-    |    |

|             | Function method                                                                   | 88 |

| Figure 60 – | Transistor $I_{DS}xV_{GS}$ characteristics at low $V_{DS}$ with and without the   |    |

|             | series resistance effect, showing how the extraction of $V_{th}$ is dependant     |    |

| _           | on this parameter. From (TAUR, 2000)                                              | 89 |

| Figure 61 – | $I_{DS}XV_{DS}$ of FinFET with SiON/TiN by plasma surface treatment gate          |    |

|             | stack                                                                             | 89 |

| Figure 62 – | $I_{DS}xV_{GS}$ of above-threshold (a) and subthreshold (b) characteristics of         |     |

|-------------|----------------------------------------------------------------------------------------|-----|

|             | FinFET with SiON/TiN by plasma surface treatment gate stack                            | 90  |

| Figure 63 – | Silicon fin before (a) and after (b) sacrificial oxidation and oxide strip-            |     |

|             | ping, showing how the sidewall roughness greatly reduces                               | 91  |

| Figure 64 – | Schematic of the procedure to extract the output resistance                            | 118 |

| Figure 65 – | Schematic of the procedure to extract the subthreshold slope                           | 119 |

| Figure 66 – | Campbell et al. method with extrapolation of the curves to yield a                     |     |

|             | single value for the series resistance $R_{SD}$                                        | 120 |

| Figure 67 – | Extraction procedure for the $V_{\mathrm{th}}$ parameter by extrapolating the          |     |

|             | $I_{\rm DS}xV_{\rm GS}$ curve at the point of maximum transconductance                 | 121 |

| Figure 68 – | Transistor $I_{DS}xV_{GS}$ characteristics at low $V_{DS}$ with and without the        |     |

|             | series resistance effect, showing how $V_{\rm th}$ changes when removing its           |     |

|             | effect. From (TAUR, 2000)                                                              | 121 |

| Figure 69 – | $I_{\rm DS}/\sqrt{gm}$ versus $V_{\rm GS}$ showing the extraction procedure for the Y- |     |

|             | Function method                                                                        | 122 |

# List of Tables

| Table 1 –  | Complete RCA wafer clean process                                      | 44 |

|------------|-----------------------------------------------------------------------|----|

| Table 2 -  | Wet oxidation process                                                 | 45 |

| Table 3 –  | Photo-lithography process                                             | 45 |

| Table 4 -  | FIB parameters for Al hard mask milling                               | 45 |

| Table 5 -  | Final fin definition parameters                                       | 56 |

| Table 6 –  | Fin<br>FET gate stacks for metal electrode and dielectric comparisons | 58 |

| Table 7 –  | Parameters for the active region mask lithography                     | 62 |

| Table 8 -  | Parameters for the gate mask lithography                              | 63 |

| Table 9 –  | Extracted EOT for the different gate stacks                           | 77 |

| Table 10 – | Parameter comparisons of gate stack alternatives                      | 93 |

| Table 11 – | Parameters of the different FinFETs presented in this work            | 94 |

| Table 12 – | Parameter comparison between FinFETs fabricated in Brazilian research |    |

|            | institutes                                                            | 94 |

# List of Acronyms and Symbols

$\mu_0$  low field mobility.

**ALD** atomic layer deposition.

CMOS complementary metal oxide semiconductor.

**CMP** chemical mechanical polishing.

CVD chemical vapour deposition.

**DI** deionized.

**DIBL** drain induced barrier lowering.

e-beam electron beam.

EBL electron beam lithography.

**ECR** electron cyclotron resonance.

**EDS** energy dispersive X-ray spectroscopy.

**EOT** equivalent oxide thickness.

**EUVL** extreme ultraviolet lithography.

FIB focused ion beam.

FinFET fin field effect transistor.

**HF** hydrofluoric acid.

IC integrated circuit.

ICP inductively coupled plasma.

$L_{met}$  metallurgical channel length.

LDD lightly doped drain/source.

MEMS micro electro-mechanical systems.

MIF metal ion free.

MOSFET metal oxide semiconductor field effect transistor.

$\mathbf{R}_{\mathbf{OUT}}$  output resistance.

$\mathbf{R_{SD}}$  source and drain series resistance.

**RIE** reactive ion etch.

RTA rapid thermal annealing.

**SEM** scanning electron microscope.

**SIMS** secondary ion mass spectrometry.

SiON silicon oxynitride.

**SOI** silicon-on-insulator.

**STI** shallow trench isolation.

${f TEM}$  transmission electron microscope.

TiAlON titanium-aluminium oxynitride.

$\mathbf{V_{FB}}$  flat band voltage.

$\mathbf{V_{th}}$  threshold voltage.

VLSI very large system integration.

$\mathbf{W_{fin}}$  fin width.

WF work function.

# Contents

| 1 | Intr | oductio  | on                                                                          | LÇ |

|---|------|----------|-----------------------------------------------------------------------------|----|

|   | 1.1  | Plana    | and 3D MOSFETs                                                              | 18 |

|   | 1.2  | Transi   | stor Operation                                                              | 19 |

|   | 1.3  | FinFE    | T Fabrication Overview and Related Challenges                               | 22 |

|   | 1.4  | Object   | tives and Motivation                                                        | 24 |

|   | 1.5  | Thesis   | Structure                                                                   | 26 |

| 2 | Finf | ET Fa    | brication Processes                                                         | 28 |

|   | 2.1  | Fin D    | efinition Methods                                                           | 28 |

|   |      | 2.1.1    | Electron Beam Lithography                                                   | 28 |

|   |      | 2.1.2    | 193nm Immersion Lithography                                                 | 26 |

|   |      | 2.1.3    | Spacer Lithography                                                          | 26 |

|   |      | 2.1.4    | Focused Ion Beam Techniques                                                 | 3( |

|   |      |          | 2.1.4.1 FIB Fin Milling                                                     | 31 |

|   |      |          | 2.1.4.2 Al Hard Mask FIB Milling                                            |    |

|   |      |          | 2.1.4.3 Ga <sup>+</sup> FIB Lithography                                     |    |

|   | 2.2  | Thin 1   | Film Deposition                                                             |    |

|   |      | 2.2.1    | Atomic Layer Deposition                                                     |    |

|   |      | 2.2.2    | Metal Evaporation                                                           |    |

|   |      | 2.2.3    | Sputter Deposition                                                          |    |

|   |      | 2.2.4    | Plasma Surface Treatment                                                    |    |

|   | 2.3  | Gate S   | Stack                                                                       |    |

|   |      | 2.3.1    | Industry Gate Stack Evolution                                               |    |

|   |      | 2.3.2    | Alternative Gate Stacks for FinFET prototypes                               |    |

| 3 | _    |          | tal Procedure                                                               |    |

|   | 3.1  |          | nium Hard Mask Milled FinFETs                                               |    |

|   | 3.2  |          | ve Ion Etch Calibration                                                     | 48 |

|   |      | 3.2.1    | Initial Determination of the Ga <sup>+</sup> Focused Ion Beam Effect in the |    |

|   |      |          | Etching Rate                                                                |    |

|   |      |          | 3.2.1.1 Control Sample                                                      |    |

|   |      |          | 3.2.1.2 Amorphous Silicon Sample                                            |    |

|   |      |          | 3.2.1.3 FIB Processed Sample                                                |    |

|   |      | 3.2.2    | Ga <sup>+</sup> Masking for Multiple Fin Fabrication                        |    |

|   | 3.3  |          |                                                                             | 56 |

|   | 3.4  |          | graphy Calibration                                                          |    |

|   | 3.5  | -        | ized Ga <sup>+</sup> Focused Ion Beam Lithography FinFETs                   |    |

| 4 | Cha  | racteriz | zations and Discussions                                                     | 36 |

|    | 4.1    | FinFE   | T Morphological Characterisations               |

|----|--------|---------|-------------------------------------------------|

|    |        | 4.1.1   | Ga <sup>+</sup> incorporation in the fin        |

|    |        | 4.1.2   | Fin Dimensions                                  |

|    | 4.2    | Gate S  | Stack Alternatives Comparisons                  |

|    | 4.3    | FinFE   | T Electrical Characterisations                  |

|    |        | 4.3.1   | Al hard mask FIB milling                        |

|    |        | 4.3.2   | Ga <sup>+</sup> FIB Lithography                 |

|    |        |         | 4.3.2.1 TiAlON/TiN by reactive sputtering       |

|    |        |         | 4.3.2.2 SiON/TiN by plasma surface treatment 88 |

| 5  | Con    | clusion | s and Future Work                               |

|    | 5.1    | List of | Publications                                    |

| Bi | bliogi | raphy   |                                                 |

| ΑF | PEN    | IDIX    | A Parameter Extractions                         |

|    | A.1    | Outpu   | t Resistance                                    |

|    | A.2    | Subth   | reshold Slope                                   |

|    | A.3    | Series  | Resistance                                      |

|    | A.4    | Thresl  | nold Voltage and Low Field Mobility             |

# 1 Introduction

#### 1.1 Planar and 3D MOSFETs

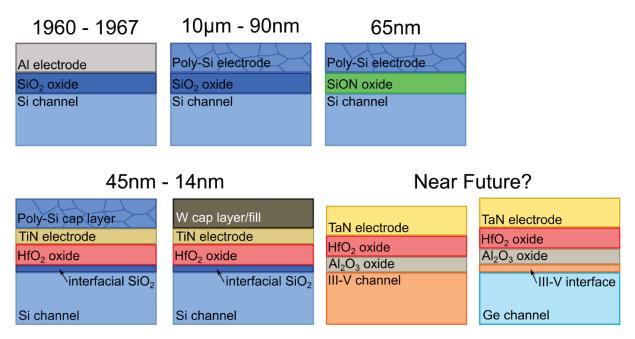

The metal oxide semiconductor field effect transistor (MOSFET) can be considered one of the greatest inventions of the 20th century and has revolutionized the field of electronic devices and systems. For the last five decades the transistor has become steadily smaller, following the observation made by Gordon Moore (MOORE, 1965; GARGINI, 2015). However, it is a constant challenge for process engineers to reduce its dimensions, which ranges from incremental improvements and slight tricks to whole new materials and novel processes. Figure 1 presents the evolution of Intel technology from the 0.5µm technology node to the 14nm node, in regards to the several aspects that comprise the complete integrated circuit (IC) fabrication. It can be seen that to achieve modern transistors with gate lengths of few nanometres, steady efforts in all aspects had to be made. The transistor architecture change towards Tri-Gate, also known as fin field effect transistor (FinFET), has been commercially introduced in 2011, and current research is focused on further improvements still – such as replacing the silicon channel for a material with higher carrier mobility. It is important to note that although some developments are ground-breaking – such as the introduction of high- $\kappa$  dielectric and metal gate – they are not final. For the scaling to continue, new developments have to be introduced every node and new paradigms are researched, which could solve one problem or another (COLLAERT et al., 2015).

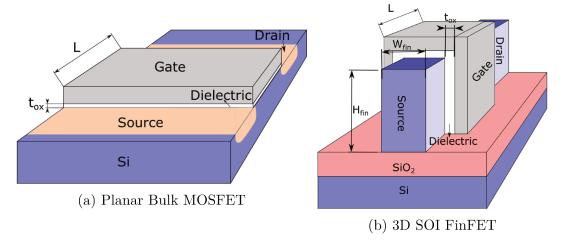

The main focus of this Master thesis are the transistor architecture, gate oxide and gate electrode aspects. Beyond 32nm, short channel effects degrade the electrical behaviour of planar MOSFETs, and a 3D channel becomes essential. It provides superior gate-to-channel coupling, lessening effects such as drain induced barrier lowering (DIBL) and enabling excellent device subthreshold characteristics (SUBRAMANIAN et al., 2006; COLINGE et al., 2008). The adopted solution was the FinFET (HUANG et al., 1999; HISAMOTO et al., 2000), a tri- or double-gate semiconductor device with self-aligned source and drain regions and gates aligned to each other, and planar complementary metal oxide semiconductor (CMOS)-compatible process flow. A schematic of a planar MOSFET, fabricated in bulk silicon, and of a 3D FinFET, fabricated on silicon-on-insulator (SOI) substrate, is presented in Figure 2<sup>1</sup>. One can see that a completely new direction related to transistor fabrication was taken when the 3D FinFET was first introduced. What was a mostly planar process – in the front end of the line, at least – now becomes three-dimensional, and has to solve issues related to this device three dimensionality – step

All figures whose source has not been mentioned are of own elaboration.

| <b>Evolution of Intel Technology</b> |        |                   |                   |                   |                   |                   |                   |                   |                   |                   |                   |

|--------------------------------------|--------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Process                              | P852   | P854              | P856              | P858              | PX60              | P1262             | P1264             | P1266             | P1268             | P1270             | P1272             |

| Year                                 | 1993   | 1995              | 1997              | 1999              | 2001              | 2003              | 2005              | 2007              | 2009              | 2011              | 2014              |

| Node                                 | 0.5μ   | $0.35\mu$         | 0.25μ             | $0.18\mu$         | $0.13\mu$         | 90nm              | 65nm              | 45nm              | 32nm              | 22nm              | 14nm              |

| Metal                                | Al     | $\longrightarrow$ | $\rightarrow$     | $\rightarrow$     | Cu                | $\longrightarrow$ | $\rightarrow$     | $\longrightarrow$ | $\longrightarrow$ | $\longrightarrow$ | $\longrightarrow$ |

| Interlevel<br>Dielectric             | SiO2   | $\rightarrow$     | $\rightarrow$     | SiOF              | $\rightarrow$     | CDO               | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | Air<br>Gap        |

| Transistor<br>Architecture           | Planar | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\longrightarrow$ | $\longrightarrow$ | Tri-Gate          | $\rightarrow$     |

| Gate Oxide                           | SiO2   | $\longrightarrow$ | $\longrightarrow$ | $\rightarrow$     | $\longrightarrow$ | $\longrightarrow$ | SiON              | High-K            | $\longrightarrow$ | $\longrightarrow$ | $\longrightarrow$ |

| Gate<br>Electrode                    | Poly   | $\longrightarrow$ | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | Metal             | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     |

| Channel                              | Si     | $\longrightarrow$ | $\longrightarrow$ | $\rightarrow$     | $\longrightarrow$ | Strained<br>Si    | $\rightarrow$     | $\longrightarrow$ | $\longrightarrow$ | $\longrightarrow$ | $\rightarrow$     |

| Lithography                          | 365nm  | 248nm             | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | 193nm             | $\longrightarrow$ | Double<br>Pattern | i193nm            | $\longrightarrow$ | $\rightarrow$     |

| Wafer Size                           | 200mm  | $\longrightarrow$ | $\rightarrow$     | $\longrightarrow$ | 200mm/<br>300mm   | 300mm             | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     | $\rightarrow$     |

Source: Intel, IC Insights

Figure 1 – Evolution of different aspects of Intel integrated circuit fabrication. From (IC INSIGHTS, 2015).

coverage during material deposition and careful sidewall etching, to name a couple.

Figure 2 – Three dimensional schematic of a planar bulk MOSFET and a SOI FinFET.

# 1.2 Transistor Operation

The main principle of MOSFET operation is to apply a bias on the gate electrode that creates an inversion layer on the semiconductor substrate, where a source to drain current flows. In this section the transistor physical and electrical operation will be briefly explained in the context of the works presented in Grove (1967), Tsividis (2003) and Sze and Ng (2006).

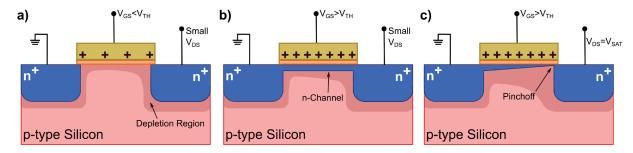

When varying the gate bias, two regions are clearly discernible: the subthreshold region (Figure 3a), where the channel is still beginning to form, and the inversion region (Figure 3b), where the channel is fully formed and the transistor is conducting.

If the gate bias is set to a value above the threshold voltage, varying the drain voltage takes the transistor from the linear region (Figure 3b), where an increase in  $V_{DS}$  results in a linear increase in  $I_{DS}$ , to the saturation region (Figure 3c), where the channel is pinched off and the current is constant for further increases in  $V_{DS}$ .

Figure 3 – Illustration of the operation of the MOS transistor in the subthreshold region (a), linear region (b) and saturation region (c).

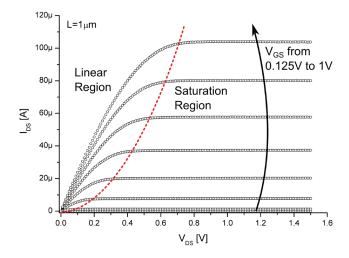

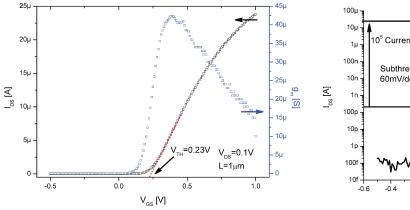

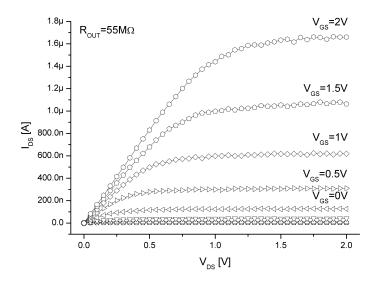

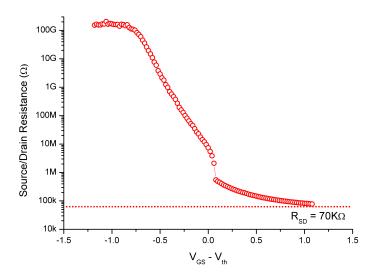

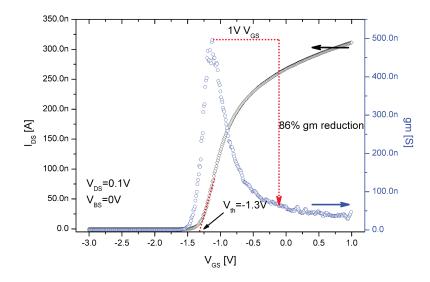

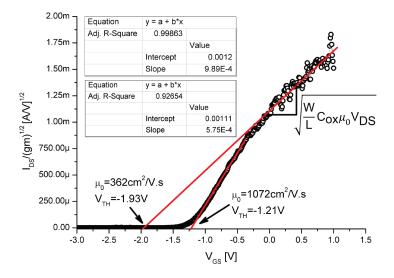

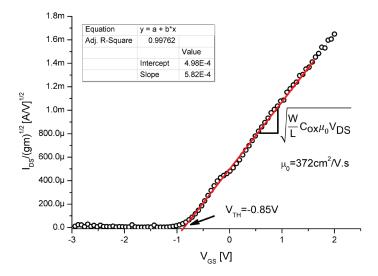

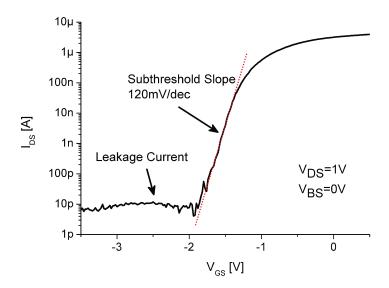

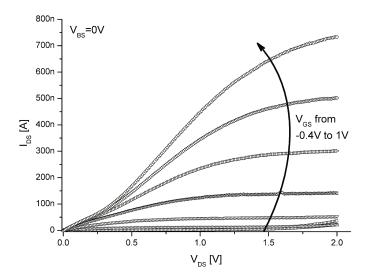

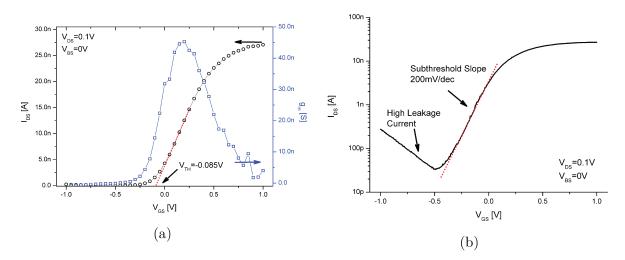

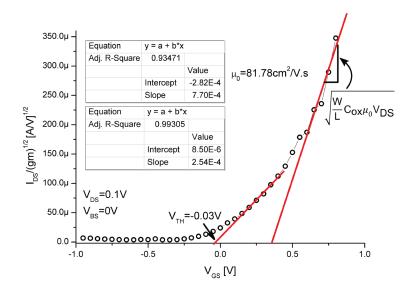

The physical operation translates in current response for a given condition of source, drain and gate bias. In Figure 4 the typical transistor behaviour is presented through the characteristic  $I_{DS}$  measurements of FinFET fabricated at IMEC with gate length of 1 $\mu$ m and 10nm fin width (FERREIRA, 2012; LEONHARDT, 2014). Throughout this work similar curves – for the FinFETs fabricated and measured in this thesis – will be presented and analysed.

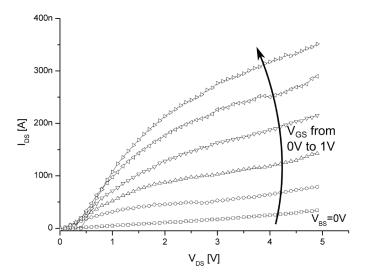

Figure 4a shows the  $I_{DS}xV_{DS}$  curve of the MOS transistor. For a given  $V_{GS}$ , increasing  $V_{DS}$  takes the transistor from the linear region, where the drain current increases linearly with  $V_{DS}$ , to the saturation region, where  $I_{DS}$  is ideally constant. On the onset of saturation,  $V_{DS}$  is equal to  $V_{GS}$  minus  $V_{TH}$ . Increasing the gate bias value takes the transistor back to the linear region, what gives rise to the quadratic curve that divides the linear and saturation regions.

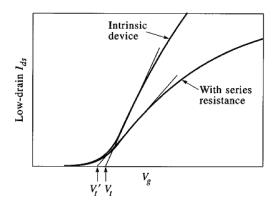

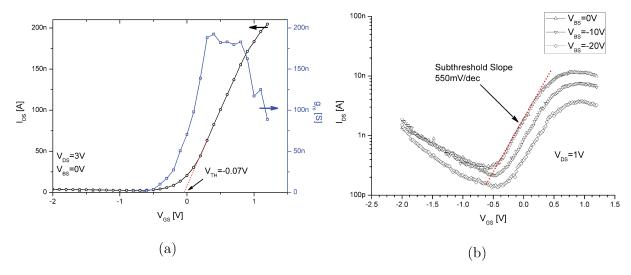

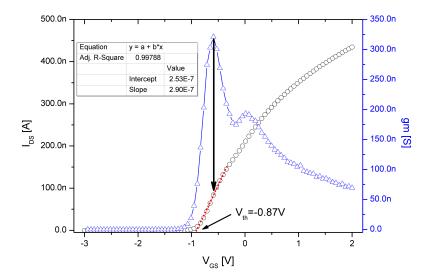

The current response with the variation of  $V_{GS}$  is analysed in Figure 4b and Figure 4c, for a small  $V_{DS}$ , showing the above threshold and subthreshold characteristics, respectively. When increasing  $V_{GS}$ , the transistor passes from an off state, with small current, to an on state, where  $I_{DS}$  increases almost linearly with every increase in  $V_{GS}$ , as shown in Figure 4b. The voltage where the transistor start conducting, roughly (SUN et al., 1986; TAUR, 2000; SCHRODER, 2006), is called the threshold voltage ( $V_{th}$ ). The transconductance, presented in the right hand axis, is defined as  $\frac{dI_{DS}}{dV_{GS}}$ , and represents how much current the transistor delivers for an increase in  $V_{GS}$ .

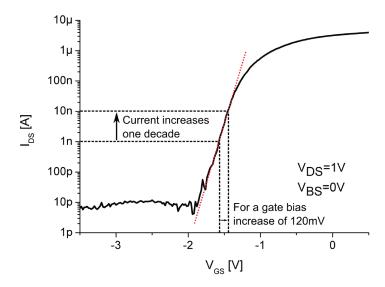

Below  $V_{th}$  the current is not zero, however. Figure 4c presents the same  $I_{DS}xV_{GS}$  discussed previously, but in logarithmic scale, such as to better evaluate the exponential

(a) Drain current response when increasing the drain bias, for different values of gate bias.

- (b) Drain current response and device transconductance when increasing the gate bias, for a small drain voltage.

- (c) Drain current response in the subthreshold region, showing the exponential current increase.

Figure 4 – MOSFET typical electrical response presented using FinFETs with 1 $\mu$ m gate length and 10nm fin width.

current increase in the subthreshold region. An increase in  $V_{\rm GS}$  from negative values to the threshold voltage induces a sharp increase in  $I_{\rm DS}$ , dominated by the diffusion current. Two important transistor figures of merit can be extracted from this graph, the subthreshold slope and the  $I_{\rm ON}/I_{\rm OFF}$  ratio. The first indicates how much  $V_{\rm GS}$  needs to increase to induce a tenfold increase in  $I_{\rm DS}$ , and is defined as

$$S \simeq \frac{kT}{q} ln \left( 10 \frac{C_{ox} + C_D + C_{it}}{C_{ox}} \right)$$

(1.1)

where  $C_D$  is the depletion capacitance,  $C_{it}$  the interface trap capacitance and  $C_{ox}$  the gate oxide capacitance. The minimal theoretical limit is 59.6 mV/decade at T=300K, where  $S = \frac{kT}{q} ln(10)$ , where the capacitance terms  $C_{it}$  and  $C_D$  approach zero (SZE; NG, 2006). The  $I_{ON}/I_{OFF}$  ratio indicates how much the drain current increases from the transistor off

state at zero gate bias to the on state at high  $V_{GS}$ . In the transistor presented in Figure 4c, the subthreshold slope is 60 mV/dec, what is called ideal, and the  $I_{ON}/I_{OFF}$  ratio is  $10^5$ , the current increases five orders of magnitude from the off state to the on state.

# 1.3 FinFET Fabrication Overview and Related Challenges

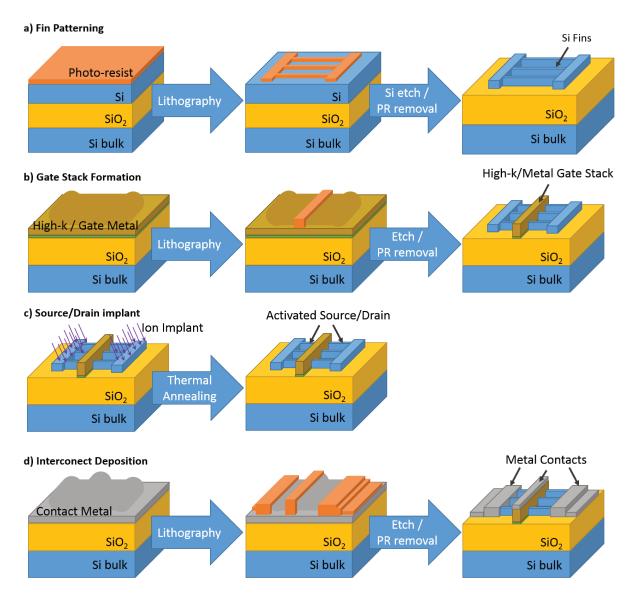

FinFET fabrication flow on SOI substrates can be divided in four simplified steps: fin patterning, gate stack formation, source and drain implant, and contacts and interconnect deposition, presented schematically in Figure 5.

Figure 5 – Simplified schematic of the FinFET fabrication flow, presenting the fin patterning (a), gate stack formation (b), source and drain implant (c) and interconnect deposition (d)

Fin patterning (Figure 5a) consist in the definition of the active area, the fins and source/drain pads, using a lithographic method that achieves small enough dimensions.

The silicon layer is then etched and the photo-resist or other masking material is removed, leaving the silicon fins exposed for the next step. Gate stack formation (Figure 5b) can be achieved by high- $\kappa$  dielectric deposition, followed by gate metal deposition, which is then lithographically defined and etched. Again, the lithographic method used, along with the etching techniques, has to be able to produce gate lengths of sub-50nm or less. Source and drain implantation (Figure 5c), along with thermal annealing, creates the source and drain junctions, by incorporation and activation of impurity atoms in the silicon lattice. The final gate stack, with the correct materials, can be formed either before – known as gate first scheme – of after – gate last scheme – source and drain implantations, according to process design decisions (FRANK, 2011; VELOSO et al., 2011). Contact and interconnect deposition (Figure 5d) is usually the last step of device fabrication, where the contact metal is deposited, patterned and etched. Contact deposition allows the device to be accessed to be tested or connected to other devices, creating a circuit.

The presented fabrication steps are obviously simplified, since modern CMOS fabrication involves additional steps such as gate sidewall spacer formation, silicides, complex gate stacks, engineered junction profiles and others (CHAU et al., 2007; HARELAND et al., 2013). Also, FinFETs fabricated on bulk silicon substrates require further additional steps, such as ion implants to avoid junction punchthrough and creation of shallow trench isolation (STI) (LINDERT; CEA, 2006).

Although FinFETs present simplified fabrication steps, compared to other multiple gate transistor designs—such as planar and vertical double-gate transistors (NOWAK et al., 2004)—, several challenges arise from the channel three dimensionality. The challenges are mainly related to sidewall smoothness after etching, ion implantation and uniform fin doping, conformal metal gate deposition and layout usage (KAWASAKI et al., 2009).

One of the most important structural parameter in a FinFET device – which is not present in planar MOSFETs – is the fin width  $(W_{\rm fin})$ . A very thin fin is desired, to ensure volume inversion, improve the electrical response and reduce short channel effects (DAL et al., 2007). Volume inversion is when the current flows in the center of the fins, not on the surface, reducing the mobility scattering effects and resulting in enhanced transistor performance, as first suggested by Balestra et al. (1987). It is only achieved, however, in fins thinner than 10nm (COLINGE et al., 2008), which imposes serious fabrication challenges not only to achieve this dimension, but to ensure uniformity and low roughness. Besides thin fins, multiple fin FinFET are also desired. Multiple fins improve FinFET electrical characteristics, for two important reasons: first, it provides better layout usage, and a wider channel for the same device, increasing the transistor drive current; second, it averages the fin characteristics, reducing random morphological variations that may compromise single fin transistors (SHANG et al., 2006). The fin definition is thus the first FinFET fabrication challenge, and special attention is required on the sidewall roughness,

which increases mobility scattering and degrades the device performance (CHOI et al., 2002a). Another issue is to guarantee that the metal gate fully envelops the fin, with proper step coverage and uniform thickness (JURCZAK et al., 2009).

Regarding fin doping, two main issues can be discussed: channel doping and source and drain doping. While planar MOSFETs require complex doping profiles to successfully suppress short channel effects, the supperior gate-to-channel coupling provided by Fin-FET devices allows the reduction of the channel doping (KING, 2005). An undoped channel provides higher carrier field effect mobility, increasing the transistor drive current. Random discrete doping variability is also significantly suppressed, when reducing the channel doping (WANG et al., 2011). For FinFETs with undoped channel, the threshold voltage ( $V_{\rm th}$ ) is controlled mainly by the gate electrode work function. Work function variations become thus the main source of  $V_{\rm th}$  variations between transistors in a circuit (MATSUKAWA et al., 2009).

The challenge of FinFET source and drain doping is related to uniformity and silicon amorphisation. An uniform doping of FinFET source and drain is more difficult to obtain due to fin shadowing, where one fin acts as a mask for the ion implant of the other (KAWASAKI et al., 2008). Also, the very thin silicon layer is prone to complete fin amorphisation during source and drain ion implant, which leads to problematic recrystallization during high temperature anneal. Boundary defects and possibly polycrystalline fins can result from complete amorphisation, contributing to increase the source and drain series resistance ( $R_{\rm SD}$ ) (DUFFY et al., 2007; COLLAERT et al., 2008). One way of preventing full amorphisation is to perform epitaxial regrowth of the thin fins – thus increasing the size of the silicon layer – before source and drain ion implantation, which also reduces significantly the source and drain series resistance ( $R_{\rm SD}$ ) (BASKER et al., 2010).

# 1.4 Objectives and Motivation

MOSFET prototype fabrication is an important part of the development cycle of new technologies and a basis for important discoveries in materials and devices. Transistor prototypes are mainly used to evaluate new materials and fabrication alternatives that can be integrated in the main process flow if successful. New materials or deposition methods for a given material should be assessed both regarding their morphological and electrical parameters. Due to its constraints on step coverage, sidewall roughness and work function stability, FinFET devices present themselves as excellent mediums for electrical characterisation of novel gate stack materials, for example. The fin has to be completely covered by both the dielectric and gate electrode, or else the device will not function properly. As such, the deposition method has to guarantee conformality, which can be assessed electrically using FinFET prototypes. Furthermore, a dielectric film which induces

a high density of charged interface states degrades the transistor carrier mobility and the subthreshold slope, parameters extracted from the electrical measurements. In summary, the evaluation of a given material or deposition method, in semiconductor research, has to go beyond morphological assessments, and as the industry has moved towards 3D devices, so are research labs required to.

This work is an effort to bring FinFET prototypes as a feasible testing tool for future developments in the Center for Semiconductor Components and Nanotechnologies (CCS Nano). When performing experimental research, one faces several challenges and drawbacks. This work is focused at critically analysing the issues and identifying their sources, in order to solve some and propose improvements and useful advice for future works related to prototype fabrication. Special attention is given to in depth evaluation of the results, both structural – such as cross sections with magnification close to the scanning electron microscope (SEM) resolution limit – and electrical – with careful parameter extraction and result discussion.

To fabricate the FinFET prototypes, results from other works, both from CCS Nano and elsewhere, have been put together, investigated and optimized to a certain degree. An effort towards process integration has been made, since the best results should be applied to new studies in order to achieve progress. Nonetheless, part of this work consists of new developments and new methods, since past solutions were not able to solve the issues raised in this research.

Prototype fabrication and transistor scaling depends on a full toolbox of methods, materials and equipments that are continually evolving, as was seen in Figure 1. With this thesis one more technique is expected to be added to the FinFET prototyping toolbox: the multiple fin definition using Ga<sup>+</sup> focused ion beam (FIB) lithography. This technique allows fast device prototyping using the focused ion beam (FIB), when compared to the most common technique of substrate milling using the same equipment. The flexibility regarding number of fins and fin width provided by Ga<sup>+</sup> FIB lithography is valuable for prototype fabrication, since it allows FinFETs with different fin characteristics to be fabricated side by side. In addition, transistor scaling is full of examples of techniques and tricks that were used for reasons beyond their original purpose. Spacer technology is an interesting case, first used in the gate sidewalls, allowing the fabrication of high performance lightly doped drain/source (LDD) MOSFETs (TSANG et al., 1982), was later used for sub-20nm line patterning and fin definition (DEGROOTE et al., 2007; XU et al., 2013), then called self-aligned double-patterning or spacer lithography. Likewise, techniques designed for FinFET prototyping could potentially be used for vertically integrated nanowire FETs or other applications even.

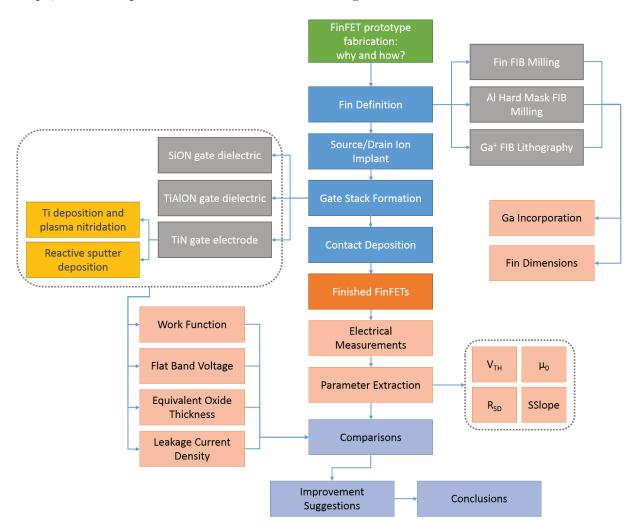

## 1.5 Thesis Structure

The schematic structure of the thesis is presented on Figure 6. The first block indicates the introduction, where the motivations, and basic knowledge of transistor operation and FinFET fabrication is presented. The work then follows to the specific fabrication steps, with in depth details on fin definition and gate stack formation alternatives.

Figure 6 – Schematic organization of the work and how this thesis will present it.

In this work three fin definition methods are studied: Fin FIB Milling, Al hard mask FIB milling and Ga<sup>+</sup> FIB lithography, with special attention to the latter two. Those methods are described in Section 2.1, along with other lithographic alternatives for FinFET fin definition. In the experimental procedure their parameters and initial results are presented. The fin definition methods are evaluated regarding the process induced gallium incorporation and obtained fin dimensions, in Chapter 4, in the morphological characterisations.

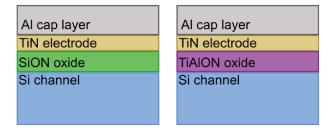

Different FinFET gate stack alternatives are also explored, including two dielectrics – SiON and TiAlON – and two different methods for TiN formation – e-beam titanium deposition followed by plasma surface treatment, and reactive sputter deposi-

tion. These materials and methods are discussed in the context of analogous results and applications, and gate stack alternatives used in modern CMOS by either the industry or other research institutes. The experimental formation of the different gate stacks in the fabricated FinFET prototypes and control capacitors is presented in Chapter 3, and the extracted parameters, results and comparisons are discussed in Section 4.2.

Following the FinFET fabrication, presented in the experimental procedure in Chapter 3, a complete device is obtained. Electrical characterisations is then performed and discussed along with its extracted parameters, such as R<sub>SD</sub>, V<sub>th</sub> and mobility, for example. The discussions and comparisons are tied with gate stack comparisons and lead to the conclusions. Improvement suggestions are made, based on the extracted parameters, electrical characterisations and evaluations of problems during prototype fabrication. It is not expected that this thesis solves all issues related to process integration and prototype fabrication, but that it provides useful advice for future improved devices. The final conclusions are thus drawn based on the fabrication experience and results achieved.

# 2 FinFET Fabrication Processes

Several fabrication steps are necessary for modern IC fabrication. In this section some of these fabrication steps will be covered, focusing on the key process for FinFET fabrication in special. The techniques employed in this work will be described in detail.

## 2.1 Fin Definition Methods

The vertical FinFET body – the fin – can be obtained using a variety of different techniques. The main issue is to define sub-100nm lines using the available lithographic equipment and methods. This section focuses on briefly outlining common lithography techniques for fin definition and discussing their advantages and difficulties.

## 2.1.1 Electron Beam Lithography

Electron beam lithography (EBL) is the method of choice for initial prototype fabrication, not only FinFETs, but other proof-of-concept devices and techniques as well. The first FinFETs fabricated employed e-beam lithography for fin definition and source and drain pads (HUANG et al., 1999; HISAMOTO et al., 2000).

Flexibility in pattern generation, since lithography is performed by direct writing, which eliminates the need of physical masks. Very fine lines below 10 nm can be achieved using e-beam lithography (GRIGORESCU et al., 2007; MANFRINATO et al., 2013). Electron forward scattering and backscattering leads to beam spread when electrons interact with the e-resist and even pattern size variations (CONSTANCIAS et al., 2013). This increases pattern roughness and results in line edge roughness which compromise smaller features (VIEU et al., 2000). For FinFET fabrication, it results in fins with uneven width, wich in turn degrades the output characteristics of the transistors. To reduce the effects of scattering upon the resist, that result in line width roughness and line edge roughness, very thin resists are employed. This, in turn, compromise future sample processing, since thicker resist layers are often needed for lift off and etch steps. Another option, is to separately adjust the exposure dose for each feature, accounting for proximity effects in order to properly define the features with minimal roughness (TSENG et al., 2003).

While electron beam lithography is very attractive for prototyping, mask and mold fabrication, and research and development (James Watt Nnanofabrication Centre, 2014), the low throughput makes this technique undesirable for high scale manufacturing. To address this issue, multiple beam tools are being developed to increase processing speeds

(CHANG et al., 2001), with different approaches being evaluated, such as the micro-column multiple e-beam (DU et al., 2016) and the reflective electron beam lithography (REBL) (MCCORD et al., 2012). While these systems are still in the development phase, interesting opportunities are expected for multiple beam systems in critical lithography steps (LIN, 2012).

#### 2.1.2 193nm Immersion Lithography

Big manufactures and research institutes use multi million dollars 193nm immersion lithography along with ashing and reactive ion etch (RIE) optimizations for fin definition. Some examples of fabricated FinFETs using this technique are demonstrated by IBM (KEDZIERSKI et al., 2003), IMEC (DAL et al., 2007), Intel (KAVALIEROS et al., 2006; AUTH, 2012; NATARAJAN et al., 2014) and TSMC (WU et al., 2010a). While the reported technology is 193nm immersion lithography, other methods are also frequently employed for the fin definition and other structures as well, such as double lithography double etch (LELE) and self aligned double patterning (MAENHOUDT et al., 2008) – herein called spacer lithography.

One way to obtain smaller structures using the same laser source is to replace the medium between the lenses and the wafer. When switching from air to a higher refraction index fluid, the system numerical apperture is increased, and thus the resolution and focal depth (SMITH et al., 2004b). Using water as an immersion fluid reduces the effective wavelength of 193nm radiation by 30% (SANDERS, 2010). Immersion lithography enables the patterning of sub-45nm features (SMITH et al., 2004a) and even sub-10nm when applied in conjunction with other techniques such as multiple patterning (OWA et al., 2014) and directed self assemby (JEONG et al., 2013).

Challenges remain, however, when immersion lithography is employed. The fluid has to be extremely homogeneous, free of bubbles and particles, that damage the final pattern (LIN, 2006). Moreover, scaling using 193nm immersion lithography can only achieve certain dimensions and remain viable. Beyond the 14nm technology node, extreme ultraviolet lithography (EUVL) provide important reduction of process complexity – and cost (RONSE et al., 2012).

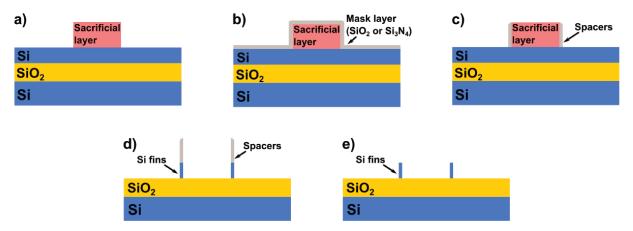

# 2.1.3 Spacer Lithography

Spacer lithography is often used for fin definition, since it provides reduction of the minimum features obtained by optical lithography (JUNG et al., 2006). Most nostably, FinFETs have been fabricated using spacer lithography and RIE for the silicon etch step (CHOI et al., 2001; CHOI et al., 2002b; DEGROOTE et al., 2007; KIM et al., 2013), and also using TMAH wet etch for highly anisotropic silicon etching (LIU et al., 2003;

JOVANOVI et al., 2010).

Spacer lithography, also called sidewall image transfer (STI) or self aligned double patterning (SADP) has been applied in NAND flash (BENCHER et al., 2008), due to the simple layouts, but also in SRAM fabrication (BASKER et al., 2010) and back end of the line (BENCHER et al., 2011). Beyond expanding the resolution limit, spacer lithography also reduces line width roughness.

The generic spacer fabrication flow is presented in Figure 7. A mandrel of sacrificial material is lithographycally defined. The mask layer is deposited by chemical vapour deposition (CVD) and subsequently plasma etched to leave thin spacers on the side of the sacrificial layer. This is then selectively removed, usually by wet etching, to leave the free-standing spacers. The final fins are obtained by etchin the silicon, using the spacers as etch masks, and then removing the spacers. We can see that the pattern density is doubled (one mandrel becomes two fins) and the final fin width is controlled solely by the thickness of the deposited film that forms the spacers. Since deposition thickness is more easily controlled than optical lithography line edge roughness, the resulting patterns present lower width variations. Structures with 15nm half pitch presenting line width roughness as low as 1.5nm and line edge roughness of 2.5nm have been reported for self assembled double patterning after process optimizations (XU et al., 2013).

Figure 7 – Schematic process for fin definition through spacer lithography

#### 2.1.4 Focused Ion Beam Techniques

Ion beam approaches for nanopatterning have gathered considerable attention in the last few years, with improved controllability and versatility (BAGLIN, 2012). When comparing to electron beam lithography, considerable advantages are observed due to the reduced lateral scattering, since ions are several order of magnitude heavier than electrons. Low line width roughness and line edge roughness are reported for ion beam lithography, especially when employing low mass ions such as helium (WINSTON et al., 2009; SCHOLDER et al., 2013; LUO et al., 2016).

Ion beam techniques for nanopatterning and nanofabrication are especially interesting due to its flexibility. By tailoring parameters such as ion mass and acceleration energy, a wide range of applications can be addressed (WATT et al., 2005). Focused ion beam for device fabrication has two main approaches: milling and lithography.

#### 2.1.4.1 FIB Fin Milling

Heavy ions such as Gallium are specially suited for patterned material sputtering, also known as milling. Several works have been performed using milling and ion-assisted material deposition for 3D transistor fabrication (POTT; IONESCU, 2006; LIMA et al., 2013; SANTOS et al., 2013; LIMA et al., 2015). Three dimensional fins can be obtained by defining and etching the transistor active region using conventional lithography and subsequently using the focused ion beam to remove the silicon on the channel until only a thin fin is left. Figure 8 schematically presents this process. An aluminium thin layer is used as the etching hard mask and left on the sample during the milling step to allow better contrast.

Figure 8 – Schematic process for FIB fin milling

This method presents some disadvantages, however. First, a single beam FIB system is inherently serial, which is, the transistors are fabricated one at a time. This limits the maximum number of devices that can be fabricated, due to time (and thus cost) constraints. Second, to obtain fins with sub-100nm width, very low beam currents have to be used. Lower beam currents result in lower sputtering yield, and thus the milling process requires very long time. Third, the focused Ga<sup>+</sup> beam, when interacting with the sample, not only sputter surface atoms, but also implant ions from the beam itself (VOLKERT et al., 2007). When using silicon substrates, this implanted gallium alters the doping levels, since Ga is an acceptor ion in silicon. Focused ion beam systems using hellium ions solve this last issue, and significant results have already been presented (WINSTON et al., 2009; SCHOLDER et al., 2013; LUO et al., 2016). In this work however, a Ga ion beam is used, which is relevant both for the Ga<sup>+</sup> FIB Lithography method and for the discussion regarding Ga incorporation in the samples.

#### 2.1.4.2 Al Hard Mask FIB Milling

In order to solve some of this issues, a new technique for fin definition using Ga<sup>+</sup> FIB milling is proposed in this work, where only a shallow milling is performed to remove

the aluminium hard mask on top of the transistor channel, leaving only a thin strip that becomes the fin after RIE. Since the milling depth is reduced, lower processing times are required to produce the same device, when comparing to the fin milling technique. The lower processing time also relates to lower Ga<sup>+</sup> implanted dose in the sample. The schematic process is presented in Figure 9.

Figure 9 – Schematic process for FIB Aluminium hard mask milling

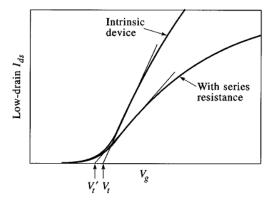

Although promising, this method assumes that the silicon just beneath the milled aluminium layer etches at the same rate – or near – as the bare silicon elsewhere on the sample. This was experimentally determined in this thesis as not being true, and in fact,  $Ga^+$  ion irradiation of silicon can lead to nanopillars as tall as 800nm when using fluorinated plasma etch chemistries such as  $C_4F_8/SF_6$  or  $SF_6/Ar$  (HENRY et al., 2010). This etch masking, in turn, can be used for the fin definition itself, and is the last method discussed.

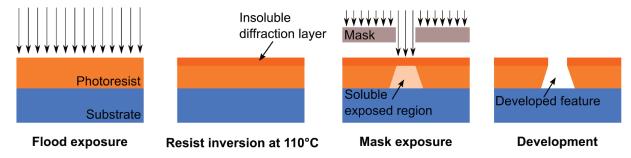

#### 2.1.4.3 Ga<sup>+</sup> FIB Lithography

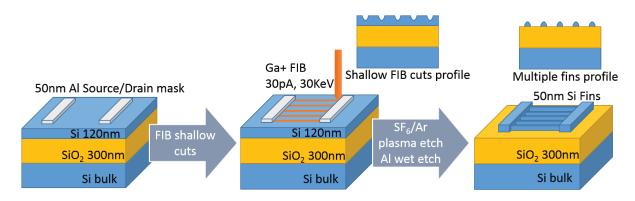

$\mathrm{Ga^{+}}$  ion irradiation os silicon can be adopted as a maskless and resistless lithography method for nanoscale multiple fin definition. While this technique has already been employed for micro electro-mechanical systems (MEMS) (CHEKUROV et al., 2010), in this work it is used for FinFET prototype fabrication for the first time. The  $\mathrm{Ga^{+}}$  FIB lithography relies on the formation of a thin non-volatile mask on the silicon regions irradiated by the  $\mathrm{Ga^{+}}$  ions, when exposed to a fluorinated plasma such as  $\mathrm{SF_{6}}$  and Ar. The time required for the multiple fin definition by combining the  $\mathrm{Ga^{+}}$  FIB lithography and  $\mathrm{SF_{6}/Ar}$  plasma etch techniques, is drastically reduced when compared to the traditional  $\mathrm{Ga^{+}}$  FIB milling.

The multiple fins are defined using surface modification through Ga+ shallow implant on silicon. Using a 30KeV focused ion beam, a 20nm layer of silicon is incorporated with Ga ions (VOLKERT et al., 2007). This incorporation is associated with material sputtering, and thus we call the process of patterned Ga implantation FIB shallow cuts. Figure 10 presents the schematic for the multiple fin definition. The Ga incorporated in the sample, in fluorinated plasma such as  $SF_6/Ar$ , creates a thin  $GaF_x$  non-volatile mask that protects the fins from etching (HENRY, 2010; HENRY et al., 2010).

Figure 10 – Schematic process for Ga<sup>+</sup> FIB lithography

When compared to other fin definition methods using the focused ion beam, the Ga<sup>+</sup> FIB lithography offers significant advantages. While the fabrication of a single fin using the Al hard mask milling process requires approximately 10 minutes, only 40 seconds are necessary to define nine parallel fins using ion beam lithography. It is still a serial process but the much reduced processing time allows increasing the number of fabricated FinFETs. The device gallium incorporation is also drastically reduced, as will be later discussed. An important disadvantage of the proposed method is the material sputtering related to the Ga<sup>+</sup> incorporation, which requires a thicker silicon layer than the desired fin height. It is shown, however, that the fin height can be controlled with adequate accuracy based on the FIB cut depth and silicon layer thickness.

# 2.2 Thin Film Deposition

Thin film deposition is an essential step of modern IC fabrication flow. A large variety of thin films is necessary to fabricate transistors nowadays, either metals, semiconductors or insulators. Deposited films have to follow strict requirements, such as uniform and controllable thickness and composition, low density of defects and imperfections, excellent adhesion, conformal step coverage and suitable electrical characteristics (WOLF; TAUBER, 1986). Several techniques are used for thin film deposition, owing to their advantages in different aspects needed in IC fabrication. This section will outline the main methods used for thin film formation and focus of the techniques employed in this work.

# 2.2.1 Atomic Layer Deposition

Although atomic layer deposition (ALD) was introduced in (SUNTOLA; ANTSON, 1977), the widespread adoption occurred when film conformality and precise thickness control became strict requirements. The transition from  $SiO_2$  gate dielectrics to high- $\kappa$  materials – that will be discussed in the next section – much increased ALD importance in the microelectronics industry (MISTRY et al., 2007). The FinFET design

has also been readily implemented partly due to the excellent conformal films provided by ALD (AUTH, 2012; JOHNSON et al., 2014). Furthermore, the main disadvantage ALD presents – the low deposition rate – has become less important as required film thickness have decreased and thickness control has in turn gained importance (LESKEL; RITALA, 2002).

The ALD process consists of sequential alternating pulses of vapour phase chemical precursors that react with the substrate. These individual gas-surface reactions are called "half-reactions" and appropriately make up only part of the materials synthesis. During each half-reaction, the precursor is inserted in the chamber reacts with to the substrate surface in a self-limiting manner, saturating the exposed surface and leaving no more than one monolayer. The first half reaction is purged and and the next chemical species are inserted, which react to the adsorbed monolayer and create a single layer of the desired material. ALD processes are performed at relatively low temperatures (<350°C), and the temperature range where the growth is saturated is called the "ALD temperature window" and depends on the utilized precursos (JOHNSON et al., 2014). Due to the self limiting nature, the films are highly uniform, conformal and continuous. Since each cycle deposits a single material layer, excellent thickness control is achieved (GEORGE, 2010). Several precursor gases have been developed to deposit a wide range of materials, including gate oxides, transition-metal nitrides for gate electrodes and metals for interconnections such as copper and ruthenium and even semiconductor materials (LESKEL; RITALA, 2003; GUO et al., 2015; MINJAUW et al., 2015; AHADI; CADIEN, 2016; SCHWARTZBERG; OLYNICK, 2015).

One of the limitations of ALD is related to film contamination arising from the non-reacted precursors incorporated in the film(LESKEL; RITALA, 2003; KIM, 2003; WU et al., 2010b), which can be controlled by changing the process temperature and improving the purge steps. Also, the materials that can be deposited are dependent on the available precursors. Furthermore, ALD depends on the chemisorption of the first pulse of precursors to the substrate surface, and for this active sites need to exist in this surface (PUURUNEN, 2005). For some chemistries employed, certain substrates require an additional step of surface preparation, prior to material deposition (POMAREDE et al., 2003).

## 2.2.2 Metal Evaporation

While evaporation has been phased out in the semiconductor industry, it still retains a degree of importance for research purposes (NISHI; DOERING, 2000). Evaporation tools are either thermal, with a tungsten filament heating the source material, or based on an electron beam (e-beam) as a heating source. In both cases the material to be deposited is heated above its boiling point and evaporates. When the vapour reaches the

sample it condenses and forms a continuous thin film. Electron beam evaporators reach higher temperatures, which allows the deposition of a wider range of materials. Furthermore, the source material is only melted in a small spot, where the electron beam is focused, reducing the contamination from the crucible that holds the material. Evaporation is performed at ultra high vacuum, which improves film purity and reduces gas phase scattering. Deposition of alloys is challenging, since different metals have different vapour pressures and thus their evaporation rate is also distinct. A multiple e-beam system can be used for this purpose, with adjusted beam energy to match the deposition rate of different materials (PLUMMER, 2009). The main disadvantage of e-beam evaporation is the poor step coverage, leading to non-conformal films. Perfect step coverage is specially important for 3D transistor fabrication, where the gate dielectric and gate electrode have to envelop the fin, in the case of FinFETs. Another serious concern regarding e-beam evaporation, is the radiation damage, originating from the highly excited electrons that arrive in the material being evaporated decaying back to the core levels (CAMPBELL, 2001). The x-rays can cause oxide traps that reduce MOSFET performance.

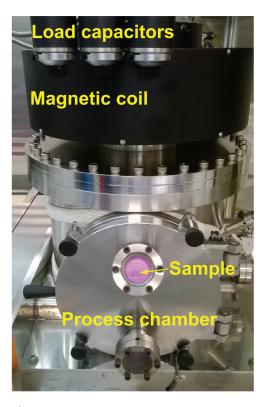

In this work e-beam evaporation is employed to deposit ultra thin films (few angstroms thick) of titanium and aluminium. The system reaches ultra high vacuum of 10<sup>-8</sup>Torr, which allows high deposition rate control, low contamination in the films, and low substrate damage resulting from high energy atoms. The evaporated metallic films are subsequently treated modified by plasma treatments, that will be discussed in a following subsection, to become either different compounds or even dielectrics.

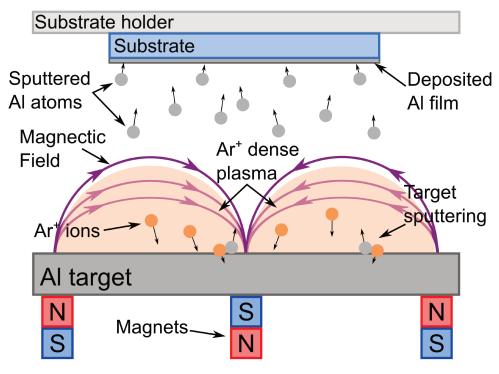

## 2.2.3 Sputter Deposition

Sputtering is a process in which ions are accelerated into a surface in order to remove atoms from that surface. Sputter deposition relies on the ejected atoms condensing on the desired substrate, forming a thin film. It is most widely used for metal deposition, but can also be employed for insulators (SIMON, 2012).

Argon is typically used as the bombardment species, which is accelerated to the target. Upon collision with the surface, atoms from the target ejected and travel with high kinetic energy to the substrate, condensing and forming the thin film. The impinging ions need sufficient energy – in the range of 50eV to 2KeV – in order to sputter target atoms, but at higher energies – 2KeV to 50KeV – the incident particle creates a cascade of collisions that breaks several atomic bonds and is not convenient for thin film deposition. Above 50KeV, ion implant is predominant and the sputter yield is significantly reduced (ROSSNAGEL, 2003).

The high kinetic energy of the sputtered atoms, when reaching the substrate surface is the main factor for the improvement in step coverage, when compared to evaporated films. The sputtered atoms have high surface mobility and can condense in smooth,

conformal and continuous films more easily than when evaporation is performed. The characteristic non-directionality of sputter deposition further improves film step coverage (ROSSNAGEL, 2003). Despite its advantadges, high energetic atoms can cause damage in thin films or sensible structures upon which the sputtered atoms are being deposited (LUJAN et al., 2002)